技术摘要:

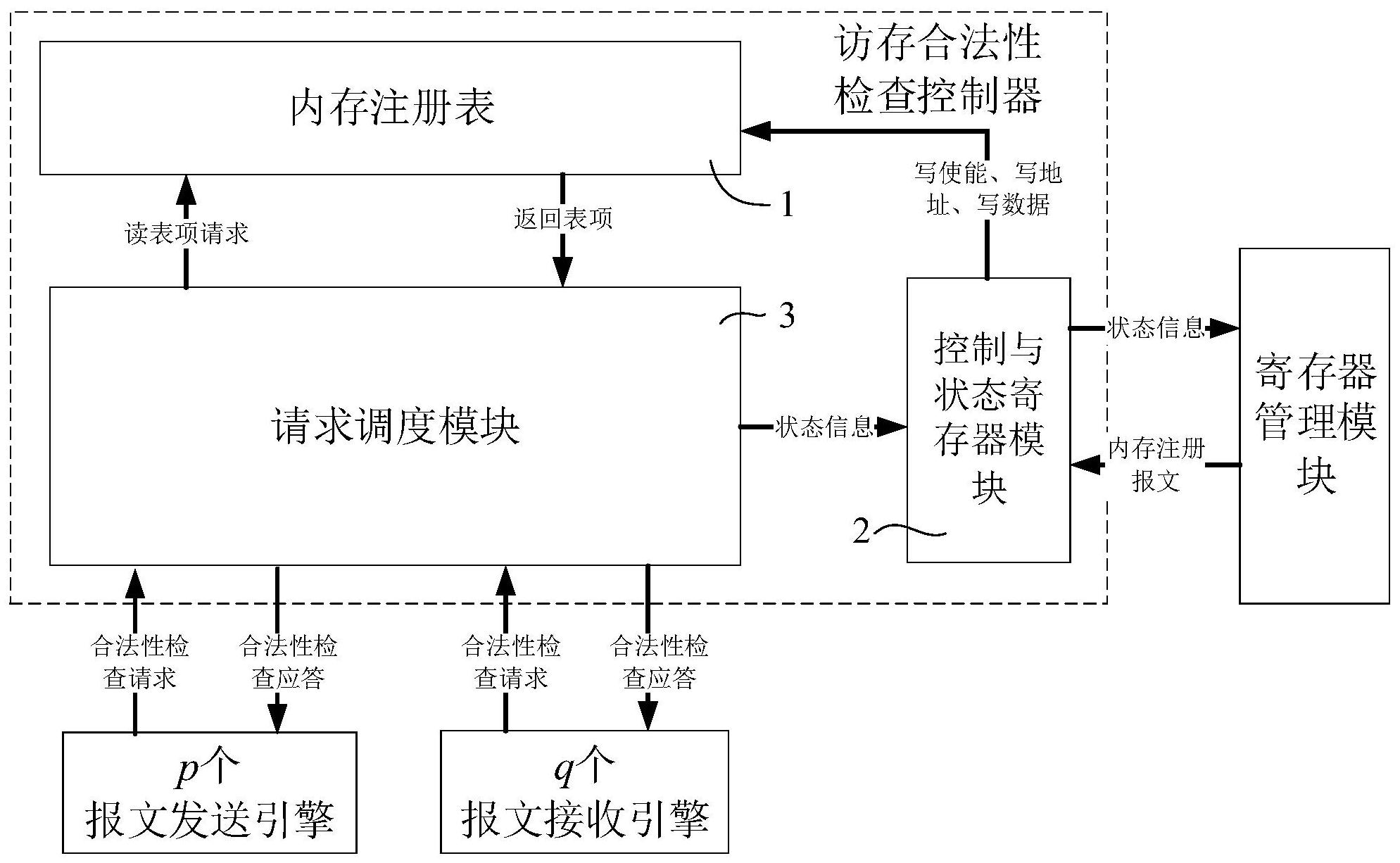

本发明公开了一种访存合法性检查控制器,芯片及设备,本发明的访存合法性检查控制器包括内存注册表、控制与状态寄存器模块、请求调度模块,请求调度模块包括请求栈存逻辑、仲裁请求生成逻辑、访存合法性检测逻辑与公平仲裁器,请求栈存逻辑分别与p个报文发送引擎及q个 全部

背景技术:

在高性能并行计算机与大规模数据中心中,成千上万个节点(微处理器或加速器) 之间的通信都是基于网络接口芯片与交换芯片的高速通信协议。为了解决网络传输中各个 节点数据处理的延迟,用户级的通信操作已经成为高速通信协议中主要采用的技术途径, 最常见的是远程内存直接访问(Remote Direct Memory Access,RDMA)技术,RDMA技术允许 用户态的应用程序直接读取或写入远程节点的内存,不需要内核干预以及内存拷贝的发 生。RDMA技术的主要思想是通过虚拟化通信硬件的资源,将其直接映射到用户进程地址空 间,实现完全用户层的通信操作,在通信的关键路径上旁路操作系统的介入,再结合硬件的 可靠性精简通信协议,减少内存拷贝操作,在用户进程缓冲区之间直接进行数据传输,从而 实现最优化的通信性能。因此,RDMA技术具备低延迟、高吞吐率、占用CPU资源少等优点。 由于在用户级直接实现了内存访问,绕开了操作系统对内存数据的保护,那么如 何保障内存数据的安全性将是RDMA技术的首要问题,因此RDMA中访存合法性检查技术成为 亟待解决的关键技术。目前,最常见的访存合法性检查技术是在软件驱动层面实现。采用软 件实现访存合法性检查技术的优点是灵活性强,不足之处是性能低、延迟大、占用带宽资 源,无法满足硬件大规模RDMA数据传输的需求。因此采用硬件实现访存合法性检查技术是 必然的趋势。

技术实现要素:

本发明要解决的技术问题:针对现有技术的上述问题,提供一种访存合法性检查 控制器,芯片及设备,本发明通过在网络接口芯片中实现访存合法性检查控制器(Memory Aceessing Validity Checker,MAVC),可扩展支持多个外部的请求源,能够在使用较少的 硬件资源的情况下,能够显著提高RDMA访存合法性检查的性能并大幅降低了延迟。 为了解决上述技术问题,本发明采用的技术方案为: 一种访存合法性检查控制器,包括内存注册表、控制与状态寄存器模块、请求调度 模块,所述控制与状态寄存器模块分别与内存注册表的控制端、请求调度模块的输出端以 及网络接口芯片的寄存器管理模块相连,所述请求调度模块包括请求栈存逻辑、仲裁请求 生成逻辑、访存合法性检测逻辑与公平仲裁器,所述请求栈存逻辑分别与p个报文发送引擎 及q个报文接收引擎相连,所述仲裁请求生成逻辑分别与请求栈存逻辑、访存合法性检测逻 辑、公平仲裁器相连,所述访存合法性检测逻辑与内存注册表相连。 可选地,所述内存注册表中存储的内存注册表项包含6个位域,每一项内存注册表 项的宽度是w位,所述6个位域分别为有效位、读位、写位、密钥、末页地址和首页地址。 可选地,所述内存注册表为随机访问存储器,且该随机访问存储器深度为d、宽度 4 CN 111600872 A 说 明 书 2/7 页 为w位,包含1个读端口和1个写端口;地址位的宽度为m位,且满足m=log2d。 可选地,所述控制与状态寄存器模块用于缓存内存注册报文、发送写入内存注册 表的控制信号、以及用于保存FIFO溢出以及访存不合法的地址信息以便寄存器管理模块读 取,所述控制与状态寄存器模块中包含用于保存内存注册报文的一组报文寄存器以及输出 寄存器,该组报文寄存器为w位且包括读写位、注册表地址、密钥、起始页地址、页面长度5个 位域,该输出寄存器用于保存FIFO溢出以及访存不合法的地址信息以便寄存器管理模块读 取。 可选地,所述请求栈存逻辑用于将p个报文发送引擎及q个报文接收引擎共计p q 个请求源的请求报文进行栈存后发送到请求到仲裁请求生成逻辑,以及当接收到仲裁请求 生成逻辑返回的应答信号后将合法性检查应答发送给对应的报文发送引擎或报文接收引 擎。 可选地,所述仲裁请求生成逻辑用于在接收到请求栈存逻辑发送的p q个请求报 文后产生p q位的仲裁请求发送到公平仲裁器,所述仲裁请求中的每一位对应一个请求源; 当接收到公平仲裁器返回的 位仲裁应答信号,所述仲裁应答信号表示对应的哪 一路请求源被授权,而后将授权的请求源的合法性检查报文发射到访存合法性检测逻辑; 当接收到访存合法性检测逻辑返回的检查应答信号后,根据p q位的授权信号将授权信号 为1那位的应答有效信号置为高电平,同时将应答信号返回请求栈存逻辑。 可选地,所述访存合法性检测逻辑用于在接收到仲裁请求生成逻辑发送的合法性 检查请求报文后取出第i j k m-1:i j k位作为读取内存注册表存储器的地址,同时将读 使能信号置为高电平,发送到内存注册表,其中i表示报文访问内存区域的页面长度,j表示 报文访问内存区域的起始页地址的宽度,k表示密钥的宽度,m表示地址位的宽度;当内存注 册表返回读出的数据后,进行如下的四项比对,第一项比对:取出内存注册表项的最高位, 即有效位是否为1;如果为1,表示当前内存区域已注册,内存检查请求合法;否则表示不合 法;第二项比对:根据合法性检查报文中作为读写位的最高位,如果最高位为1,表示对内存 区域是读操作,同时取出内存注册表项中作为读位的第2j k 1位,如果为1,表示内存区域 允许读操作,那么检查合法,如果为0,那么检查不合法;如果读写位为0,表示对内存区域是 写操作,取出内存注册表项的第2j k位,即写位,如果为1,表示内存区域允许写操作,那么 检查合法,如果为0,那么检查不合法;第三项比对:取出内存注册表项中作为密钥的第2j k-1:2j k位,与合法性检查报文的第i j k-1:i j位密钥进行比对;如果完全相同,表示内 存检查合法;如果存在不一致的位,表示内存检查不合法;第四项比对:取出合法性检查报 文的第i-1:0位页面长度域L,第i j-1:i位起始页地址As;取出内存注册表项的第2j-1:j位 末页地址Ah,第j-1:0位首页地址Al;判断是否满足公式:Al≤(As L)≤Ah,如果满足公式,那 么内存检查合法,如果不满足公式,那么内存检查不合法;如果上面四项比对全部通过,表 示内存检查报文合法,那么将应答有效位置1,同时将1位的检查结果置1,返回给仲裁请求 生成逻辑;如果上面四项比对至少有一项没有通过,表示内存检查报文不合法,那将应答有 效位置1,同时将1位的检查结果置0,返回给仲裁请求生成逻辑。 可选地,所述公平仲裁器用于接收到仲裁请求生成逻辑发送的p q位仲裁请求信 号后通过公平的轮转调度策略从中选出第r个授权、将r编码为二进制,产生 位的 5 CN 111600872 A 说 明 书 3/7 页 仲裁应答信号,发送给仲裁请求生成逻辑。 此外,本实施例还提供一种网络接口芯片,包括芯片本体,所述芯片本体中设有p 个报文发送引擎、q个报文接收引擎以及寄存器管理模块,所述芯片本体中还设有所述的访 存合法性检查控制器。 此外,本实施例还提供一种网络设备,该网络设备包含网络接口芯片,所述网络接 口芯片的芯片本体中设有p个报文发送引擎、q个报文接收引擎以及寄存器管理模块,其特 征在于,所述芯片本体中还设有所述的访存合法性检查控制器。 和现有技术相比,本发明具有下述优点:本发明通过在网络接口芯片中实现访存 合法性检查控制器,该访存合法性检查控制器包括内存注册表、控制与状态寄存器模块、请 求调度模块,控制与状态寄存器模块分别与内存注册表的控制端、请求调度模块的输出端 以及网络接口芯片的寄存器管理模块相连,请求调度模块包括请求栈存逻辑、仲裁请求生 成逻辑、访存合法性检测逻辑与公平仲裁器,请求栈存逻辑分别与p个报文发送引擎及q个 报文接收引擎相连,仲裁请求生成逻辑分别与请求栈存逻辑、访存合法性检测逻辑、公平仲 裁器相连,访存合法性检测逻辑与内存注册表相连,可扩展支持多个外部的请求源,能够在 使用较少的硬件资源的情况下,能够显著提高RDMA访存合法性检查的性能并大幅降低了延 迟。 附图说明 图1是本发明实施例中访存合法性检查控制器及其的逻辑结构及接口示意图。 图2是本发明实施例中请求调度模块的逻辑结构示意图。 图3是本发明实施例中访存合法性请求报文的格式。 图4是本发明实施例中内存注册表项的格式。