技术摘要:

本发明公开了一种变频器的控制方法和系统、计算机存储介质及处理器。其中,变频器包括:主控制器和至少一个第一微处理器;其中,该方法包括:主控制器生成变频器的控制信息,并通过至少一个高速通信接口发送至至少一个第一微处理器;至少一个第一微处理器基于控制信息 全部

背景技术:

磁悬浮大功率变频器用于磁悬浮离心冷水机组上,用于进行电机驱动。该变频器 在硬件拓扑上采用四象限变频技术,四象限变频在整流端和逆变端均采用全控整流拓扑。 对应I-U(电流-电压)曲线,变频器可以工作在四个象限内,因此称作四象限变频器。 由于整流和逆变为全控整流拓扑,所以在两端均需要控制器提供驱动信号,进而 驱动全控器件IGBT(Insulated Gate Bipolar Transistor,绝缘栅双极型晶体管)。因此, 如图1所示,在四象限变频器中需要一块PFC(Power Factor Correction,功率因素校正)控 制板,一块电机控制板和一块继电器控制板,其中,PFC板用于控制整流,电机控制板用于控 制逆变,继电器控制板用于执行变频器控制逻辑。如图2所示,各个控制器间的通信通常为 CAN(Controller Area Network,控制器局域网络)通信或光纤通信。但是,由于通信速率有 限,很难满足板间的数据的及时传输,造成了变频器的控制协同性不足;而光纤通信则有缺 少通信协议,成本高等缺点,不适宜大量使用。 针对上述的问题,目前尚未提出有效的解决方案。

技术实现要素:

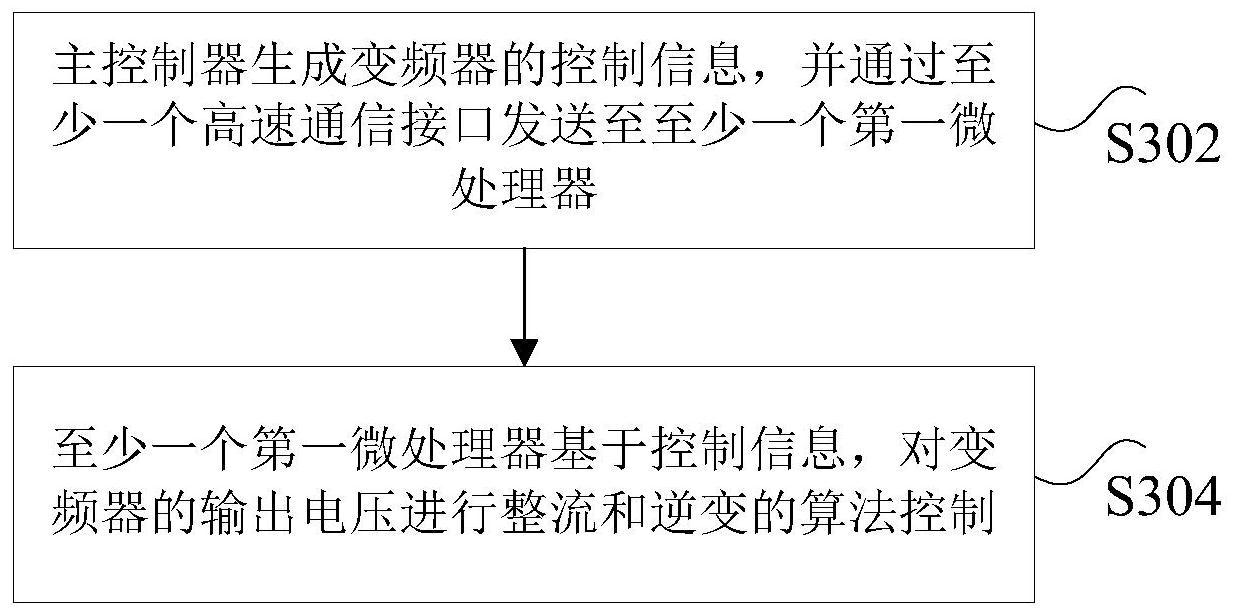

本发明实施例提供了一种变频器的控制方法和系统、计算机存储介质及处理器, 以至少解决相关技术中变频器的控制协调性不足,导致大功率变频器运行效果差的技术问 题。 根据本发明实施例的一个方面,提供了一种变频器的控制方法,变频器包括:主控 制器和至少一个第一微处理器;其中,该方法包括:主控制器生成变频器的控制信息,并通 过至少一个高速通信接口发送至至少一个第一微处理器;至少一个第一微处理器基于控制 信息,对变频器的输出电压进行整流和逆变的算法控制。 可选地,变频器还包括:开关电源板,其中,该方法还包括:通过开关电源板为主控 制器和第一微处理器进行供电,并触发主控制器和第一微处理器上电;在确定每个第一微 处理器完成初始化的情况下,主控制器与每个第一微处理器建立通信关系。 可选地,触发主控制器和第一微处理器上电包括:获取主控制器和第一微处理器 的电压等级;按照电压等级的顺序,控制主控制器和第一微处理器上的电源使能信号,以触 发主控制器和第一微处理器上电。 可选地,开关电源板至少由两部分电压源提供电能,主控制器基于变频器的母线 电压控制开关电源板使用不同的电压源进行供电,其中,在电压源包括三相输入端供电和 母线电压供电的情况下,当母线电压低于预设电压时,采用三相输入端供电,当母线电压高 于预设电压时,采用母线电压供电。 5 CN 111614268 A 说 明 书 2/15 页 可选地,至少一个第一微处理器基于控制信息,对变频器的输出电压进行整流和 逆变的算法控制包括:至少一个第一微处理器基于控制信息对电压环和电流环进行整流控 制,调制输出第一驱动信号,并经由主控制器内部的逻辑互锁,输出到主控制器后级的驱动 电路;至少一个第一微处理器基于控制信息对电机进行开环逆变调制,在允许进行模拟数 据采集时,切入闭环逆变调制,调制输出第二驱动信号,并经由主控制器内部的逻辑互锁, 输出到驱动电路。 可选地,在接收到第一驱动信号和第二驱动信号之后,主控制器通过比较接收到 的驱动信号,禁止输出同为高电平的驱动信号,并通过检测驱动信号的死区时间,确定是否 允许电平翻转。 可选地,该方法还包括:主控制器通过至少一个高速通信接口接收至少一个第一 微处理器发送的采样请求;主控制器通过采样控制接口控制外部采样芯片进行数据采样, 并接收外部采样芯片反馈的采样数据;主控制器通过至少一个高速通信接口发送采样数据 至至少一个第一微处理器,并将采样数据存储至第一外部存储器中。 可选地,在接收外部采样芯片反馈的采样数据之后,该方法还包括:将采样数据与 采样数据对应的设定数据进行比较;基于比较结果对主控制器后级的驱动电路进行输出保 护控制。 可选地,采样数据包括:多路模拟信号,其中,在主控制器将采样数据与采样数据 对应的设定数据进行比较之前,该方法还包括:主控制器将多路模拟信号划分为至少一个 信号集合,其中,每个信号集合中的至少一路模拟信号的类型相同,且具有相同的保护值; 通过采样电路对每个信号集合中的至少一路模拟信号进行处理,得到目标模拟信号;将目 标模拟信号与目标模拟信号对应的设定模拟信号进行比较。 可选地,变频器还包括:第二微处理器,其中,该方法还包括:在完成初始化,且与 上位机建立以太网通信连接之后,第二微处理器向主控制器进行数据交互,并将返回的信 息通过网络通信传递给上位机。 可选地,第二微处理器与上位机建立以太网通信连接之后,该方法还包括:第二微 处理器将上位机发送的传输数据发送至第一微处理器;第一微处理器对传输数据进行缓 存,并将缓存的传输数据转存到第二外部存储器中。 可选地,在接收到上位机发送的烧录指令之后,第一微处理器对传输数据进行解 析和校验,在校验成功的情况下,将传输数据进行缓存。 可选地,主控制器为不同的微处理器之间提供通信通路,其中,不同的微处理器使 用通信通路进行直接的信息交互。 可选地,该方法还包括:主控制器获取变频器的多个检测参数;主控制器对多个检 测参数进行并行处理,并基于每个检测参数与预先设定的故障参数的比较结果,确定变频 器是否存在故障;当变频器发生故障时,主控制器阻断内部的控制单元输出交互数据,并存 储故障信息,其中,控制单元用于生成控制信息,控制信息包括如下至少之一:状态控制信 息、上电控制信息、故障保护控制信息、模拟采样控制信息、采样保护控制信息、通信控制信 息、存储控制信息和检测控制信息。 可选地,当变频器的母线电压达到设定阈值时,控制主控制器的故障检测功能处 于使能状态,如果检测到变频器发生故障,则返回到待机启动状态。 6 CN 111614268 A 说 明 书 3/15 页 可选地,该方法还包括:通过数据选择器获取第三外部存储器或第四外部存储器 中存储的配置信息;基于配置信息对主控制器进行配置。 根据本发明实施例的另一方面,还提供了一种变频器的控制系统,包括:主控制 器,包括:至少一个高速通信接口,主控制器用于生成变频器的控制信息;至少一个第一微 处理器,与至少一个高速通信接口连接,第一微处理器用于基于控制信息,对变频器的输出 电压进行整流和逆变的算法控制。 可选地,该系统还包括:开关电源板,用于为主控制器和第一微处理器进行供电, 并触发主控制器和第一微处理器上电;主控制器还用于在确定每个第一微处理器完成初始 化的情况下,与每个第一微处理器建立通信关系。 可选地,开关电源板至少由两部分电压源提供电能,电压源包括:三相输入端供电 和母线电压供电,其中,主控制器用于基于母线电压来控制开关电源板使用不同的电压源 进行供电。 可选地,该系统还包括:外部采样芯片,用于采集采样数据;第一外部存储器,用于 存储采样数据;至少一个高速通信接口还用于接收至少一个第一微处理器发送的采样请 求;主控制器还包括:采样控制接口,与外部采样芯片连接,用于控制外部采样芯片以及接 收采样数据;第一存储控制模块,与第一外部存储器连接,用于将接收到的采样数据存储至 第一外部存储器。 可选地,该系统还包括:上位机,用于发送传输数据;主控制器包括:双端口随机存 储器,第二微处理器,与上位机建立以太网通信连接,与主控制器内部的双端口随机存储器 连接,用于向主控制器进行数据交互,并将返回的信息通过网络通信传递给上位机。 可选地,该系统还包括:第二外部存储器,用于存储传输数据;第一微处理器包括: 缓存模块,用于缓存经由第二微处理器转发的传输数据;第二存储控制模块,与缓存模块和 第二外部存储器连接,用于将缓存的传输数据转存到第二外部存储器中。 根据本发明实施例的另一方面,还提供了一种计算机存储介质,计算机存储介质 包括存储的程序,其中,在程序运行时控制计算机存储介质所在设备执行上述的变频器的 控制方法。 根据本发明实施例的另一方面,还提供了一种处理器,处理器用于运行程序,其 中,程序运行时执行上述的变频器的控制方法。 在本发明实施例中,主控制器生成变频器的控制信息,并通过至少一个高速通信 接口发送至至少一个第一微处理器,至少一个第一微处理器在接收到控制信息之后,可以 对变频器的输出电压进行整流和逆变的算法控制,从而实现大功率变频器的控制目的。由 于变频器包括主控制器和至少一个第一微处理器,并且主控制器和第一微处理器之间通过 高速通信接口进行数据交互,从而提高变频器整流和逆变端的数据交互量,便于进行算法 的优化,达到了提升大功率变频器的运行控制的协同性的技术效果,进而解决了相关技术 中变频器的控制协调性不足,导致大功率变频器运行效果差的技术问题。 附图说明 此处所说明的附图用来提供对本发明的进一步理解,构成本申请的一部分,本发 明的示意性实施例及其说明用于解释本发明,并不构成对本发明的不当限定。在附图中: 7 CN 111614268 A 说 明 书 4/15 页 图1是根据现有技术的一种磁悬浮大功率变频器拓扑的示意图; 图2是根据现有技术的一种磁悬浮大功率变频器硬件的示意图; 图3是根据本发明实施例的一种变频器的控制方法的流程图; 图4a是根据本发明实施例的一种可选的FPGA与DSP之间“一对一”uPP高速通信连 接及数据流的示意图; 图4b是根据本发明实施例的一种可选的FPGA与DSP之间“一对二”uPP高速通信连 接及数据流的示意图; 图5是根据本发明实施例的一种可选的三处理器主控平台拓扑的示意图; 图6是根据本发明实施例的一种可选的开关电源板的供电切换逻辑的流程图; 图7是根据本发明实施例的一种可选的主控平台内部的上电时序控制的流程图; 图8是根据本发明实施例的一种可选的主控平台软、硬件双重驱动信号保护的示 意图; 图9是根据本发明实施例的一种可选的主控平台数据采样和输出保护的示意图; 图10a是根据本发明实施例的一种可选的正半周采样包络线电路的示意图; 图10b是根据本发明实施例的一种可选的负半周采样包络线电路的示意图; 图11是根据本发明实施例的一种可选的绝对值包络线采样电路输出波形的示意 图; 图12是根据本发明实施例的一种可选的FPGA模式切换及数据观测的示意图; 图13是根据本发明实施例的一种可选的DSP远程程序烧录的流程图; 图14是根据本发明实施例的一种可选的主控平台内部的故障保护控制的流程图; 图15是根据本发明实施例的一种可选的主控平台各处理器的功能分配的示意图; 图16是根据本发明实施例的一种可选的多核心处理架构工作时序的流程图;以及 图17是根据本发明实施例的一种变频器的控制系统的示意图。