技术摘要:

本发明公开了一种基于FPGA方块映射方式的90度实时图像旋转处理的方法,属于图像处理技术领域,包括建立图像旋转处理系统,对行缩放处理后的每帧图像做分块处理生成数个分块,对每一个分块进行旋转,解决了对多格式的实时视频流进行90度的旋转处理的技术问题,采用流水 全部

背景技术:

图像旋转是一种常用的的数字图像处理技术,目前已广泛地应用于军事、航空、医 学等方面。国外对图像旋转算法的研究可追溯至20世纪80年代。1980年Catmull和Smith在 硬件上用两步法实现了图像旋转,但是第一步变换中,丢失图像中的高频部分,图像质量下 降明显。Paeth和Tanaka在1986年提出了三步实现的办法,只需通过三次平移就可以完成图 像旋转处理,便于硬件实现,但是图像质量未得到很好的改善。 1996年,Kiern提出用快速傅里叶变换实现图像旋转的方法,不同于直接法、两步 法或三步法在完成坐标变换后需要进行图像插值,该方法将坐标变换与图像插值合二为 一,但是计算量庞大,不利于硬件。 随着FPGA技术的发展,FPGA已经对专业图像处理芯片构成很大的威胁。过去,FPGA 通常被用做协处理器。随着生产规模的提高,产品应用成本的下降,FPGA常被用于系统级的 设计之中。基于FPGA的图像处理系统可以充分利用FPGA高速、并行计算的特点,通过设计流 水线的方式提高数字图像的处理速度,以提高系统性能,满足大数据量、实时性的处理要 求。虽然当前用FPGA进行视频图像处理已经取得了很大的进展,但是仍有很多待解决的问 题,比如高实时性要求、大分辨率图像处理、复杂图像处理算法的硬件实现等。

技术实现要素:

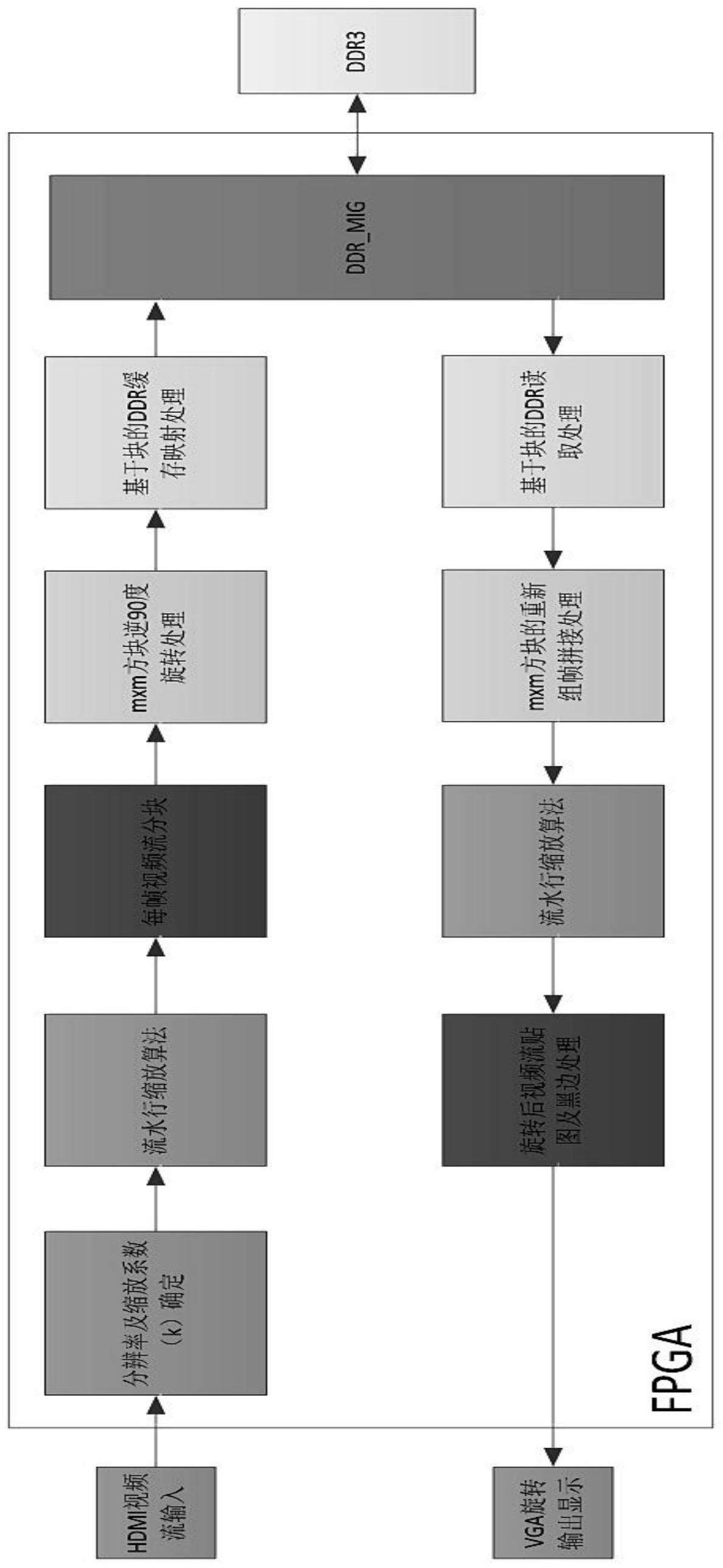

本发明的目的是提供一种基于FPGA方块映射方式的90度实时图像旋转处理的方 法,解决了对多格式的实时视频流进行90度的旋转处理的技术问题。 为实现上述目的,本发明采用以下技术方案: 一种基于FPGA方块映射方式的90度实时图像旋转处理的方法,如下步骤: 步骤1:建立图像旋转处理系统,图像旋转处理系统包括视频流输入接口、FPGA模 块、DDR存储器和VGA输出接口,视频流输入接口与FPGA模块连接,用于为FPGA模块提供HDMI 视频流数据,DDR储存器与FPGA模块连接,用于为FPGA提供数据存储区,VGA输出接口与输出 FPGA模块转换后的VGA图像数据; 步骤2:视频流数据从视频流输入接口输入后,被传送到FPGA模块中,FPGA模块实 时判断视频流数据的分辨率,依据分辨率大小确定旋转的行缩放系数k,行缩放系数k的计 算公式如下: k=Y÷X; 其中,X为一帧的行有效像素个数,Y为一帧的有效行个数; 步骤3:FPGA模块对视频流数据的每行像素做插值和抽取的操作,采用硬件优化的 最近邻插值法,且以流水线的方式进行计算,重组缩放后的每一行视频流数据; 4 CN 111583122 A 说 明 书 2/4 页 步骤4:对行缩放处理后的每帧图像做分块处理生成数个分块,设定所述分块表示 为MB,MB的大小为m×m,m为像素值,m的取值由DDR存储器的缓存带宽和突发读写长度所决 定; 设定进过分块处理后,每帧图像被分成了L×L个MB,L为正整数; 步骤5:采用FPGA的流水线处理流程,对每个MB做旋转90度的处理,其处理公式如 下: Cow_Data_t[n1][((3-m1)×16 15):((3-m1)×16)]=Row_Data_t[m1][(n1×16 15):(n1×16); 其中m1和n1的取值均为4,Row_Data_t[ ]为缓存了一个MB的二维数组,Cow_Data_t [ ]为90度旋转后输出的一个MB的二维数组; 步骤6:FPGA模块将步骤5中做过旋转的所有MB全部放入DDR储存器进行存储,MB的 地址范围为:{AX1(0~L),AY1(0~L)},设定每个MB对应一个映射地址(AX,AY); DDR储存器的地址映射做如下转换:AX=AX1,AY=L-AX1; DDR储存器的写地址映射公式为:WR_ADDR={AY,AX}; 步骤7:FPGA模块根据以下DDR储存器的读地址映射公式,从DDR储存器中逐个读取 一帧图像当中的所有MB: RD_ADDR={BY,BX},其中BX的取值为0~L,BY的取值为0~L; 步骤8:FPGA模块将经过步骤7读取的所有MB重新组成新的一帧图像,此时的图像 已经为旋转后的状态,即旋转后图像; 步骤9:FPGA模块根据步骤2的方法,对旋转后图像进行缩放处理; 步骤10:将步骤9得到的结果贴入视频格式生成时序中,未填充部分做黑化处理, 生成最终图像,并通过VGA输出接口进行输出。 优选的,在执行步骤3时,采用FPGA的乒乓处理方法,使缩放和行重组工作相互独 立。 优选的,在执行步骤6和步骤7时,WR_ADDR={AY,AX}为一个写二维地址映射数组, 其中AY和AX为地址,WR_ADDR则为AY和AX的地址下的数据; RD_ADDR={BY,BX}为一个读二维地址映射数组,其中BY和BX为地址,RD_ADDR则为 BY和BX的地址下的数据。 优选的,所述DDR储存器为DDR3存储器。 本发明所述的一种基于FPGA方块映射方式的90度实时图像旋转处理的方法,解决 了对多格式的实时视频流进行90度的旋转处理的技术问题,采用流水线及乓的FPGA的设计 思想,有效提升了旋转的处理速度,采用方块旋转并突发读写DDR的设计流程,有效提升单 片DDR读写的效率,可只对一片DDR3同时做双通道并行操作,提高DDR带宽利用率,减少PCB 布线面积,只需要一片DDR3即可做一路旋转和一路不旋转或者两路都旋转的操作。 附图说明 图1是本发明的数据流向图; 图2是本发明的行像素缩放处理及帧分块示意图; 图3是本发明的未旋转MB的示意图; 5 CN 111583122 A 说 明 书 3/4 页 图4是本发明的旋转后MB的示意图。