技术摘要:

本公开内容的实施方式总的来说涉及硬掩模膜和用于沉积硬掩模膜的方法。更具体而言,本公开内容的实施方式总的来说涉及碳化钨硬掩模膜和用于沉积碳化钨硬掩模膜的工艺。在一个实施方式中,提供了形成碳化钨膜的方法。所述方法包括:在第一沉积速率下,在基板的含硅表面 全部

背景技术:

集成电路已演变成复杂的装置,其可在单个芯片上包括数百万个晶体管、电容器 及电阻器。芯片设计的演变持续涉及更快的电路以及更高的电路密度。对具有更高的电路 密度的更快速的电路的需求增强了对用于制造此种集成电路的材料的相应需求。具体而 言,当集成电路部件的尺寸缩小至次微米量级时,低电阻导电材料以及低介电常数绝缘材 料被用来从此种部件获得适当的电气性能。 对于更高的集成电路密度的需求也产生了对于用在集成电路部件的制造中的工 艺序列的需求。举例而言,在使用常规光刻技术的工艺序列中,可在设置在基板上的材料层 的堆叠之上形成能量敏感抗蚀剂层。能量敏感抗蚀剂层暴露于图案的影像,以形成光抗蚀 剂掩模。其后,使用蚀刻工艺将掩模图案转移至堆叠的材料层中的一个或多个。选择蚀刻工 艺中使用的化学蚀刻剂,使得具有比对能量敏感抗蚀剂的掩模的蚀刻选择性要大的对堆叠 的材料层的蚀刻选择性。即,化学蚀刻剂会以比蚀刻能量敏感抗蚀剂快得多的速率来蚀刻 材料堆叠的一个或多个层。堆叠的一个或多个材料层相对于抗蚀剂的蚀刻选择性避免能量 敏感抗蚀剂在完成图案转移之前被消耗。因此,高选择性蚀刻剂提升准确的图案转移。 随着图案尺寸缩小,能量敏感抗蚀剂的厚度也相应地缩小,以便控制图案分辨率。 由于化学蚀刻剂的侵蚀,这样薄的抗蚀剂层可能不足以在图案转移过程中遮盖下方材料 层。因为对化学蚀刻剂具有更大的抵抗力,通常在能量敏感抗蚀剂层与下方材料层之间使 用称为硬掩模的中间层(如,氧氮化硅、碳化硅或碳膜),以促进图案转移。目标是具有高蚀 刻选择性和高沉积速率的硬掩模材料。随着临界尺寸(CD)缩减,现有的硬掩模材料缺乏相 对于下方材料的目标蚀刻选择性,且通常难以沉积。 因此,本领域中需要改进的硬掩模层及用于沉积改进的硬掩模层的方法。

技术实现要素:

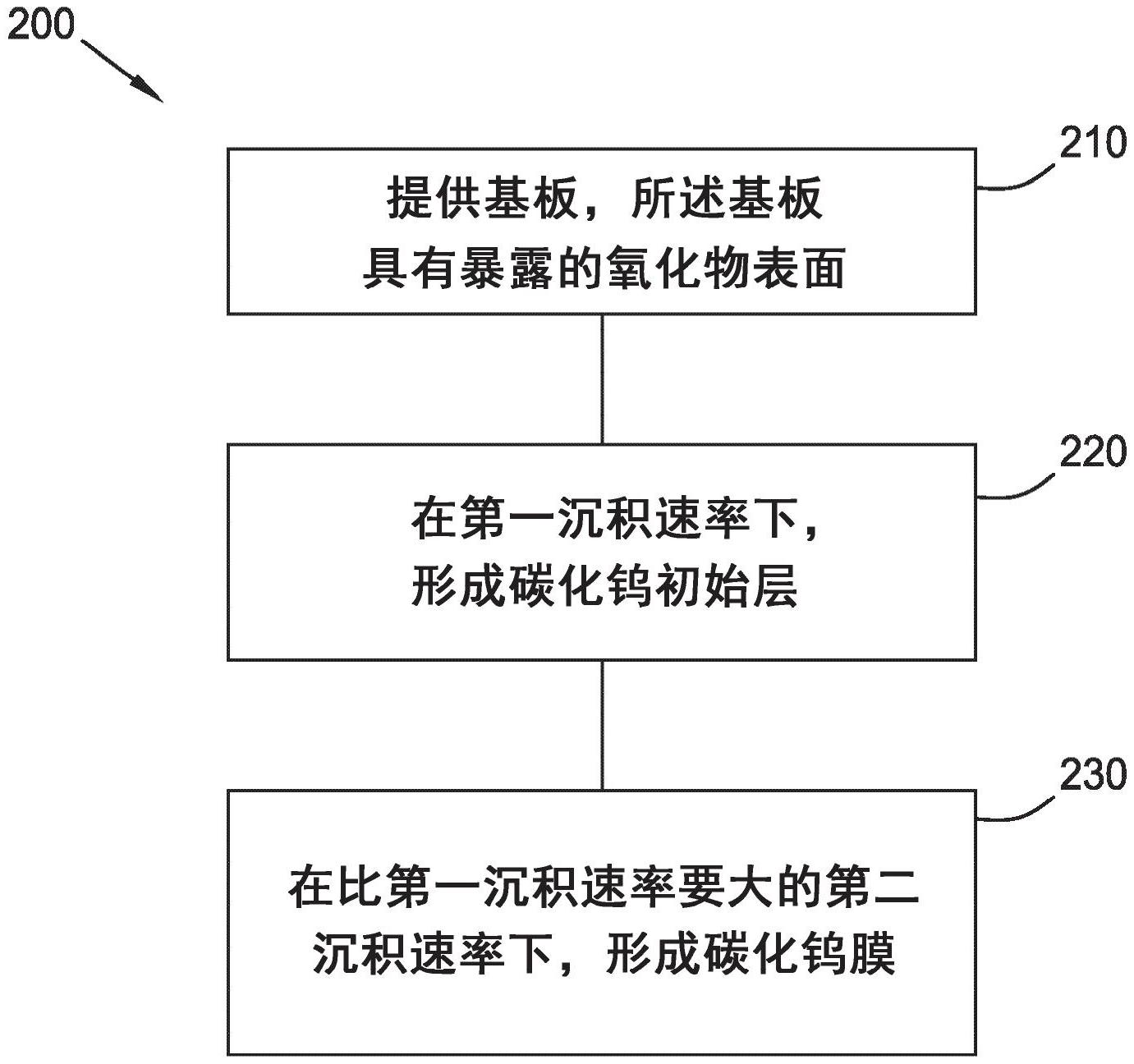

本公开内容的实施方式总的来说涉及硬掩模膜和用于沉积硬掩模膜的方法。更具 体而言,本公开内容的实施方式总的来说涉及碳化钨硬掩模膜和用于沉积碳化钨硬掩模膜 的工艺。在一个实施方式中,提供了形成碳化钨膜的方法。所述方法包括:在第一沉积速率 下,在基板的含硅表面上形成碳化钨初始层。所述方法进一步包括:在第二沉积速率下,在 碳化钨初始层上形成碳化钨膜,其中第二沉积速率大于第一沉积速率。 在另一个实施方式中,提供了形成碳化钨膜的方法。所述方法包括:在第一沉积速 率下,在基板的含硅表面上形成碳化钨初始层,包括:在第一PECVD工艺中,将含硅表面暴露 于包括WF6、C3H6及可选地H2的第一反应性气体,第一PECVD工艺包括处于约2托(Torr)至约 4 CN 111602224 A 说 明 书 2/8 页 10托的范围内的第一压力下的约100瓦或更小的第一RF等离子体功率。所述方法进一步包 括:在第二沉积速率下,在碳化钨初始层上形成碳化钨膜,包括:在第二PECVD工艺中,将碳 化钨初始层暴露于包括WF6、C3H6及H2的第二反应性气体,第二PECVD工艺包括处在约2托至 约10托的范围内的第二压力下的约500瓦或更大的第二RF等离子体功率。所述第二沉积速 率大于所述第一沉积速率。 在又一实施方式中,提供了形成碳化钨膜的方法。所述方法包括:在第一沉积速率 下,在基板的含硅表面上形成碳化钨初始层,包括:在第一PECVD工艺中,将含硅表面暴露于 包括WF6、C3H6及可选地H2的第一反应性气体,第一PECVD工艺包括处在约2托至约10托的范 围内的第一压力下的约100瓦或更小的第一RF等离子体功率。所述方法进一步包括:在第二 沉积速率下,在碳化钨初始层上形成碳化钨膜,包括:在第二PECVD工艺中,将碳化钨初始层 暴露于包括WF6、C3H6及H2的第二反应性气体,第二PECVD工艺包括处在约2托至约10托的范 围内的第二压力下的约500瓦或更大的第二RF等离子体功率。第二沉积速率大于第一沉积 速率。碳化钨初始层具有在约 至约 的范围内的厚度。碳化钨膜具有大于约 或更大的厚度。 附图说明 可通过参考实施方式来详细理解本公开内容的上述特征,公开内容的上述特征简 短地在前面概述过,其中所述实施方式中的一些实施方式在附图中示出。然而,应注意的 是,附图仅示出此公开内容的典型实施方式,并且因此附图不应被视为对此公开内容的范 围的限制,因为本公开内容可允许其他等效的实施方式。 图1描绘可用于实践本文所述的实施方式的PECVD系统的剖面示意图; 图2描绘根据本公开内容的一个实施方式的用在设置于基板上的膜堆叠上形成碳 化钨硬掩模层的方法的流程图;以及 图3A至图3C描绘根据图2中所示的实施方式的用在形成于基板上的膜堆叠上形成 钨硬掩模层的序列的一个实施方式。 为了促进理解,已尽可能使用相同的元件符号来表示附图共有的相同元件。可预 期一个实施方式的元件和特征可以有利地并入其它实施方式中,而无需进一步叙述。