技术摘要:

本发明实施例提供了一种半导体器件及形成方法。在本发明实施例中,通过去除所述外延结构上方的介质层,以露出所述外延结构和所述外延结构两侧的金属栅极的侧壁;并形成覆盖所述金属栅极侧壁的侧墙;形成覆盖所述外延结构的金属层;形成覆盖所述金属层的隔离层;在所述 全部

背景技术:

随着半导体制造工艺的不断发展,半导体器件的集成度越来越高,半导体器件的 特征尺寸也逐渐缩小。然而,半导体器件的可靠性还需要提高。

技术实现要素:

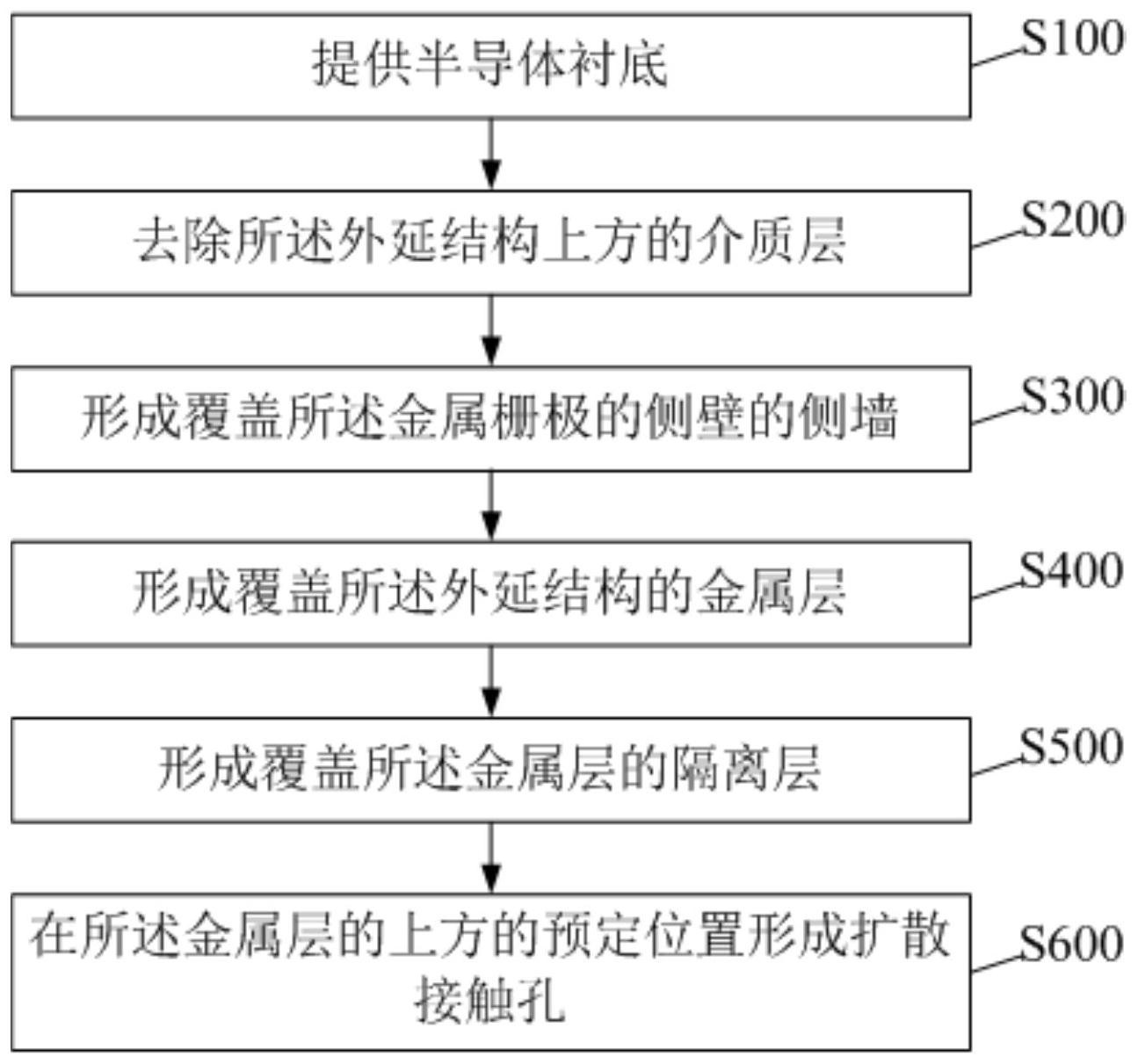

有鉴于此,本发明实施例提供了一种半导体器件及形成方法,能够提高半导体器 件的可靠性。所述方法包括: 提供半导体衬底,所述半导体衬底上形成多个金属栅极、位于所述金属栅极之间 的外延结构和覆盖所述金属栅极和所述外延结构的介质层; 去除所述外延结构上方的介质层,露出所述外延结构和所述外延结构两侧的所述 金属栅极的侧壁; 形成覆盖所述金属栅极的侧壁的侧墙; 形成覆盖所述外延结构的金属层; 形成覆盖所述金属层的隔离层; 在所述金属层的上方的预定位置形成扩散接触孔。 进一步地,所述去除所述外延结构上方的介质层,包括: 采用宽度大于所述金属栅极之间的距离的掩膜图案刻蚀所述外延结构上方的介 质层。 进一步地,所述金属栅极上方具有保护层,在所述隔离层的预定位置形成接触孔 的同时,所述方法还包括: 在所述金属栅极上方的预定位置形成栅极接触孔。 进一步地,所述在所述金属栅极上方的预定位置形成栅极接触孔,包括: 刻蚀所述保护层的预定位置,以形成露出金属栅极的第一通孔; 在所述第一通孔中沉积导电材料。 进一步地,所述在所述金属层上方的预定位置形成扩散接触孔,包括: 刻蚀所述隔离层的预定位置,以形成露出金属层的第二通孔; 在所述第二通孔中沉积导电材料。 进一步地,同时在所述第一通孔和第二通孔中沉积金属。 进一步地,所述形成覆盖所述外延结构的金属层,包括: 在所述外延结构上方沉积金属层; 采用化学机械研磨工艺研磨所述介质层、金属层和侧墙直至露出所述保护层; 回刻蚀所述金属层。 进一步地,所述形成覆盖所述金属层的隔离层,包括: 4 CN 111613573 A 说 明 书 2/9 页 沉积隔离层; 采用化学机械研磨工艺研磨所述隔离层,以使所述隔离层的上表面与所述介质层 的上表面平齐。 进一步地,所述侧墙的材料与所述隔离层的材料相同。 进一步地,所述侧墙和所述隔离层的材料为碳化硅或碳氧化硅。 另一方面,本发明实施例提供一种半导体器件,所述半导体器件包括: 半导体衬底,所述半导体衬底上形成多个金属栅极和位于所述金属栅极之间的外 延结构; 保护层,所述保护层覆盖所述金属栅极的顶部; 金属层,所述金属层与所述外延结构电连接; 侧墙,所述侧墙覆盖所述金属层的侧壁,以使得所述金属层和所述金属栅极电隔 离; 隔离层,所述隔离层覆盖所述金属层的顶部; 扩散接触孔,所述扩散接触孔形成在所述金属层的上方的预定位置。 进一步地,所述半导体器件还包括: 栅极接触孔,所述栅极接触孔形成在金属栅极上方的预定位置。 在本发明实施例中,通过去除所述外延结构上方的介质层,以露出所述外延结构 和所述外延结构两侧的金属栅极的侧壁;并形成覆盖所述金属栅极侧壁的侧墙;形成覆盖 所述外延结构的金属层;形成覆盖所述金属层的隔离层;在所述金属层的上方的预定位置 形成扩散接触孔。能够确保金属栅极和金属层之间电绝缘,避免金属栅极和金属层相互短 路,确保半导体器件的可靠性。 附图说明 通过以下参照附图对本发明实施例的描述,本发明的上述以及其它目的、特征和 优点将更为清楚,在附图中: 图1-图5是对比例的半导体器件的形成方法的各步骤形成的剖面示意图; 图6是本发明实施例的半导体器件的形成方法的流程图; 图7-图18是本发明实施例的半导体器件的形成方法的各步骤形成的结构的示意 图; 图19-图21是本发明实施例的半导体器件的示意图。