技术摘要:

本申请涉及用于准确信号生成的反馈控制。锁相环(PLL)通过进入保持模式(418)并在保持模式下将反馈时钟(fbclk)与第二参考时钟对准,从而执行从第一参考时钟(ref1)到第二参考时钟(ref2)的无中断切换。通过调节用于多模式分频器(128)的除数输入(D)来执行对准,多模式分频器 全部

背景技术:

PLL被广泛用于电子电路中的时钟生成,尤其是在设置时钟频率和其他电参数时 需要灵活性的情况下。图1示出了示例性PLL 120,该PLL 120从由包括压电晶体114和温度 补偿放大器电路116的晶体振荡器电路110提供的参考时钟信号refclk生成时钟信号 PLLout。将输出PLLout反馈到PLL中用于与refclk进行比较,以校正PLLout生成中的任何相位/ 频率误差。另外,如果需要,反馈路径可以被用于倍频,以使PLLout频率为refclk频率的倍 数。 具体地,分频器128将PLLout频率除以某个除数N,该除数N可以是整数或分数。分频 器输出fbclk被提供给也接收refclk的相位/频率检测器(PFD)136。PFD生成表示refclk和 fbclk之间的相位/频率差的误差信号。误差信号由电荷泵(CP)140转换为电压Vctrl,该电 压Vctrl控制压控振荡器(VCO)150以生成PLLout信号,从而使refclk和fbclk之间的相位/频 率差最小化。值得注意的是,由于fbclk频率等于PLLout频率除以N,因此PLLout频率是refclk 的N倍。参见例如2007年4月10日授权的美国专利No.7,202,717,其通过引用并入本文。 将低通滤波器154插入在CP 140和VCO 150之间以提高PLLout稳定性。 PLL也可以使用数字电路系统。参见例如2015年2月3日授权的美国专利No.8,947, 139,其通过引用并入本文。 在各种应用(汽车是其中之一)中,需要冗余参考时钟来提高系统的可靠性/安全 性。图2中示出了一个示例,其中两个晶体振荡器110.1、110.2被多路复用以向PLL 120提供 refclk。更具体地,振荡器110.1、110.2生成相应的时钟ref1、ref2。多路复用器210基于选 择信号214来选择这些时钟之一,并将所选择的时钟提供给PLL的refclk输入。如果两个振 荡器110之一发生故障,则选择信号214选择另一个振荡器。参见例如1992年6月16日授权给 Sato的美国专利No.5,122,677,其通过参考并入本文。 如果两个振荡器110的输出是相位对准的,则振荡器切换可以是无中断的,即具有 PLLout和refclk的最小中断/停机时间。但是,即使同时启用振荡器110,振荡器110也常常不 是同相的。这是因为它们的晶体114通常被略微不同地切割,并且由于其他不匹配(布局不 匹配、在裸片的不同部分中的位置等)。在两个晶体之间的相位未知/任意的情况下,从一个 振荡器110切换到另一个振荡器110将给PLL引入相位偏移,这可能会干扰下游信号,从而可 能导致电子器件崩溃。特别地,PLL 120可能失去锁定并停止起作用。 根据上面引用的Sato专利,振荡器110的输出在被提供给MUX210之前可以通过附 加电路系统(未示出)进行相位对准。始终保持相位对准,因此时钟切换是无中断的。

技术实现要素:

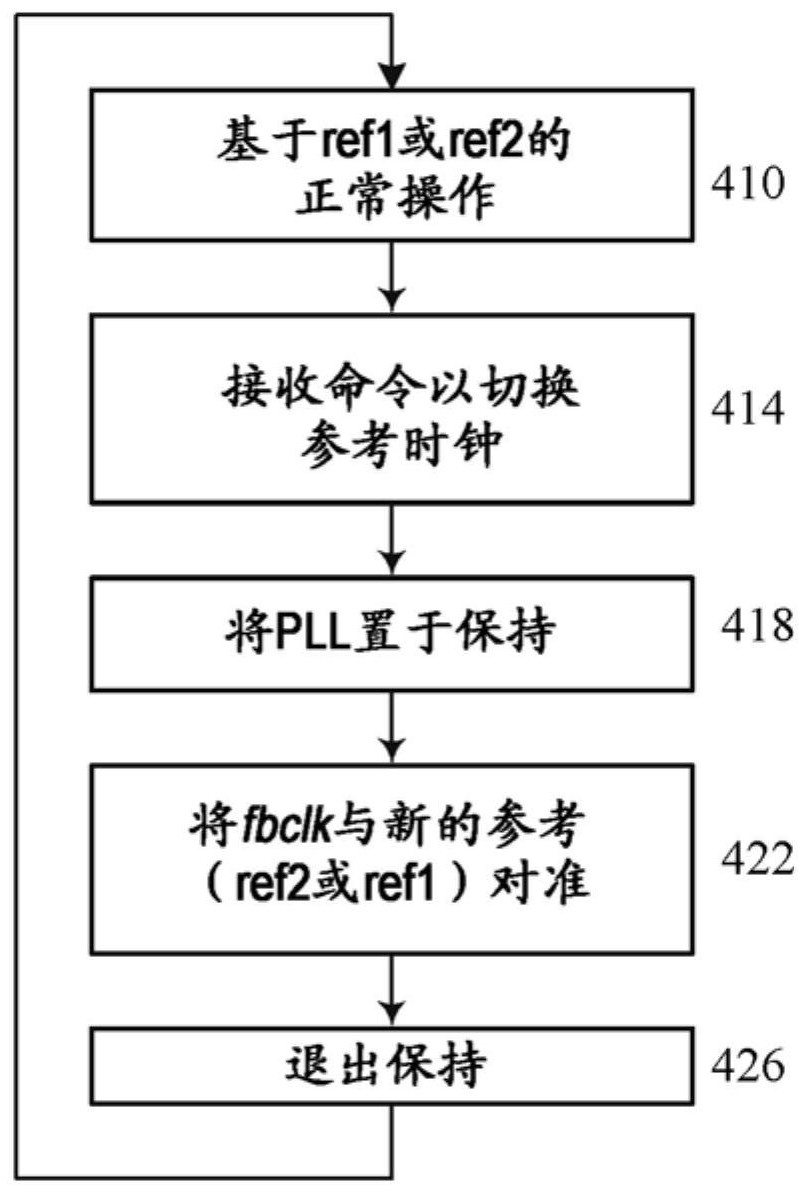

该部分总结了本发明的一些特征。其他特征可以在后续部分中进行描述。本发明 5 CN 111600601 A 说 明 书 2/7 页 由所附权利要求限定,所附权利要求通过引用被并入到本部分中。 本发明的一些实施例促进了无中断或接近无中断的参考时钟切换,而不管参考时 钟是否一直被对准。例如,假设PLL需要从ref1(即振荡器110.1)切换到ref2。首先,将PLL置 于保持模式,在该模式中,输出PLLout与振荡器110解耦并保持在恒定频率。分频器128被替 换为多模式分频器,并且在保持期间,分频器的输入N(除数)在反馈环路中被进行了调整, 以使fbclk与新的参考ref2对准。在已经达到对准时,保持模式结束,并且PLL根据ref2进行 操作。在一些实施例中,由于在保持模式下执行对准而减少了PLL干扰。 此外,在一些实施例中,时钟ref1和ref2可以具有不同的频率。另外,取决于 refclk是ref1还是ref2,除数N可以具有不同的值。 本发明的一些PLL实施例可以与其他技术例如在Sato专利中描述的技术相结合。 除了由所附权利要求限定以外,本发明不限于上述特征或优点。 附图说明 图1和图2是根据现有技术的时钟发生器的框图。 图3是根据本发明一些实施例的时钟发生器的框图。 图4是根据本发明一些实施例的时钟发生器操作的流程图。 图5是图示出根据本发明一些实施例的保持模式操作的时序图。 图6、图7、图8图示出了根据本发明一些实施例的时钟发生器电路。 图9是根据现有技术的时钟发生器的时间/频率图。 图10是根据本发明一些实施例的时钟发生器的时间/频率图。