技术摘要:

本发明的一种基于物联网的污水处理监控系统,传输延时计算模块采用除法器得出传输延时信号,之后经压控振荡器转换为频率信号后输出到变频比较模块,与原有的传输延时对应的时钟频率信号进入频率差电路,计算出频率偏差量并转为0‑5V电压,进入双比较器比较,控制时钟补 全部

背景技术:

污水处理工艺复杂(不同领域的污水采取不同的工艺,例如城市污水处理工艺包 括物化调节池、氧化池、还原池、沉淀、生化调节池、水解酸钠池、缺氧池、纳滤装置、NF产水 池、反渗透装置、污泥池、压滤机等工艺),分布范围比较大,水中污染物质的浓度和分布是 随着时间、空间、气象条件及污染源排放情况等因素的变化而不断改变的,为有效监控各个 工艺环节的数据、准确控制污水处理,目前常采用基于物联网的污水处理监控系统实现在 线实时监控; 具体为距离近的或每个工艺环节所处区域为一个子系统,子系统中由相应传感器 检测现场污水处理设备运行状态信息和污水处理设备信息,有线或无线的方式传送到PLC 控制器,PLC控制器通过物联网反馈到污水处理监控平台,对数据进行实时采集、调控,并可 对数据进行显示、记录,但由于传输到PLC控制器的数据以及PLC控制器到污水处理监控平 台的数据由于网络速率不稳定,传输的延时不一,若PLC控制器、污水处理监控平台以接受 到的数据时间为采集时间,会造成采集数据的时间不准确,进而不能准确的监控所在时间 的反映的现场污水处理设备运行状态信息和污水处理设备信息的问题。 因此,本发明提供一种新的方案来解决此问题。

技术实现要素:

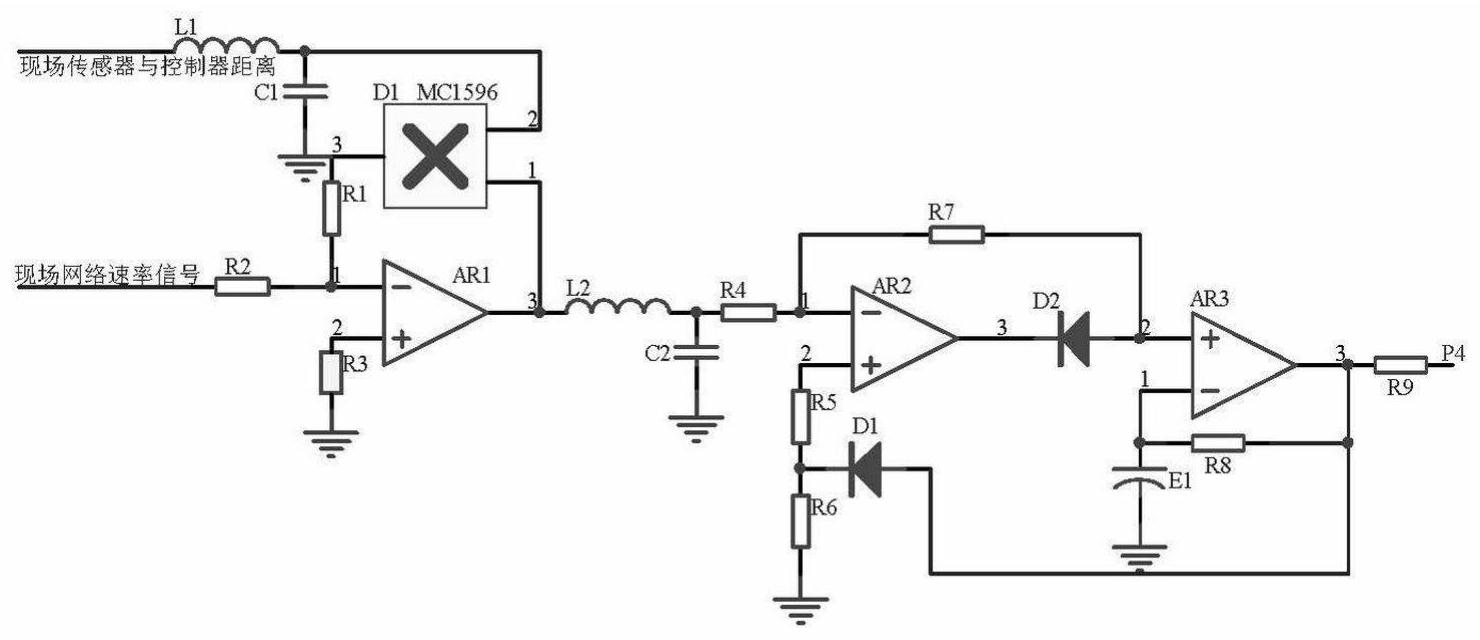

针对上述情况,为克服现有技术之缺陷,本发明之目的在于提供一种基于物联网 的污水处理监控系统,有效解决了PLC控制器、污水处理监控平台以接受到的数据时间为采 集时间,会造成不能准确的监控所在时间的反映的现场污水处理设备运行状态信息和污水 处理设备信息的问题。 其解决的技术方案是,包括数据采集时钟模块、PLC控制器、污水处理监控平台,其 特征在于,所述PLC控制器接收现场污水处理设备运行状态信息和污水处理设备信息,PLC 控制器采集的时间经数据采集时钟模块校正,PLC控制器在采集处理的数据上打上时间戳 后,再通过物联网传输到污水处理监控平台; 所述数据采集时钟模块包括传输延时计算模块、变频比较模块、时钟补偿模块、反 馈稳频模块。 优选的,所述传输延时计算模块通过采用除法器对检测现场污水处理设备运行状 态信息和污水处理设备信息的现场传感器与控制器距离信号与现场网络速率信号相除,得 出传输延时信号,之后经压控振荡器产生方波脉冲也即频率信号后输出; 所述变频比较模块接收传输延时计算模块输出的频率信号和原有的传输延时对 应的时钟频率信号,三极管Q1-Q4为核心的频率差电路,计算出频率偏差量并转为0-5V电 压,之后经环路滤波器稳压进入双比较器,高于 LH或低于 LL时输出高电平,否则输出低电 4 CN 111586159 A 说 明 书 2/6 页 平; 所述时钟补偿模块在变频比较模块输出低电平时,芯片IC1对原有的传输延时对 应的时钟频率信号锁相、反相器缓冲后进入PLC控制器,在变频比较模块输出高电平时,芯 片IC1对原有的传输延时对应的时钟频率信号经环路滤波器转换为直流电压,同时与变频 比较模块中环路滤波器稳压后电压耦合,经三极管Q9、三极管Q10稳压后进入芯片IC1,改变 震荡频率后,再经锁相、反相器缓冲后进入PLC控制器,PLC控制器内部通过计数器计算出校 正后的时延,并作为PLC控制器的系统时钟,在采集处理的数据上打上时间戳; 所述反馈稳频模块接收时钟补偿模块缓冲后信号,一路经环路滤波器后反馈到三 极管Q10的基极,稳定芯片IC1的震荡频率,另一路进入三极管Q8为核心的频率差电路,计算 出缓冲后信号和原有的传输延时对应的时钟频率信号的频率差,反馈到芯片IC1,起到锁 频、锁相的作用,芯片IC1以校正后震荡频率震荡。 本发明有益效果是:将实时检测的传输延时经转换为频率信号后与原有的传输延 时对应的时钟频率信号进入频率差电路,计算出频率偏差量并转为0-5V电压,转化为频率 信号分析处理,用以提高抗干扰能力,避免了模拟信号直接比较受杂讯信号干扰影响,进入 双比较器比较控制进行锁相、反相器缓冲后进入PLC控制器,或改变震荡频率后,再经锁相、 反相器缓冲后进入PLC控制器,PLC控制器内部通过计数器计算出校正后的时延,最后PLC控 制器根据接受传感器数据的时间减去延时时间作为采集数据的时间,并作为PLC控制器的 系统时钟,在采集处理的数据上打上时间戳,再通过物联网传输到污水处理监控平台,污水 处理监控平台根据时间戳,定义采集数据的时间,以此进行实时采集、调控,可准确的反映 所在时间的现场污水处理设备运行状态信息和污水处理设备信息。 附图说明 图1为本发明的传输延时计算模块电路原理图。 图2为本发明的变频比较模块电路原理图。 图3为本发明的时钟补偿模块电路原理图。 图4为本发明的反馈稳频模块电路原理图。