技术摘要:

用于使用神经网络生成输出示例的方法、系统和装置,包括编码在计算机存储介质上的计算机程序。方法之一包括,在每个生成时间步长处,使用回归神经网络并根据隐藏状态,处理包括序列中前一生成时间步长处的N比特输出值的第一回归输入,以生成第一分数分布;使用第一分数 全部

背景技术:

本说明书涉及使用神经网络生成输出示例。 神经网络是采用非线性单元的一个或多个层来预测接收到的输入的输出的机器 学习模型。一些神经网络除了输出层之外,还包括一个或多个隐藏层。每个隐藏层的输出被 用作网络中下一层的输入,即下一个隐藏层或输出层。网络的每个层根据相应的参数集的 当前值,从接收到的输入生成输出。 一些神经网络是回归神经网络。回归神经网络是接收输入序列并从输入序列生成 输出序列的神经网络。特别地,回归神经网络可以使用来自先前时间步长的网络的一些或 全部内部状态来计算当前时间步长的输出。 回归神经网络的示例是包括一个或多个LSTM存储器块的长短期记忆(Long Short-Term Memory,LSTM)神经网络。每个LSTM存储器块可以包括一个或多个单元,每个单 元包括输入门、遗忘门和输出门,其允许该单元存储该单元的先前状态,例如,用于生成当 前激活或要提供给LSTM神经网络的其他组件的状态。

技术实现要素:

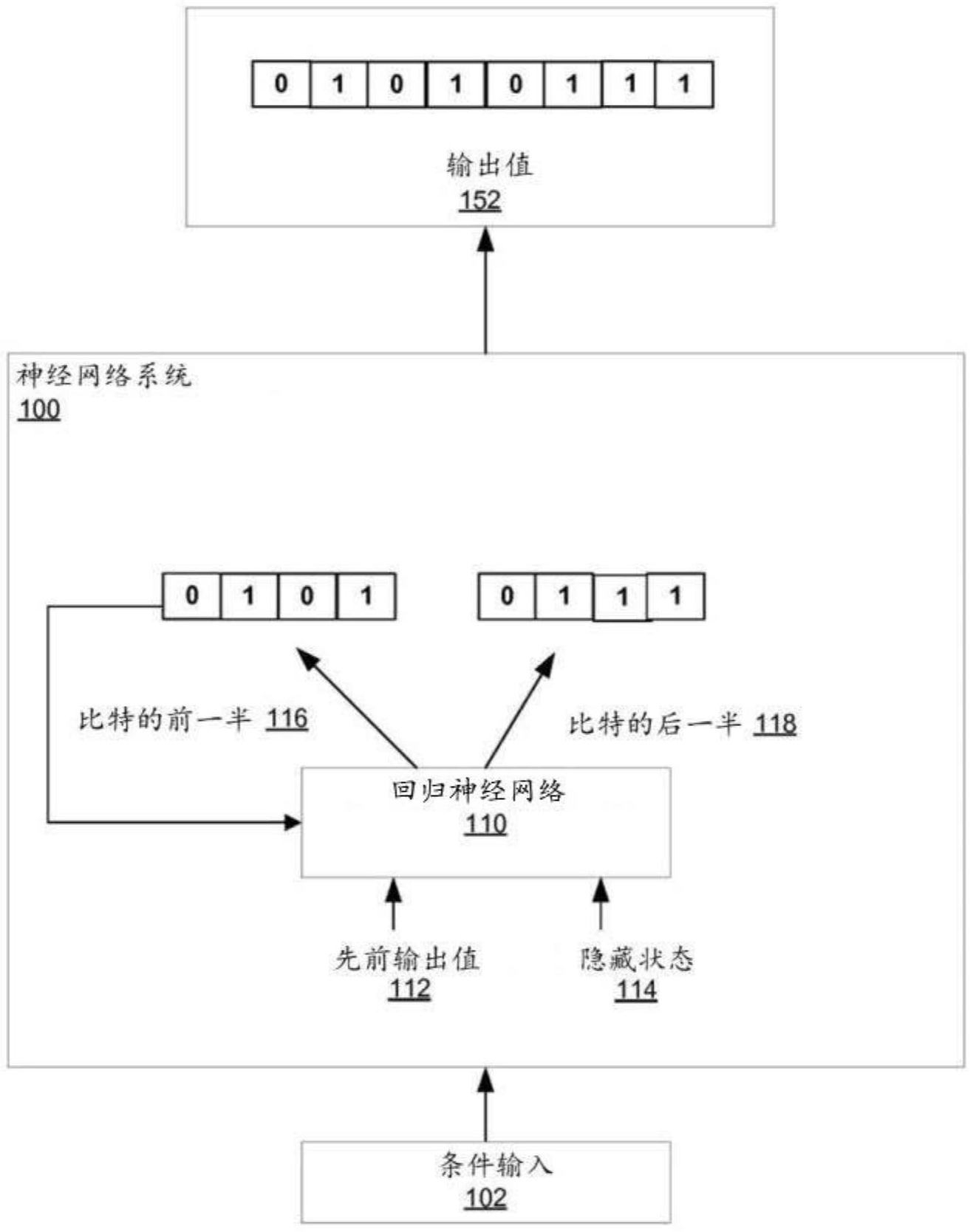

本说明书描述了在一个或多个位置的一个或多个计算机上实现为计算机程序的 系统,该系统通过在多个生成时间步长的每一个处生成相应的输出值,使用回归神经网络 生成输出示例。输出示例中的每个输出值都是N比特值。在每个生成时间步长,系统生成N个 比特的前一半的值,然后生成以N个比特的前一半的值为条件的N个比特的后一半的值。例 如,系统可以生成输出值的N/2个最高有效位的值,然后以已经生成的最高有效位的值为条 件生成输出值的N/2个最低有效位的值。 因此,在一个方面,提供了一种生成输出示例的方法,该输出示例包括在生成时间 步长序列的每个生成时间步长处的相应的N比特输出值。该方法可以包括,对于每个生成时 间步长,使用回归神经网络并根据回归神经网络的隐藏状态,处理包括序列中前一生成时 间步长处的N比特输出值的第一回归输入,以生成在生成时间步长处的输出值中的N个比特 的前一半的可能值上的第一分数分布,并且使用该第一分数分布选择输出值的N个比特的 前一半的值。该方法可以包括,对于每个生成时间步长,使用回归神经网络并根据相同的隐 藏状态,处理第二回归输入,该第二回归输入包括(i)序列中前一生成时间步长处的N比特 输出值,以及(ii)N个比特的前一半的值,以生成在生成时间步长处的输出值中N个比特的 后一半的可能值上的第二分数分布,并且使用该第二分数分布选择输出值的N个比特的后 一半的值。 如稍后进一步描述的,该方法的实现方式适于在具有有限计算能力和存储器带宽 的处理单元上实现,诸如在移动设备中找到的。例如,该方法的实现方式使用计算架构,其 中处理单元被配置为将生成N比特输出值分为两半,生成N个比特的前一半,然后生成N个比 特的后一半。通过以这种方式将输出空间划分为两个较小的输出空间而不是一个大的输出 空间,序列矩阵-向量乘积计算的数量可以减小一个数量级,促进该方法的实时实现方式。 5 CN 111587441 A 说 明 书 2/10 页 可选地,输出值可以在生成时间步长中的每一个处以相应的条件输入为条件。第 一回归输入和第二回归输入中的每一个还可以包括生成时间步长的条件输入。在生成时间 步长处生成条件输入可以包括使用条件神经网络来处理条件特征。 在实现方式中,处理第一回归输入可以包括处理第一回归输入以生成更新隐藏状 态的前一半,然后使用一个或多个第一输出层处理更新隐藏状态的前一半以生成第一分数 分布。处理第二回归输入可以包括处理第二回归输入以生成更新隐藏状态的后一半,以及 使用一个或多个第二输出层处理更新隐藏状态的后一半以生成第二分数分布。 在特定实现方式中,一个或多个第一输出层可以被配置为将第一权重矩阵应用于 更新隐藏状态的前一半,以生成第一投影更新隐藏状态。然后,该方法可以将元素方式 (element-wise)非线性激活函数应用于第一投影更新隐藏状态以生成第一激活向量,将第 二权重矩阵应用于第一激活向量以生成第一罗吉斯(logits),然后将softmax函数应用于 第一logits以生成第一分数分布。类似地,一个或多个第二输出层可以被配置为将第三权 重矩阵应用于更新隐藏状态的后一半,以生成第二投影更新隐藏状态。然后,该方法可以将 元素方式非线性激活函数应用于第二投影更新隐藏状态以生成第二激活向量,将第四权重 矩阵应用于第二激活向量以生成第二logits,并将softmax函数应用于第二logits以生成 第二分数分布。 回归神经网络可以包括一个或多个门。然后,处理第一回归输入可以包括通过将 回归权重矩阵应用于隐藏状态来确定每个门的相应回归贡献。然后,该方法还可以包括,对 于一个或多个门中的每一个,从第一回归输入确定门的第一输入贡献,从至少门的回归贡 献和门的第一输入贡献确定门的第一门向量,以及从第一门向量和隐藏状态生成更新隐藏 状态的前一半。类似地,处理第二回归输入可以包括,对于一个或多个门中的每一个,从第 二回归输入确定门的第二输入贡献,从至少门的回归贡献和门的第二输入贡献确定门的第 二门向量,以及从第二门向量和隐藏状态生成更新隐藏状态的后一半。 在实现方式中,处理第二回归输入可以包括生成更新隐藏状态的后一半,而无需 从第一回归输入的处理中重新计算门的回归贡献。 在实现方式中,回归神经网络仅包括单个回归层。应用于回归神经网络的先前状 态的单个回归层可以提供上下文的高度非线性变换,这由回归神经网络的隐藏状态以已经 压缩的形式表示。因此,这进一步促进了该方法在具有有限计算能力的处理单元上的部署。 在该方法的一些实现方式中,N个比特的前一半是最高有效位,而N个比特的后一 半是输出示例(数据项)的最低有效位。在一些实现方式中,可以通过分别从第一分数分布 和第二分数分布中采样来选择N个比特的前一半和后一半的值。 该方法的实现方式仅允许在生成输出示例的开始时,将回归神经网络的参数加载 到处理单元的寄存器中一次。然后,回归神经网络的参数可以在输出示例的生成的整个过 程中保持(persist)在寄存器中。这有助于减少实现该方法时使用的存储器带宽。 在一些实现方式中,该方法在诸如手机的移动设备的处理单元上操作。 在另一方面,提供了一种处理单元,其被配置为在生成时间步长序列的每个生成 时间步长处生成包括相应的N比特输出值的输出示例。处理单元被配置为将N比特输出值的 生成分为两半,以生成N个比特的前一半,然后生成N个比特的后一半。处理单元可以被配置 为,对于每个生成时间步长,使用回归神经网络并根据回归神经网络的隐藏状态,处理包括 6 CN 111587441 A 说 明 书 3/10 页 序列中前一生成时间步长处的N比特输出值的第一回归输入,以生成在生成时间步长处的 输出值中的N个比特的前一半的可能值上的第一分数分布,然后使用该第一分数分布选择 输出值的N个比特的前一半的值。处理单元还可以被配置为,对于每个生成时间步长,使用 回归神经网络并根据相同的隐藏状态,处理第二回归输入,该第二回归输入包括(i)序列中 前一时间步处的N比特输出值,以及(ii)N个比特的前一半的值,以生成在生成时间步长处 的输出值中的N个比特的后一半的可能值上的第二分数分布,然后使用该第二分数分布选 择输出值的N个比特的后一半的值。 可以实现本说明书中描述的主题的特定实施例,以便实现以下优点中的一个或多 个。 通过首先生成N个比特的前一半的值,例如最高有效位,然后生成N个比特的后一 半的值,例如最低有效位,以前一半的值为条件,系统提高了生成的输出的准确度。此外,网 络可以在计算紧凑的同时实现这种提高的准确度。特别地,因为神经网络仅包括单个回归 层(和具有相对低的计算成本的输出层)来对条件输入进行操作,所以该网络可以比传统方 法更快地生成高质量的输出。这可以允许在需要实时生成输出的环境中使用网络,例如,当 部署在移动设备或另一用户设备上时。 此外,系统可以每时间步长生成两个输出,而不需要重新计算计算上昂贵的矩阵 乘法,即,通过仅计算一次对更新隐藏状态的回归贡献,最小化生成第二输出所需的额外计 算和处理能力。 此外,通过在比特的前一半和后一半上生成单独的分数分布,系统减少了输出空 间,允许多比特值的有效预测。作为特定的示例,当N是16,即所有的值都是16比特值时,神 经网络只需要两个相对小的输出空间(每个都具有两个为2^8的分数的分数分布)而不是一 个大的输出空间(每个时间步长都需要具有分数分布,该分数分布具有2^16分数),减少了 有效预测16比特值所需的计算量。 网络的架构非常适合在GPU或其他专用硬件上进行优化,从而节省额外的计算和 时间。例如,在实现方式中,网络仅具有单个回归层,并且回归层的隐藏状态的大小,即隐藏 状态中的单元的数量,可以容易地被配置为优化专用硬件上可用的存储器。 本说明书中描述的主题的一个或多个实施例的细节在附图和以下描述中阐述。本 主题的其他特征、方面和优点将从说明书、附图和权利要求中变得清楚。 附图说明 图1示出了示例神经网络系统。 图2是示出由回归神经网络执行以在生成时间步长处生成输出值的处理的图。 图3是用于生成输出示例的示例过程的流程图。 不同附图中相同的附图标记和名称指示相同的元件。