技术摘要:

本发明提供了一种良率参数文件和门级网表的生成方法以及芯片的开发流程,其中良率参数文件的生成方法包括:首选,提供数据库,且所述数据库中具有多个单元的数据参数;其次,建立仿真验证平台,并对所述单元进行仿真得到仿真参数,确认所述仿真参数与所述单元的数据参 全部

背景技术:

SOC(system on chip,系统级芯片)的开发流程包括RTL(Register Transfer Level,寄存器传输级)Code(代码)到Synthesis(综合)的过程,且在此过程中仅仅依照原先 设计的HDL(Hardware Description Language,硬件描述语言)代码不足以将设计的逻辑电 路转换成门级网表,还需要配合工厂提供的工艺库(CDK)和.lib文件。所述.lib文件与本身 设计的.v文件(RTL代码)进行综合,即将.v文件中的功能、逻辑、时序、电压、电流和功耗等 描述,并通过与.lib文件中实际电子单元的数值参数配合,实现逻辑功能电路,也就是所谓 的门级网表。 而现有的SOC的开发流程中并不包含良率文件,需要调用Reused IP(Reused Intellectual Property Component,可重复使用的IP核)去避免芯片生成良率的问题。使 用Reused IP,即在综合时,调用Reused IP进行综合。而使用Reused IP生成的电路网表,符 合.v文件中各种的电性参数要求。由于调用的是Reused IP,所以有实际的流片数据,即生 成良率的资料,因此,生成的电路网表还可以来确保芯片生成的良率。 但是,并不是所有的功能块都有Reused IP可以调用,如果没有可以调用的Reused IP,就必须重新设计IP核,不但耗时,也没有实际流片后的数据,所以没办法保证芯片生成 的良率。

技术实现要素:

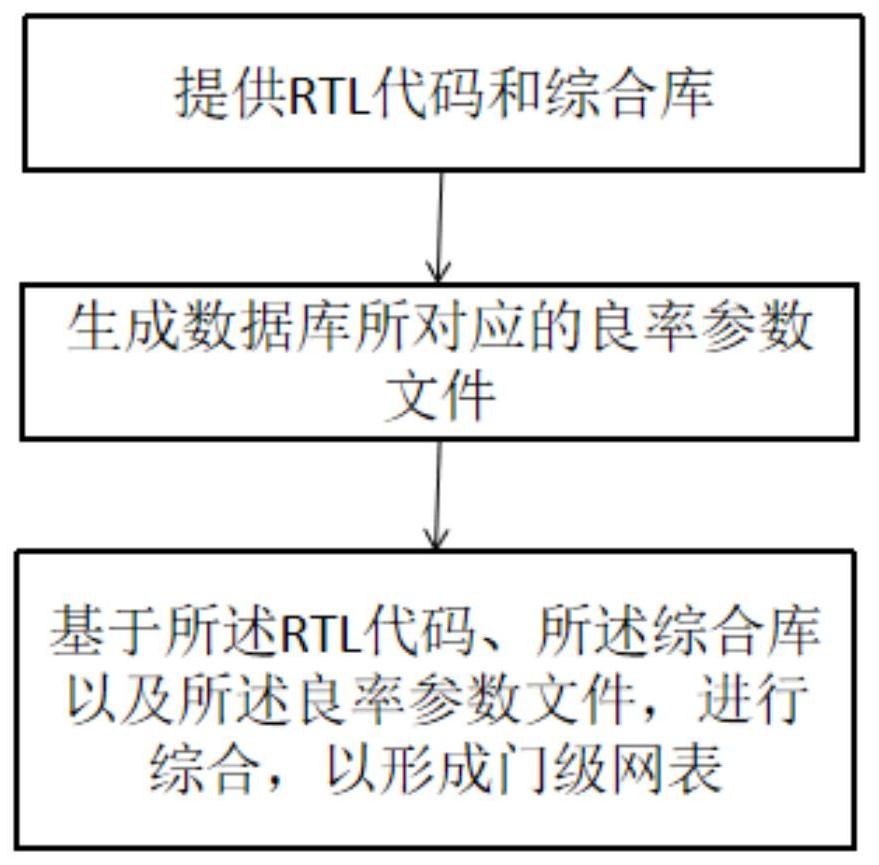

本发明的目的在于提供一种良率参数文件和门级网表的生成方法以及芯片的开 发流程,能够提高流片的成功率,缩短芯片的开发周期和开发成本。 为实现上述目的,本发明提供一种良率参数文件的生成方法,包括: 步骤S11:提供数据库,且所述数据库中具有多个单元的至少一种数据参数; 步骤S12:建立仿真验证平台,并对所述单元进行仿真得到仿真参数,确认所述仿 真参数与所述单元的相应的所述数据参数的一致性; 步骤S13:设定所述仿真验证平台的约束条件,并通过所述仿真验证平台对所述单 元进行蒙卡仿真得到良率仿真结果,且所有单元的良率仿真结果归纳成良率参数文件。 可选的,在所述的良率参数文件的生成方法中,所述数据库包括.lib数据库,所述 单元包括标准单元、输入输出单元以及IP核,而所述标准单元包括由晶体管串联或者并联 组成的基本型态器件和由所述基本型态器件串联或者并联组成的复杂型态器件。 可选的,在所述的良率参数文件的生成方法中,多个所述单元组成电路,若各单元 之间串联,则所述电路的良率为各单元的良率的乘积;若各单元之间并联,则所述电路的良 率为各单元的良率中的最小值。 4 CN 111581899 A 说 明 书 2/9 页 可选的,在所述的良率参数文件的生成方法中,所述仿真验证平台的约束条件包 括单元的信号输出、延迟时间或者输出频率满足设定要求。 可选的,在所述的良率参数文件的生成方法中,确认所述仿真参数和所述单元的 数据参数的一致性的方法包括: 步骤S121:选择数据库中的一坐标对应的数据条件; 步骤S122:将所述数据条件输入至仿真验证平台,得到仿真参数; 步骤S123:对比所述仿真参数与所述数据库中该坐标对应的数据参数是否一致。 为实现上述目的以及其他相关目的,本发明还提供了一种门级网表的生成方法, 包括: 步骤S21:提供RTL代码和综合库,其中所述RTL代码用于描述单元功能的逻辑思 维,所述综合库包括文艺库和数据库,所述文艺库具有工厂提供的单元,所述数据库具有所 述单元的至少一种数据参数; 步骤S22:采用上述所述的良率参数文件的生成方法,生成所述数据库所对应的良 率参数文件; 步骤S23:基于所述RTL代码、所述综合库以及所述良率参数文件,进行综合,以形 成门级网表。 可选的,在所述的门级网表的生成方法中,在执行步骤S22之后且在执行步骤S23 之前,还将所述RTL代码翻译成工具可读文件,并进行综合前约束条件设定;在步骤S23中, 采用综合库和所述良率参数文件对所述工具可读文件进行综合,形成所述门级网表。 可选的,在所述的门级网表的生成方法中,在步骤S23中,所述综合的过程包括: 步骤S231:在数据库中筛选符合RTL代码的单元; 步骤S232:对所述筛选出的单元进行敏感性分析,筛选出敏感性单元; 步骤S233:通过良率分析文件对筛选出的敏感性单元进行良率筛选。 步骤S234:由良率筛选之后的单元生成电路。 可选的,在所述的门级网表的生成方法中,在步骤S23中,所述综合前的约束条件 包括:时序约束条件、功耗约束条件和良率约束条件。 为实现上述目的以及其他相关目的,本发明还提供了一种芯片的开发流程,包括: 步骤S31:采用上述所述的门级网表的生成方法形成门级网表,以得到相应的芯片 设计; 步骤S32:对所述芯片设计进行一次流片以及流片后的一次性能验证; 步骤S33:当所述芯片设计通过所述性能验证时,进行试量产。 综上所述,在本发明提供的良率参数文件的生成方法,通过良率仿真得到良率仿 真结果,最终归纳成良率参数文件。所述良率参数文件可在后续综合的过程中对单元进行 良率筛选,以使生成的门级电路网表有完整的良率仿真数据,换言之,不需要透过流片,便 可以有可靠的资料,且此仿真数据与流片后测试的数据相匹配,提高了流片的成功率,使得 可以仅通过一次流片及流片后的一次验证即可决定是否进行芯片量产,因此可以达到减少 芯片开发成本和开发周期,即节省了芯片设计到量产的时间、人力和成本。 5 CN 111581899 A 说 明 书 3/9 页 附图说明 图1是本发明一实施例中的基本型态的标准单元示意图; 图2是本发明一实施例中的复杂型态的标准单元示意图; 图3是本发明一实施例中的仿真验证平台对坐标(1,1)对应的单元的仿真时序图; 图4是本发明一实施例中的五级反相器示意图; 图5-图8分别是坐标(1,1)对应的单元的下降延迟、上升延迟、下降转换和上升转 换的延迟良率分布图和数据图; 图9-图14分别是坐标(6,6)对应的单元的下降延迟、上升延迟、下降转换和上升转 换的延迟良率分布图和数据图; 图15是坐标(6,6)对应的单元的仿真次数分析数据图; 图16是本发明一实施例中的具有输出负载电容的反相器的示意图; 图17是本发明一实施例中的反相器的输入和输出转换延迟时间示意图; 图18是本发明一实施例中的反相器的转换上升时间和下降时间示意图; 图19是本发明一实施例中的反相器的上升传播时间和下降传播时间示意图; 图20和图21是本发明一实施例中的.lib文件代码内容模板; 图22是本发明一实施例中的良率参数文件的代码内容模板; 图23是本发明一实施例中的一种门级网表的生成方法的流程图; 图24是本发明一实施例中的反相器的结构示意图; 图25是本发明一实施例中的NOR闸的结构示意图; 图26是本发明一实施例中提供的一种信号图; 图27是图26中的信号图对应的.v文件; 图28-图31是发明一实施例中通过,lib文件筛选的反相器的结构示意图; 图32是满足.v文件要求对应的.lib文件代码; 图33是筛选出的单元各指标的良率数据图; 图34是由良率筛选之后的单元生成电路; 其中,图1~图34中: 10-晶体管,20-反相器。