技术摘要:

本申请提供一种半导体模块封装方法及半导体模块。该半导体模块封装方法包括:将第一芯片组件贴装在载板上;通过第一包封层覆盖在整个所述载板上,对所述第一芯片组件进行塑封形成第一包封结构件;剥离所述载板;在所述第一包封结构件上形成第一再布线结构,所述第一再 全部

背景技术:

目前,在封装过程中,对于大功率模块的封装,一般是在基板上印制线路层,将驱 动芯片、功能芯片、电容、电阻通过印刷锡膏和回流的方式焊接固定在基板上,然后再将基 板固定在引线框架上。基板用于多芯片支撑和散热。引线框架用于固定基板,同时引线框架 的结构保证和功率模块工作时所需的焊接疲劳耐受性。 现有技术中的封装大功率模块的过程,都是通过在基板上布线,将电容电阻芯片 通过刷锡膏、键合、塑封等一些列复杂流程制作而成,制作周期长、材料复杂、成本高、产品 尺寸大。 具体地,首先,通过曝光显影及蚀刻的方式将线路转移到基板上;再将有源及无源 器件通过印刷锡膏,引线键合的方式固定在基板上;接续,将基板露出的端子与引线框互 联,然后塑封,完成大功率模块的封装。 另外,这种封装结构中包含多种有机、无机材料,如绿油、金丝、铜丝、铝丝、锡膏、 树脂、铜、芯片等,材料种类越多,不同材料之间的性能匹配的风险因素会更大,给产品可靠 性带来很大挑战。 随着电子设备小型轻量化,具有紧凑结构、小体积的大功率模块受到越来越多的 市场青睐。 然而,如何进一步减小大功率模块的体积是本领域有待解决的一个难题。

技术实现要素:

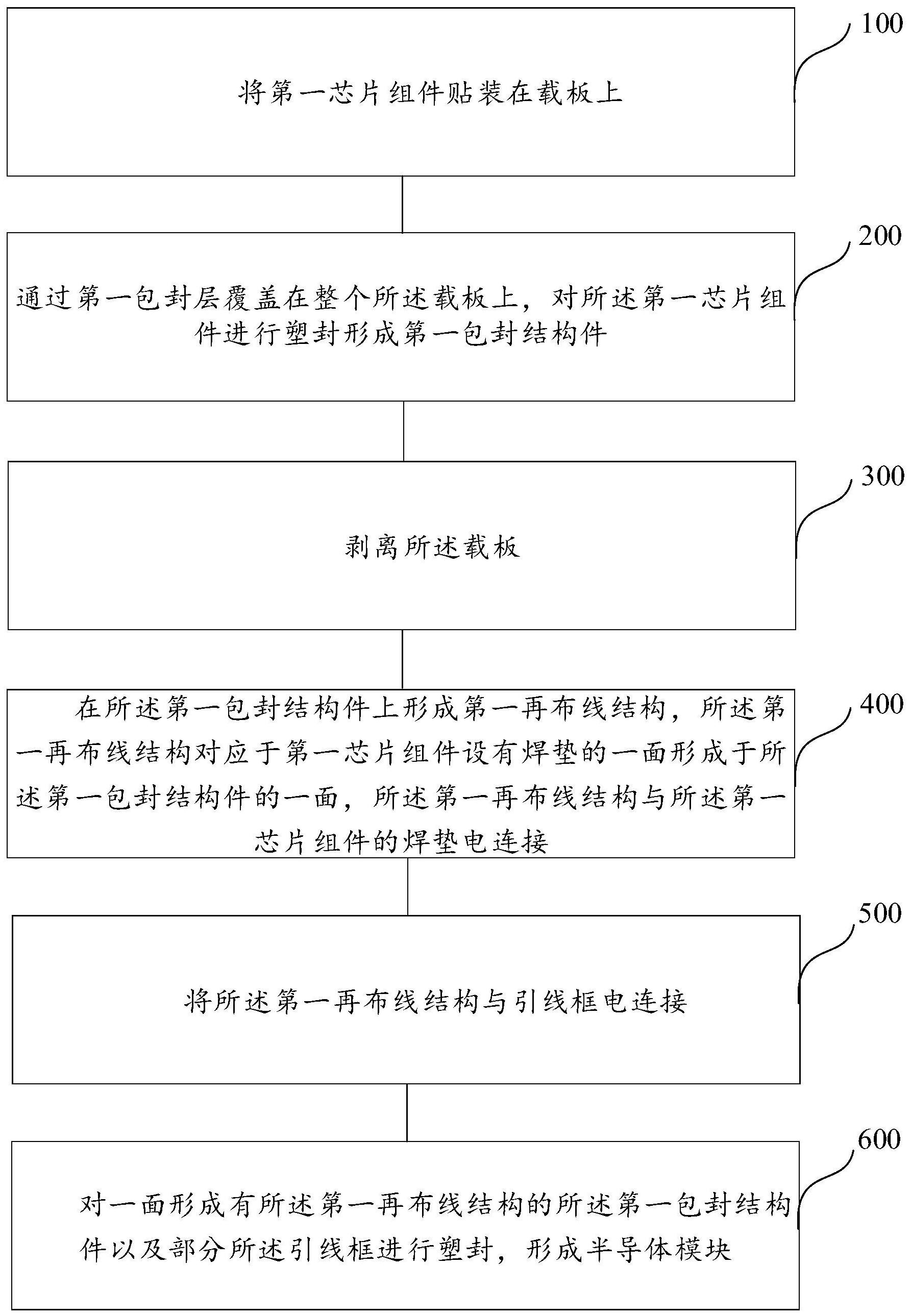

本申请的一个方面提供一种半导体模块封装方法,其包括以下步骤: S1:将第一芯片组件贴装在载板上; S2:通过第一包封层覆盖在整个所述载板上,对所述第一芯片组件进行塑封形成 第一包封结构件; S3:剥离所述载板; S4:在所述第一包封结构件上形成第一再布线结构,所述第一再布线结构对应于 第一芯片组件设有焊垫的一面形成于所述第一包封结构件的一面,所述第一再布线结构与 所述第一芯片组件的焊垫电连接; S5:将所述第一再布线结构与引线框电连接; S6:对一面形成有所述第一再布线结构的所述第一包封结构件以及部分所述引线 框进行塑封,形成半导体模块。 可选的,所述第一再布线结构包括相对的第一表面和第二表面,所述第一再布线 结构形成于所述第一包封结构件的第一表面,在步骤S4之后,以及步骤S5之前,所述半导体 5 CN 111599769 A 说 明 书 2/10 页 模块封装方法包括: 对所述第一包封结构件的第二表面进行研磨。 可选的,所述第一芯片组件包括电容、电阻和芯片中的一种或多种。 本申请的另一个方面提供一种半导体模块封装方法,其包括以下步骤: S1:将第一芯片组件贴装在载板上; S2:通过第一包封层覆盖在整个所述载板上,对所述第一芯片组件进行塑封形成 第一包封结构件; S3:剥离所述载板; S4:在所述第一包封结构件上形成第一再布线结构,所述第一再布线结构对应于 第一芯片组件设有焊垫的一面形成于所述第一包封结构件的一面,所述第一再布线结构与 所述第一芯片组件的焊垫电连接; S5:将第二芯片组件与所述第一再布线结构连接,并通过第二包封层覆盖在整个 所述第一再布线结构上,对所述第二芯片组件塑封形成所述第二包封结构件; S6:在所述第二包封结构件上形成第二再布线结构,所述第二再布线结构对应于 第二芯片组件设有焊垫的一面形成于所述第二包封结构件的一面,所述第二再布线结构与 所述第二芯片组件的焊垫、和/或所述第一再布线结构电连接; S7:将所述第二再布线结构与引线框电连接; S8:对一面形成有所述第一再布线结构的所述第一包封结构件、一面形成有所述 第二再布线结构的所述第二包封结构件以及部分所述引线框进行塑封,形成半导体模块。 可选的,在步骤S7中,重复步骤S5和步骤S6,得到叠设的N层所述第二包封结构件 及N层所述第二再布线结构,N为大于2的整数,其中, 第1层所述第二包封结构件中的所述第二芯片组件与所述第一再布线结构连接, 第N层所述第二再布线结构与第N层所述第二包封结构件中的第二芯片组件、和/或第N-1层 所述第二再布线结构电连接;及, 将第N层所述第二再布线结构与所述引线框电连接; 在步骤S8中,对一面形成有所述第一再布线结构的所述第一包封结构件、第1层至 第N层一面形成有所述第二再布线结构的所述第二包封结构件以及部分所述引线框进行塑 封,形成半导体模块。 可选的,所述第一芯片组件包括电容、电阻和芯片中的一种或多种。 可选的,所述第二芯片组件包括电容、电阻和芯片中的一种或多种。 可选的,所述第一再布线结构包括相对的第一表面和第二表面,所述第一再布线 结构形成于所述第一包封结构件的第一表面,在步骤S6之后,以及步骤S7之前,所述半导体 模块封装方法包括: 对所述第一包封结构件的第二表面进行研磨。 本申请的再一个方面提供一种半导体模块,其包括: 第一包封结构件,包括相对的第一表面和第二表面,且设有内凹的第一腔体,第一 芯片组件位于所述第一腔体内,所述第一芯片组件包括设有焊垫的第一面、以及相对于第 一面设置的第二面,所述第一芯片组件的第二面露出于所述第一包封结构件的第二表面; 第一再布线结构,对应于所述第一芯片组件的第一面形成于所述第一包封结构件 6 CN 111599769 A 说 明 书 3/10 页 的第一表面,用于将所述第一芯片组件的焊垫引出; 引线框,与所述第一再布线结构电连接; 外包封层,包封于第一表面形成有所述第一再布线结构的所述第一包封结构件以 及部分所述引线框外。 本申请的又一个方面提供一种半导体模块,其包括: 第一包封结构件,包括相对的第一表面和第二表面,且设有内凹的第一腔体,第一 芯片组件位于所述第一腔体内,所述第一芯片组件包括设有焊垫的第一面、以及相对于所 述第一面设置的第二面,所述第一芯片组件的第二面露出于所述第一包封结构件的第二表 面; 第一再布线结构,对应于所述第一芯片组件的第一面形成于所述第一包封结构件 的第一表面,用于将所述第一芯片组件的焊垫引出; 第二包封结构件,包括相对的第三表面和第四表面,且设有内凹的第二腔体,第二 芯片组件位于所述第二腔体内,所述第二芯片组件与所述第一再布线结构连接,所述第二 芯片组件包括设有焊垫的第三面、以及相对于所述第三面设置的第四面,所述第二芯片组 件的第四面朝向所述第二腔体的底部; 第二再布线结构,对应于所述第二芯片组件的第三面形成于所述第二包封结构件 的第三表面,用于将所述第二芯片组件的焊垫引出,和/或与所述第一再布线结构电连接; 引线框,与所述第二再布线结构电连接; 外包封层,包封于第一表面形成有所述第一再布线结构的所述第一包封结构件、 第三表面形成有所述第二再布线结构的所述第二包封结构件以及部分所述引线框外。 可选的,所述半导体模块包括叠设的N层所述第二包封结构件及N层所述第二再布 线结构,N为大于2的整数,其中, 第1层所述第二包封结构件中的所述第二芯片组件与所述第一再布线结构连接, 第N层所述第二再布线结构用于引出第N层所述第二包封结构件中的第二芯片组件的焊垫, 第N层所述第二再布线结构与所述引线框电连接,和/或与第N-1层所述第二再布线结构电 连接; 所述外包封层包封于第一表面形成有所述第一再布线结构的所述第一包封结构 件、第1层至第N层第三表面形成有所述第二再布线结构的所述第二包封结构件以及部分所 述引线框外。 本申请实施例提供的上述半导体模块封装方法及半导体模块,通过将各类芯片组 件通过扇出的方式完成封装,暴露出所需的端子,再将端子与引线框互联之后塑封,实现大 功率模块封装;相对于现有技术,由于半导体模块中不需要基板,从而大大地缩小了半导体 模块的整体体积,使半导体模块具有体积小、结构紧凑的优势,适合小型轻量电子设备,同 时半导体模块中材料种类大大减少,可以显著提高因热失配导致的可靠性问题,并且使被 封装在半导体模块内的芯片组件的任意一面可以暴露,而达到散热目标。 附图说明 图1是根据本申请的实施例1提出的半导体模块封装方法的流程图。 图2(a)-图2(q)是根据本申请的实施例1中半导体模块封装方法的工艺流程图。 7 CN 111599769 A 说 明 书 4/10 页 图3是根据本申请的实施例1提供的利用上述半导体模块封装方法得到的半导体 模块的结构示意图。 图4是根据本申请的实施例2提出的半导体模块封装方法的流程图。 图5(a)-图5(p)是根据本申请的实施例2中半导体模块封装方法的工艺流程图。 图6是根据本申请的实施例2提供的利用上述半导体模块封装方法得到的半导体 模块的结构示意图。