技术摘要:

本发明公开了一种实现多tap访问DDR的方法及系统,其通过设置预设数量的数据缓存模块,获取图像数据的大小以及相机的tap类型,根据所述tap类型确定扫描方向;根据tap类型选择所需数量的数据缓存模块,利用数据缓存模块缓存同一扫描方向的图像数据以实现第一次数据重组, 全部

背景技术:

TAP(TestAccessPort)是一个通用的端口,通过TAP可以访问芯片提供的所有数据 寄存器(DR)和指令寄存器(IR),对整个TAP的控制可通过TAP控制器(TAPController)来完 成的。DDR SDRAM(Double Data Rate Synchronous Dynamic Random Access Memory)为双 倍数据率同步动态随机存取存储器,其数据传输速度为系统时钟频率的两倍,由于速度增 加,其传输性能优于传统的SDRAM。目前,相机的采集图像的输出主要利用tap方式访问DDR 来实现数据的写入和写出,其可以应用于工业相机显示、机器视觉、自动化AOI检测领域。 图1(a)-(h)分别为现有技术的8种相机tap模式的示意图。如图1所示,目前相机主 要存在8种tap模式,其中,图(a)-(h)所示的分别为1X-1Y的tap模式、1X-1Y2的tap模式、2X- 1Y的tap模式、1X2-1Y的tap模式、2XE-1Y的tap模式1、2XE-1Y的tap模式2、2XM-1Y的tap模式 和2XE-2YE模式,A,B,C ,D分别表示的是4个pixel,由于pixel可能是8bit,10bit ,12bit , 16bit,以单个pixel为8bit为示例,X表示横向坐标,Y表示纵向坐标,1X-1Y表示的是水平和 垂直方向是相机在水平方向依次输出一个pixel,方向是从左到右,从上到下。 由于图像采集装置(如相机)所支持的tap方式与需要输出的tap方式不一样,由于 数据输入输出格式不一样,从而不能使用tap端口直接进行图像的传输,以AOI检测应用为 示例,每集成一种相机开发人员都需要重新开发相关的功能来实现输入输出的tap方式转 换,因而造成诸多不便。

技术实现要素:

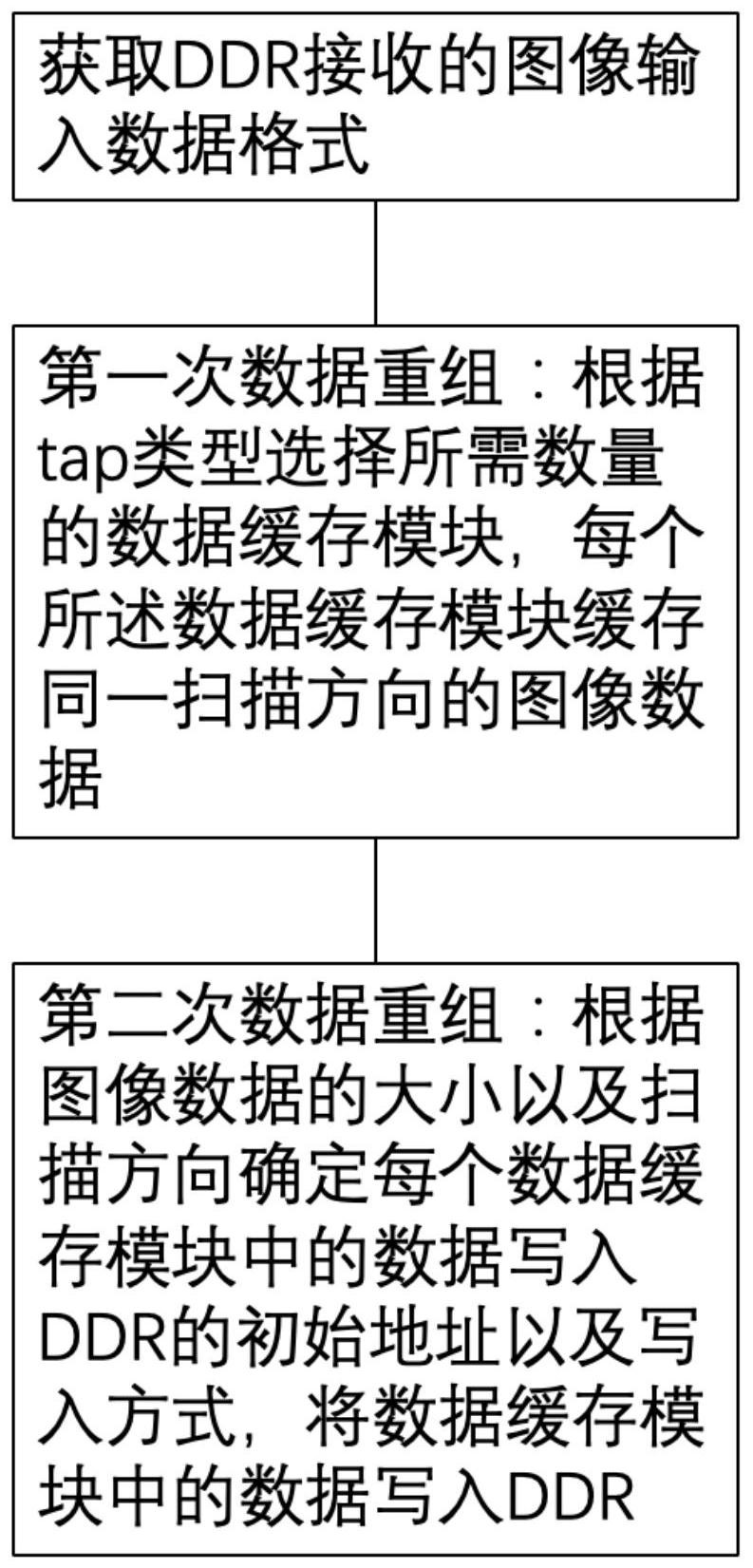

针对现有技术的以上缺陷或改进需求,本发明提供了一种实现多tap访问DDR的方 法及系统,其通过获取输入tap方式的数据格式,设置与单次突发的初始输入像素点位置坐 标对应的缓存单元,通过多tap访问DDR的方法可实现输入输出tap方式不同的图像数据传 输。 为实现上述目的,按照本发明的一个方面,提供了一种实现多tap访问DDR的方法, 该方法包括如下步骤: 设置预设数量的数据缓存模块,数据缓存模块用于进行第一次数据重组; 获取图像数据的大小以及相机的tap类型,根据tap类型确定扫描方向; 根据tap类型选择所需数量的数据缓存模块,利用数据缓存模块进行第一次数据 重组,每个数据缓存模块缓存同一扫描方向的图像数据; 根据图像数据的大小以及扫描方向确定每个数据缓存模块中的数据写入DDR的初 始地址以及写入方式,将数据缓存模块中的数据写入DDR,进行第二次数据重组。 作为本发明的进一步改进,利用数据缓存模块进行第一次数据重组,每个数据缓 存模块缓存同一扫描方向的图像数据具体为: 4 CN 111554334 A 说 明 书 2/6 页 设置所需数量的寄存器,每一寄存器寄存扫描方向相同的像素数据; 将从DDR中读取的像素数据根据扫描方向分别写入不同的寄存器,当所有寄存器 写满,则将寄存器中存储的数据写入与寄存器中存储的数据的扫描方向对应的数据缓存模 块中。 作为本发明的进一步改进,根据tap类型选择对应数量的数据缓存模块后,将未使 用的数据缓存模块写入无效数据。 作为本发明的进一步改进,将数据缓存模块中的数据写入DDR具体方式为: 通过轮询的方式读取每个数据缓存模块中的数据,并将每个数据缓存模块中的数 据通过burst方式写入DDR对应的地址中。 作为本发明的进一步改进,写入方式至少包括根据初始地址以地址递增的方式写 入,或者根据初始地址以地址递减的方式写入,或者根据初始地址以地址成等差数列跳变 的方式写入。 为实现上述目的,按照本发明的另一个方面,提供了一种实现多tap访问DDR的系 统,该系统包括DDR、数据读取模块、预设数量的数据缓存模块和数据写入模块,数据缓存模 块用于进行第一次数据重组; 数据读取模块用于获取图像数据的大小以及相机的tap类型,根据tap类型确定扫 描方向,根据tap类型选择所需数量的数据缓存模块,利用数据缓存模块进行第一次数据重 组,每个数据缓存模块缓存同一扫描方向的图像数据; 数据写入模块用于根据图像数据的大小以及扫描方向确定每个数据缓存模块中 的数据写入DDR的初始地址以及写入方式,将数据缓存模块中的数据写入DDR,进行第二次 数据重组。 作为本发明的进一步改进,利用FPGA实现数据读取模块、预设数量的数据缓存模 块和数据写入模块,其中,FPGA和DDR之间通过32bit的axi4数据总线连接,利用axi4lite总 线实现对数据读取模块和数据写入模块的逻辑控制。 作为本发明的进一步改进,利用数据缓存模块进行第一次数据重组,每个数据缓 存模块缓存同一扫描方向的图像数据具体为: 设置所需数量的寄存器,每一寄存器寄存扫描方向相同的像素数据; 将从DDR中读取的像素数据根据扫描方向分别写入不同的寄存器,当所有寄存器 写满,则将寄存器中的数据写入与寄存器中存储的数据的扫描方向对应的数据缓存模块 中。 作为本发明的进一步改进,将数据缓存模块中的数据写入DDR具体方式为: 通过轮询的方式读取每个数据缓存模块中的数据,并将每个数据缓存模块中的数 据通过burst方式写入DDR对应的地址中。 作为本发明的进一步改进,写入方式至少包括根据初始地址以地址递增的方式写 入,或者根据初始地址以地址递减的方式写入,或者根据初始地址以地址成等差数列跳变 的方式写入。 总体而言,通过本发明所构思的以上技术方案与现有技术相比,具有以下 有益效果: 本发明的一种实现多tap访问DDR的方法及系统,其通过依据输入tap方式的数据 5 CN 111554334 A 说 明 书 3/6 页 格式,利用数据缓存模块缓存同一扫描方向的图像数据以实现第一次数据重组,根据图像 数据的大小以及扫描方向确定每个数据缓存模块中的数据写入DDR的初始地址以及写入方 式,将数据缓存模块中的数据写入DDR以实现第二次数据重组,通过两次数据重组,从而实 现图像输入数据的重排列和拼接后再依据像素点的位置坐标将数据重新写入DDR中,从而 实现输入输出tap方式不同的图像数据传输。 本发明的一种实现多tap访问DDR的方法及系统,其采用轮询方式读取缓存单元的 数据,将未使用的缓存单元写入无效数据,通过轮询方式读取到缓存单元中的无效数据时 直接丢弃,从而使得设计的读取程序不需要调整即可以满足所有输入格式的需求。 附图说明 图1(a)-(h)分别为现有技术的8种相机tap模式的示意图; 图2为本发明实施例的一种实现多tap访问DDR的方法的示意图; 图3为本发明实施例的实现多tap访问DDR的装置的一种实施方式的示意图; 图4为本发明实施例的缓存数据的一种实施方式的示意图。