技术摘要:

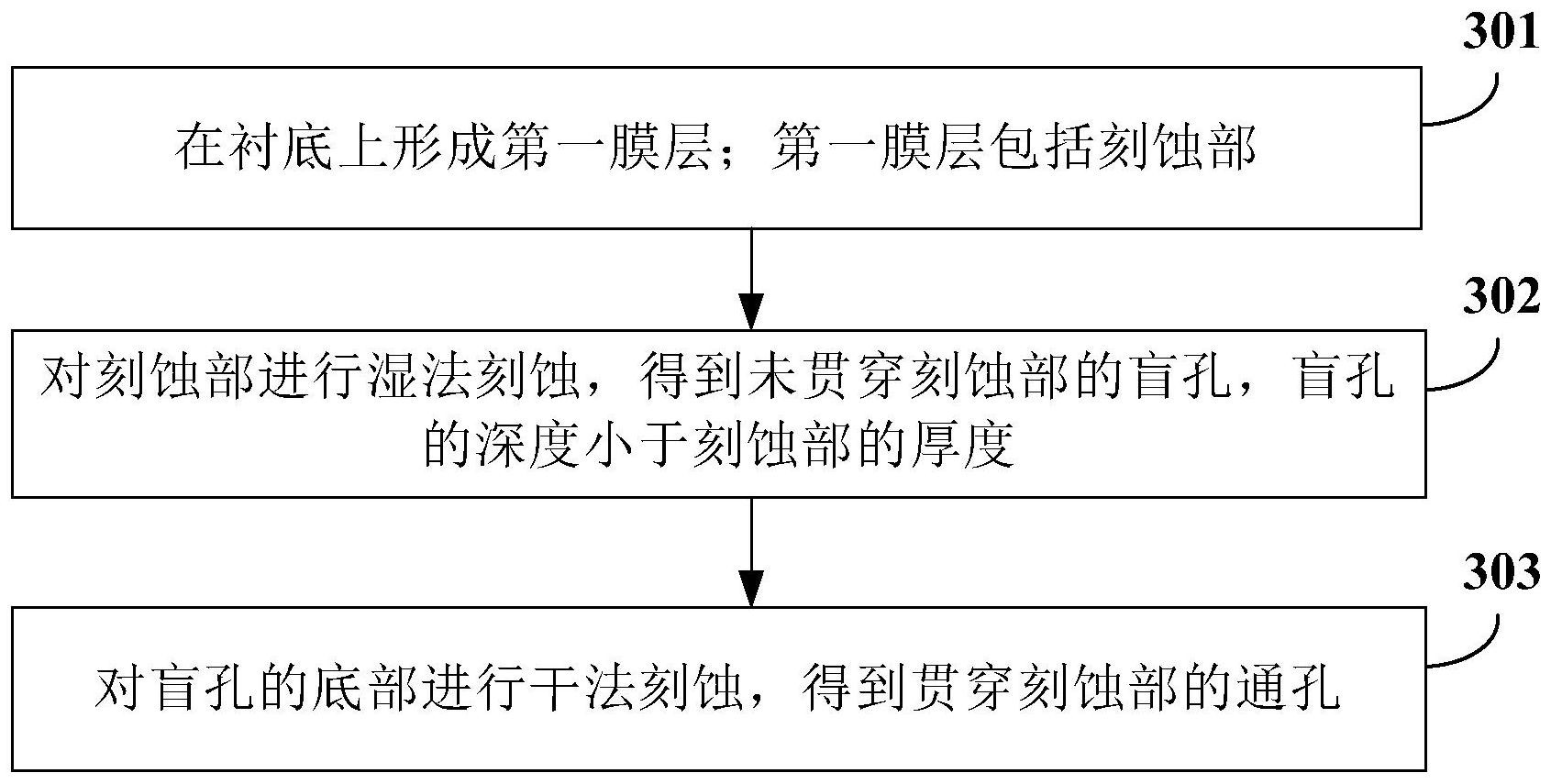

本发明涉及一种阵列基板及其制备方法和显示装置。所述阵列基板的制备方法,包括:在衬底上形成第一膜层;第一膜层包括刻蚀部;对刻蚀部进行湿法刻蚀,得到未贯穿刻蚀部的盲孔,盲孔的深度小于刻蚀部的厚度;对盲孔的底部进行干法刻蚀,得到贯穿刻蚀部的通孔。根据本发 全部

背景技术:

相关技术中,顶栅型TFT(Thin Film Transistor,薄膜晶体管)具有短沟道的特 点,所以,其开态电流Ion得以有效提升,因而,可以显著提升显示效果并且能有效降低功 耗。而且,顶栅型TFT的栅极与源漏极重叠面积小,因而产生的寄生电容较小,所以发生GDS (Gate Data Shot,栅极与数据线短路)等不良的可能性也降低。由于顶栅型TFT具有上述显 著优点,越来越受到关注。 相关技术中,顶栅型TFT制备工艺如下:依次沉积形成遮光层、缓冲层、有源层、栅 极绝缘层以及栅极,然后,采用自对准工艺对有源层进行导体化处理,得到源区与漏区,接 着,沉积层间介质层,然后,采用干刻工艺制备贯穿层间介质层和缓冲层的过孔和贯穿层间 介质层的过孔,接着,沉积金属层并构图形成源漏极层。 随着显示装置逐渐向大尺寸、高分辨率方向发展,栅极、源漏极等金属走线越来越 厚,进而需要更厚的层间介质层、钝化保护层等无机层对其进行覆盖才能有效提高良率。随 着无机层厚度的提升,各种无机膜上的过孔也越来越深。相关技术中,干刻工艺已无法刻穿 这么厚的无机层,因为干刻工艺对掩膜光刻胶的损伤速率非常快,导致无机层还没有刻穿 而光刻胶已被完全损伤掉,从而无法顺利形成过孔。

技术实现要素:

本发明提供一种阵列基板及其制备方法和显示装置,以解决相关技术中的不足。 根据本发明实施例的第一方面,提供一种阵列基板的制备方法,包括: 在衬底上形成第一膜层;所述第一膜层包括刻蚀部; 对所述刻蚀部进行湿法刻蚀,得到未贯穿所述刻蚀部的盲孔,所述盲孔的深度小 于所述刻蚀部的厚度; 对所述盲孔的底部进行干法刻蚀,得到贯穿所述刻蚀部的通孔。 在一个实施例中,进行所述湿法刻蚀使用的刻蚀液包括氟化氢、氟化铵与表面活 性剂,其中,氟化氢的质量分数为2%~5%,氟化铵的质量分数为20%~40%,表面活性剂 的质量分数为1%~5%。 在一个实施例中,所述通孔包括第一侧壁与第二侧壁,所述第一侧壁在所述湿法 刻蚀中形成,所述第二侧壁在所述干法刻蚀中形成,所述第二侧壁与所述衬底靠近所述第 一膜层的表面之间的夹角大于所述第一侧壁与所述衬底靠近所述第一膜层的表面之间的 夹角。 在一个实施例中,所述第一膜层包括打孔区;所述刻蚀部位于所述打孔区;所述打 孔区包括第一打孔区与第二打孔区,所述刻蚀部包括第一刻蚀部与第二刻蚀部;所述第一 刻蚀部位于所述第一打孔区,所述第二刻蚀部位于所述第二打孔区;所述盲孔包括第一盲 5 CN 111584423 A 说 明 书 2/9 页 孔与第二盲孔;所述第一盲孔在所述第一膜层上的投影位于所述第一打孔区,所述第二盲 孔在所述第一膜层上的投影位于所述第二打孔区。所述在衬底上形成第一膜层之前,还包 括:在衬底上形成第二膜层,所述第二膜层位于所述衬底与所述第一膜层之间;在所述第二 膜层上形成第三膜层,所述第三膜层位于所述第二膜层与第一膜层之间;所述第二膜层包 括器件区,所述第三膜层在所述第二膜层上的投影位于所述器件区;所述第三膜层包括导 电区,所述导电区在所述第一膜层上的投影位于所述第二打孔区。所述在衬底上形成第一 膜层之后,还包括:在所述第一膜层远离所述衬底的一侧形成光刻胶层,所述光刻胶层包括 镂空部与厚度减薄部,所述厚度减薄部在所述第一膜层上的投影落在所述第二打孔区内, 所述镂空部在所述第一膜层上的投影落在所述第一打孔区内。所述对所述刻蚀部进行湿法 刻蚀,得到未贯穿所述刻蚀部的盲孔,包括:对所述第一刻蚀部进行第一次湿法刻蚀,得到 未贯穿所述第一刻蚀部的第一盲孔,经所述第一次湿法刻蚀后所述第一盲孔的深度为第一 深度,所述第一深度小于所述第一刻蚀部的厚度;对所述厚度减薄部进行灰化处理,去除所 述厚度减薄部,以暴露所述第二刻蚀部;对所述第一盲孔的底部以及所述第二刻蚀部进行 第二次湿法刻蚀,经所述第二次湿法刻蚀后所述第一盲孔的深度为第二深度,所述第二深 度小于所述第一刻蚀部的厚度,且大于所述第一深度,对所述第二刻蚀部进行所述第二次 湿法刻蚀后得到第二盲孔,所述第二盲孔的深度为第三深度,所述第三深度小于所述第二 刻蚀部的厚度。 在一个实施例中,经所述第二次湿法刻蚀后所述第一盲孔的内底面与第一界面之 间的间距为1000~1500埃米,所述第一界面为所述第一膜层与所述第二膜层之间的界面; 所述第二盲孔的内底面与第二界面之间的间距为1000~1500埃米,所述第二界面为所述第 一膜层与所述第三膜层之间的界面。 在一个实施例中,所述通孔包括第一通孔与第二通孔,所述第一通孔在所述第一 膜层上的投影落在所述第一打孔区内,所述第二通孔在所述第一膜层上的投影落在所述第 二打孔区内。所述对所述盲孔的底部进行干法刻蚀,得到贯穿所述刻蚀部的通孔,包括:对 所述第一盲孔的底部以及所述第二盲孔的底部进行干法刻蚀,得到所述第一通孔与所述第 二通孔,所述第一通孔贯穿所述第一刻蚀部与所述第二膜层,所述第二通孔贯穿所述第二 刻蚀部,且未贯穿所述第三膜层。 在一个实施例中,所述第一通孔包括第三侧壁、第四侧壁与第五侧壁,所述第三侧 壁在所述第一次湿法刻蚀中形成,所述第四侧壁在所述第二次湿法刻蚀中形成,所述第五 侧壁在所述干法刻蚀中形成,所述第五侧壁与所述衬底靠近所述第一膜层的表面之间的夹 角大于所述第四侧壁与所述衬底靠近所述第一膜层的表面之间的夹角,所述第四侧壁与所 述衬底靠近所述第一膜层的表面之间的夹角大于所述第三侧壁与所述衬底靠近所述第一 膜层的表面之间的夹角。所述第二通孔包括第六侧壁与第七侧壁,所述第六侧壁在所述第 二次湿法刻蚀中形成,所述第七侧壁在所述干法刻蚀中形成,所述第七侧壁与所述衬底靠 近所述第一膜层的表面之间的夹角大于所述第六侧壁与所述衬底靠近所述第一膜层的表 面之间的夹角。 在一个实施例中,所述在衬底上形成第二膜层之前,还包括:在衬底上形成第四膜 层,所述第四膜层位于所述第二膜层与所述衬底之间,所述第三膜层在所述衬底上的投影 位于所述第四膜层在所述衬底上的投影内,所述第一通孔在所述衬底上的投影位于所述第 6 CN 111584423 A 说 明 书 3/9 页 四膜层在所述衬底上的投影内,所述第一通孔未贯穿所述第四膜层。 在一个实施例中,所述第四膜层为遮光层,所述第四膜层的材料为金属;所述第二 膜层为缓冲层,所述第一膜层为层间介质层,所述第三膜层为有源层,所述有源层包括两个 导电区,一个导电区为源区,另一个导电区为漏区,所述第二打孔区的数目为两个,所述源 区在所述第一膜层上的投影位于一个所述第二打孔区,所述漏区在所述第一膜层上的投影 位于另一个所述第二打孔区,所述第二通孔的数目为两个,所述源区在所述第一膜层上的 投影位于一个第二通孔在所述第一膜层上的投影内,所述漏区在所述第一膜层上的投影位 于另一个第二通孔在所述第一膜层上的投影内。 在一个实施例中,所述有源层还包括有源区,所述有源区位于所述源区与所述漏 区之间;所述在所述第二膜层上形成第三膜层之后,还包括:在所述第三膜层上形成栅极绝 缘层与栅极;所述栅极位于所述栅极绝缘层与所述第一膜层之间,所述有源区位于所述栅 极绝缘层在所述第三膜层上的投影内。 在一个实施例中,所述对所述第一盲孔的底部以及所述第二盲孔的底部进行干法 刻蚀,得到所述第一通孔与所述第二通孔之后,还包括:在所述第一膜层上、所述第一通孔 与所述第二通孔中沉积导电材料并进行图形化,得到源极、漏极以及连接孔,所述源区位于 所述源极在所述第三膜层上的投影内,所述漏区位于所述漏极在所述第三膜层上的投影 内,所述连接孔在所述第一膜层上的投影位于所述第一打孔区,所述连接孔与所述遮光层 电连接,所述连接孔还与所述源极电连接。 在一个实施例中,所述第一膜层的厚度为4000~10000埃米,所述第二膜层的厚度 为2000~5000埃米。 根据本发明实施例的第二方面,提供一种阵列基板,包括: 衬底; 第一膜层,位于所述衬底上,所述第一膜层包括通孔,所述通孔包括第一侧壁与第 二侧壁,所述第一侧壁与所述第二侧壁相接,所述第一侧壁远离所述衬底,所述第二侧壁靠 近所述衬底,所述第二侧壁与所述衬底靠近所述第一膜层的表面之间的夹角大于所述第一 侧壁与所述衬底靠近所述第一膜层的表面之间的夹角。 根据本发明实施例的第三方面,提供一种显示装置,包括上述的阵列基板。 根据上述实施例可知,通过对刻蚀部先进行湿法刻蚀,得到盲孔,然后,再对盲孔 的底部进行干法刻蚀,得到贯穿刻蚀部的通孔,以制备用于导电连接的过孔,可以避免膜层 交界处出现刻蚀裂缝问题。 应当理解的是,以上的一般描述和后文的细节描述仅是示例性和解释性的,并不 能限制本发明。 附图说明 此处的附图被并入说明书中并构成本说明书的一部分,示出了符合本发明的实施 例,并与说明书一起用于解释本发明的原理。 图1是根据相关技术示出的显示面板的结构示意图; 图2是根据相关技术示出的显示面板的扫描电镜图; 图3是根据本发明实施例示出的一种阵列基板的制备方法的流程图; 7 CN 111584423 A 说 明 书 4/9 页 图4是根据本发明实施例示出的另一种阵列基板的制备方法的流程图; 图5~图11是在制备阵列基板的过程中产生的中间结构的示意图; 图12是根据本发明实施例示出的另一种阵列基板的制备方法的流程图; 图13~图17是在制备阵列基板的过程中产生的中间结构的示意图; 图18是根据本发明实施例示出的像素电路的结构示意图; 图19是根据本发明实施例示出的阵列基板的俯视图; 图20是根据本发明实施例示出的一种阵列基板的结构示意图; 图21是根据本发明实施例示出的另一种阵列基板的结构示意图。