技术摘要:

本发明公开了一种双沟道增强型准垂直结构GaN基JFET,在n‑‑GaN层上部左右两个区域形成两个沿生长方向平行的p‑n结形成的双沟道,每个n‑‑GaN沟道都夹于两片p‑GaN层之间,n‑‑GaN沟道在零偏压下处于p‑n内建电场的夹断状态。并公开了其制备方法。该器件调节n型GaN沟 全部

背景技术:

功率半导体器件作为功率转换、控制电路、功率管理等电力电子系统的核心器件, 广泛应用于电力传输、交通运输、消费电子等重要领域。GaN基结型场效应晶体管因具有工 作频率高、输入阻抗高、导通电阻低、功率密度高、击穿电压高等优势,因而使其在可变电阻 和功放领域具有重要应用。JFET通常是耗尽型的器件,在零偏下处于开通状态,而对于电力 电子方面的应用,往往要求功率半导体器件为增强型器件,否则会增加驱动电路的设计难 度,并增大功率半导体器件的关态损耗。

技术实现要素:

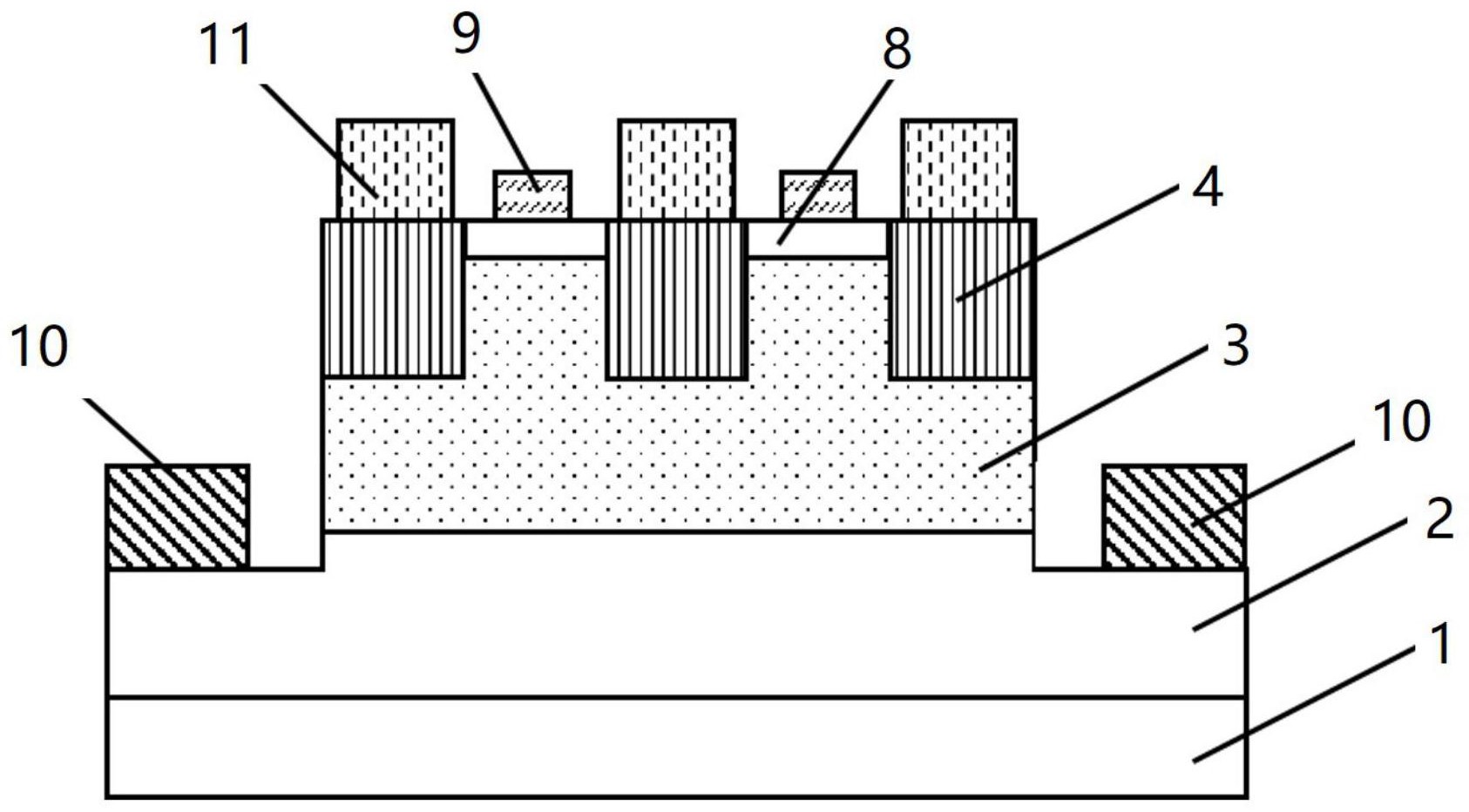

本发明的目的在于提供一种双沟道增强型准垂直结构GaN基JFET,JFET器件具有 大的电流输出。 本发明的目的通过以下技术方案实现: 一种双沟道增强型准垂直结构GaN基JFET,其结构依次包括: 衬底; 在衬底表面形成的n -GaN层及形成于n -GaN层上的漏电极; 在n -GaN层表面形成的n--GaN层; 在n--GaN层上部左右两个区域形成两个沿生长方向平行的p-n结形成的双沟道, 每个n--GaN沟道都夹于两片p-GaN层之间,n--GaN沟道在零偏压下处于p-n内建电场的夹断 状态; 栅电极,设在p-GaN层上; 生长在n--GaN沟道上的n -GaN层; 源电极,设在n--GaN沟道上的n -GaN层上。 本发明还公开了上述的双沟道增强型准垂直结构GaN基JFET的制备方法,其步骤 包括: (1)利用MOCVD系统首先在衬底上外延一层n -GaN层,接着外延一层n--GaN层,再外 延一层p-GaN层,形成GaN外延片; (2)使用PECVD的方法在GaN外延片表面沉积一层掩膜层,在掩膜层表面旋涂一层 光刻胶,通过曝光、显影和烘烤,形成光刻图形,然后在此基础上,利用光刻胶作为掩膜,使 用RIE刻蚀的方法将掩膜层图形化,最后使用丙酮去除外延片上的光刻胶; (3)使用ICP氯基等离子体刻蚀的方法,在GaN外延片上刻蚀出两个凹槽; (4)使用MBE方法通过掩膜选区在凹槽内生长n--GaN沟道和n -GaN层,使得n--GaN 填充在被刻蚀掉的区域与p-GaN层形成p-n结,n -GaN层用来形成源极的欧姆接触,生长完 4 CN 111599856 A 说 明 书 2/4 页 成后去除掩膜层; (5)使用光刻胶作为掩膜,采用ICP刻蚀的方法在器件两侧刻蚀出漏电极沉积区 域,刻蚀深度至n -GaN层; (6)采用电子束蒸发蒸镀源电极和漏电极,退火形成欧姆接触; (7)在p-GaN层表面采用电子束蒸发蒸镀栅电极,退火。 优选的,步骤(1)中外延1-4μm的n -GaN层,外延2-10μm的n--GaN层,外延0.5-2μm的 p-GaN层,其中,n -GaN层掺杂浓度为1*1018-1*1019cm-3,n--GaN层的掺杂浓度为1*1016-8* 1016cm-3,p-GaN层的掺杂浓度为1*1017-8*1017cm-3。 优选的,所述步骤(2)中掩膜层为SiN或SiO2,厚度为200-500nm。 优选的,步骤(3)中凹槽深度与p-GaN层的厚度相同,以保证p-GaN被完全刻蚀掉, 宽度为0.2-0.8μm,每个凹槽之间的间距为0.5-5μm。 优选的,步骤(4)中n-GaN的掺杂浓度为1*1016-8*1016cm-3,n -GaN的掺杂浓度是1* 1018-1*1019cm-3,使用HF去除掩膜层。 优选的,步骤(5)中可过刻0.2-0.5μm。 优选的,步骤(6)中源电极和漏电极为Ti/Al/Ni/Au多层金属,厚度为30/150/50/ 100nm,蒸镀后在850℃的N2氛围中退火30s。 优选的,步骤(7)中栅电极为Ni/Au多层金属,厚度为20/20nm,蒸镀后在500℃的空 气氛围中退火10min。 本发明的有益效果是利用多沟道实现了增强型的GaN基结型场效应晶体管(GaN- JFET)。而传统的结型场效应晶体管为保证大的输出电流均采用了宽的单沟道,为耗尽型模 式,零偏下处于导通状态,会增加功率半导体器件的关态损耗,并且使用时不安全。增强型 器件不仅没有这些问题,还可以简化驱动电路。同时,平行的多沟道保证了GaN基结型场效 应晶体管大的输出电流;采用准垂直结构,无需导电的GaN同质衬底,可降低器件成本。与传 统的刻蚀沟道层后再进行p-GaN层再生长的方法不同,n--GaN层的再生长为同质外延生长, 可以能够保证高质量的再生长界面,提高器件的可靠性。同时,p-GaN与n--GaN层在垂直方 向上的界面为原位生长得到,在器件最为关键的p-n结界面处避免了刻蚀引入的缺陷,有利 于沟道的耗尽与夹断和降低器件开态漏电流。 附图说明 图1是实施例1的步骤(1)得到的GaN外延片的结构示意图。 图2是实施例1的步骤(2)得到的GaN外延片的结构示意图。 图3是实施例1的步骤(3)得到的GaN外延片的结构示意图。 图4是实施例1的步骤(4)得到的GaN外延片的结构示意图。 图5是实施例1的步骤(5)得到的GaN外延片的结构示意图。 图6是实施例1的步骤(7)得到的GaN基JFET的结构示意图。