技术摘要:

本发明提供一种芯片结构及其乘加计算引擎,乘加计算引擎包括:多个卷积引擎,每个所述卷积引擎包括15*M*N个乘法器以及至少设置在部分乘法器之间的加法器,M,N均为大于1的整数,其中,根据所述卷积引擎所应用的不同的卷积核的尺寸,按不同的方式激活所述乘法器之间、所述 全部

背景技术:

卷积神经网络(Convolutional Neural Network,CNN)是一种前馈神经网络,它的 人工神经元可以响应一部分覆盖范围内的周围单元,对于大型图像处理有出色表现。它主 要包括卷积层(convolutional layer)和池化层(pooling layer)。卷积神经网络已广泛应 用于图像分类、物体识别、目标追踪。 对于卷积神经网络的处理芯片,如何通过乘法器和加法器的排布、设计从而提高 乘法器资源的利用率,且根据不同的卷积核的尺寸实现不同的乘法器资源分配,实现数据 的动态分布,达到需要的计算方式,是本领域技术人员亟待解决的技术问题。

技术实现要素:

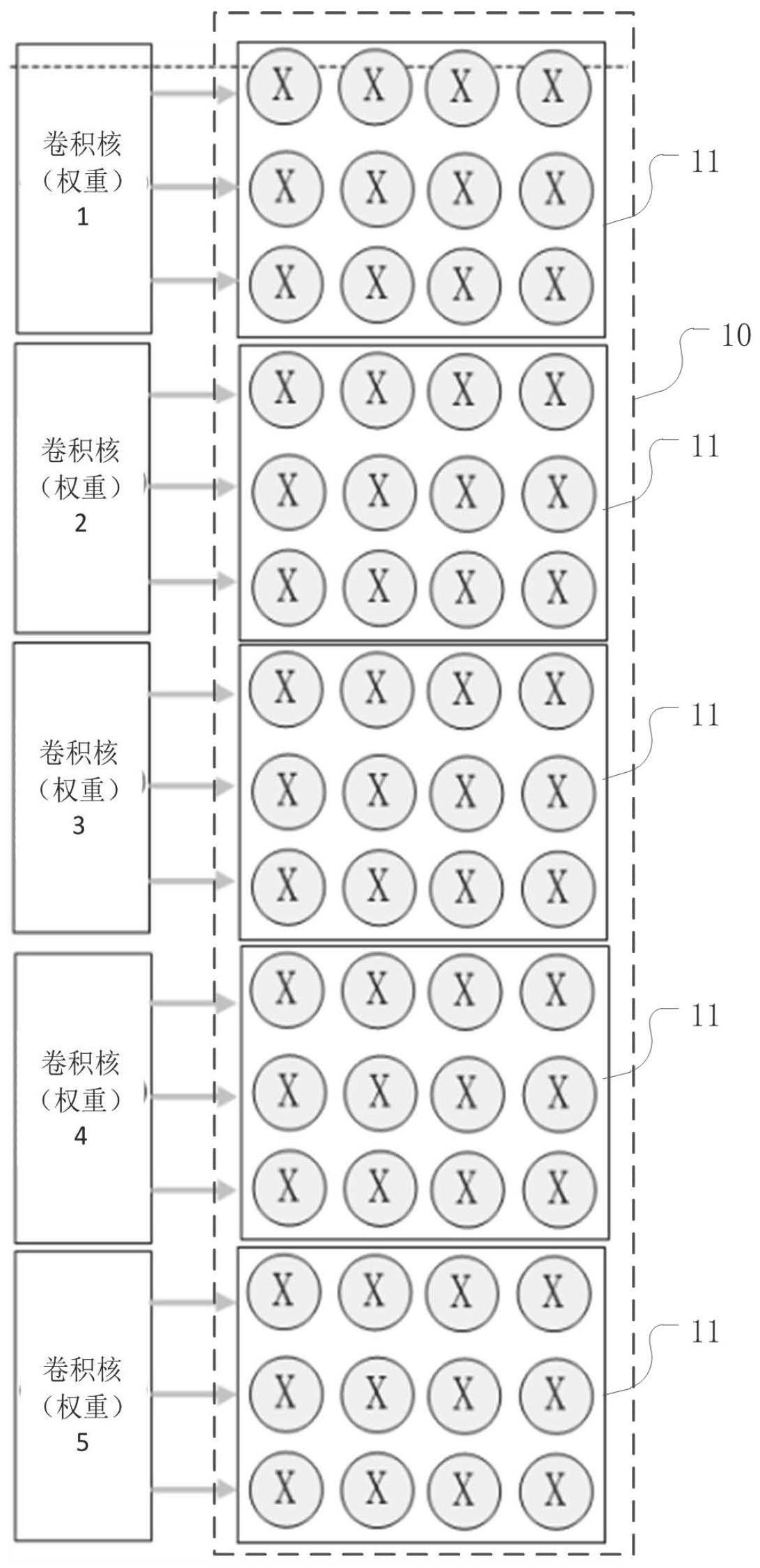

本发明为了克服上述现有技术存在的缺陷,提供一种芯片结构及其乘加计算引 擎,以利用同一套卷积引擎在应用到不同的卷积核的尺寸时,提高乘法器资源的利用率,且 根据不同的卷积核的尺寸实现不同的乘法器资源分配,实现数据的动态分布,达到需要的 计算方式。 根据本发明的一个方面,提供一种乘加计算引擎,包括: 多个卷积引擎,每个所述卷积引擎包括15*M*N个乘法器以及至少设置在部分乘法 器之间的加法器,N为大于1的整数,M为大于1的整数, 其中,根据所述卷积引擎所应用的不同的卷积核的尺寸,按不同的方式激活所述 乘法器之间、所述乘法器与所述加法器之间的连接方式。 在本发明的一些实施例中,多个所述卷积引擎对输入特征图和卷积核权重进行乘 法运算,并在输入特征通道将乘法结果进行累加以获得输出特征图。 在本发明的一些实施例中,每个所述卷积引擎在应用于卷积核时,按卷积核的尺 寸划分为多个卷积组,每个所述卷积组的乘法器的行数与所述卷积核的行数一致,每个所 述卷积组的乘法器的列数为N,以由所述卷积引擎提供在输出特征第一维度的N倍并行加 速,所述卷积引擎还提供在输入特征通道的M倍并行加速。 在本发明的一些实施例中,对于步长S为1、尺寸为P*Q的卷积核,每个所述卷积组 包括P*N个乘法器,每列乘法器的相邻两个乘法器之间连接有加法器,每个所述卷积组并行 读取(P N-1)行输入特征图,每个卷积组并行读取P行卷积核权重,其中,所述P行卷积核权 重分别输入一行乘法器;所述(P N)行输入特征图中第1至第P行分别输入一行乘法器,第P 1行至第N-1行分别输入一列乘法器,P、Q为大于1的整数; 对于步长S为2、尺寸为P*Q的卷积核,每个所述卷积组包括P*N个乘法器,每列乘法 器的相邻两个乘法器之间连接有加法器,每个所述卷积组并行读取[S*N (P-S)]行输入特 征图。 4 CN 111610963 A 说 明 书 2/7 页 在本发明的一些实施例中,由所述卷积引擎组成多组级联结构,每组级联结构包 括M/2个级联的处理单元,每个处理单元包括第一输入接口至第五输入接口、第一触发器至 第五触发器、两个乘法器以及两个加法器、一输出接口、第一时钟信号至第五时钟信号,其 中,每个处理单元: 第一输入接口至第四输入接口分别连接至第一触发器及第四触发器; 第一时钟信号至第四时钟信号分别连接至第一触发器及第四触发器; 第一触发器和第二触发器的输出连接至一乘法器; 第三触发器和第四触发器的输出连接至另一乘法器 两个乘法器的输出连接至一加法器,且该加法器的输出连接至另一加法器; 第五输入接口将前一处理单元的输出接口的数据连接至另一加法器; 另一加法器的输出连接至第五触发器; 第五时钟信号连接至第五触发器; 第五触发器的输出连接至该处理单元的输出接口, 所述第一时钟信号至第五时钟信号分别用于开启第一触发器至第五触发器。 在本发明的一些实施例中,同一处理单元的第一时钟信号至第五时钟信号相同; 在级联中,间隔(N/2-1)个处理单元的前一处理单元的时钟信号比后一处理单元的时钟信 号早N/2个时钟周期,N为2的倍数。 在本发明的一些实施例中,对于尺寸为P*Q的卷积核,所述卷积引擎组成P组级联 结构。 在本发明的一些实施例中,N为4。 在本发明的一些实施例中,M为16。 根据本发明的又一方面,还提供一种芯片结构,包括如上所述的乘加计算引擎。 相比现有技术,本发明的优势在于: 利用同一套卷积引擎在应用到不同的卷积核的尺寸时,提高乘法器资源的利用 率,且根据不同的卷积核的尺寸实现不同的乘法器资源分配,实现数据的动态分布,达到需 要的计算方式。 附图说明 通过参照附图详细描述其示例实施方式,本发明的上述和其它特征及优点将变得 更加明显。 图1示出了根据本发明实施例的卷积引擎应用于尺寸为3*3的卷积核的示意图; 图2示出了根据本发明实施例的卷积引擎应用于尺寸为5*5的卷积核的示意图; 图3示出了根据本发明实施例的卷积引擎应用于尺寸为7*7的卷积核的示意图; 图4示出了根据本发明实施例的应用于尺寸为5*5的卷积核的一卷积组的示意图; 图5示出了根据本发明实施例输入特征图进行卷积的示意图; 图6示出了根据本发明实施例输入特征图进行卷积后获得输出特征图的示意图; 图7示出了根据本发明实施例的卷积引擎的示意图; 图8示出了根据本发明实施例的处理单元的示意图; 图9示出了根据本发明实施例的级联结构的示意图; 5 CN 111610963 A 说 明 书 3/7 页 图10示出了图9的级联结构中的时钟信号的时序图。