技术摘要:

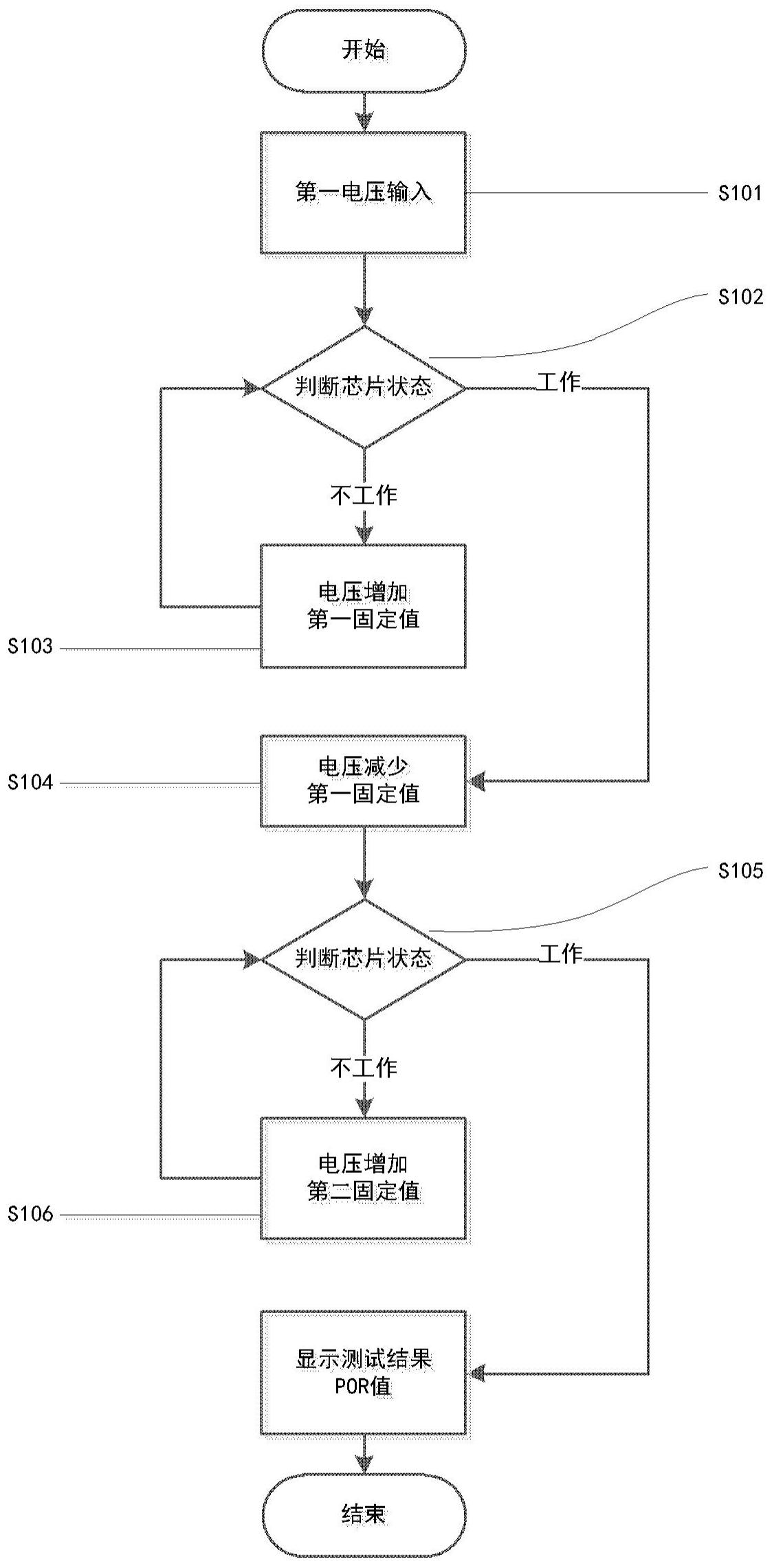

本发明提供一种芯片上电复位测试方法及装置,本方法包括:S101,将第一电压输入到芯片;S102,判断芯片是否工作,若是,执行步骤S104,否则,执行步骤S103;S103,将第一电压的电压值增加第一固定值,并执行步骤S102;S104,获取第一电压的电压值,并将该第一电压的电 全部

背景技术:

在芯片测试领域,上电和下电复位跳变点测试是必要的测试项目。上电和下电复 位跳变点测试,又称为上电复位跳变点测试(Power On Reset,POR)和下电复位跳变点测试 (Power Down Reset,PDR)。由于芯片制造工艺的差异,布局布线参数的差异等因素,都会导 致芯片的上电和下电复位跳变点,发生差异。 芯片低于正常工作的最低电压时,必须停止工作;芯片高于正常工作的最高电压 时,必须启动工作。未测试的芯片,在实际产品应用过程当中,由于跳变点的位移,导致上电 和下电复位跳变点,位移到不确定的状态;导致应用产品出错,加速芯片的老化和损坏,使 得芯片在实际产品应用当中,发生故障。 目前传统的上电和下电复位跳变点测试,需要借助专业的测试机台,这种方法价 格昂贵,测试成本高。传统上电和下电复位跳变点测试的方法,采用逐步增加施加芯片电源 的电压值,或者逐步减少电压值;在每个电压值状态下,检测芯片是否工作,这种方法测试 时间很长。在芯片研发阶段,需要尽快得到芯片的上电和下电复位跳变点测试信息,用于分 析和优化芯片的制程工艺、封装方式,加快芯片研发速度。

技术实现要素:

(一)要解决的技术问题 针对上述问题,本发明提供了一种芯片上电和下电复位测试方法及装置,用于至 少部分解决传统测试方法效率低、测试成本高、测试时间长等技术问题。 (二)技术方案 本发明一方面提供了一种芯片上电复位测试方法,包括:S101,将第一电压输入到 芯片;S102,判断芯片是否工作,若是,执行步骤S104,否则,执行步骤S103;S103,将第一电 压的电压值增加第一固定值,并执行步骤S102;S104,获取第一电压的电压值,并将该第一 电压的电压值减少第一固定值;S105,判断芯片是否工作,若否,执行步骤S106,若是,则将 第一电压的电压值作为芯片的上电复位值;S106,将第一电压的电压值增加第二固定值,并 执行S105,其中,第二固定值小于第一固定值。 进一步地,S103或S106至少循环操作一次,否则需重新设定第一电压的电压值。 进一步地,采用一测试装置将第一电压输入到芯片,其中,测试装置包括一电位 器,通过改变电位器的阻值以调节第一电压的电压值。 本发明另一方面提供了一种芯片下电复位测试方法,包括:S201,将第二电压输入 到芯片;S202,判断芯片是否工作,若否,执行步骤S204,若是,执行步骤S203;S203,将第二 电压的电压值减少第一固定值,并执行步骤S202;S204,获取第二电压的电压值,并将该第 4 CN 111610433 A 说 明 书 2/6 页 二电压的电压值增加第一固定值;S205,判断芯片是否工作,若是,执行步骤S206,若否,则 将第二电压的电压值作为芯片的下电复位值;S206,将第二电压的电压值减少第二固定值, 并执行S205,其中,第二固定值小于第一固定值。 进一步地,S203或S206至少循环操作一次,否则需重新设定第一电压的电压值。 进一步地,采用一测试装置将第二电压输入到芯片,其中,测试装置包括一电位 器,通过改变电位器的阻值以调节第二电压的电压值。 进一步地,S201中第二电压的初始电压值为芯片上电复位测试得到的上电复位 值。 本发明还有一方面提供了一种芯片上电和下电复位测试装置,包括:稳压器,用于 输出电压;电位器,用于调节稳压器模块的输出电压;控制器,用于实时监控稳压器模块输 出的电压值并调节电位器模块的阻值以控制输出电压值。 进一步地,芯片上电和下电复位测试装置包含一测试电路,其特征在于,稳压器的 反馈引脚与电位器的引脚相连、输出电压引脚与待测芯片的电源引脚相连、输出电压引脚 同时与控制器的引脚相连;控制器的通用输入输出管脚与稳压器的使能引脚相连,控制输 出电压的打开和关闭状态;电位器的串行时钟引脚和串行数据引脚与控制器的引脚相连。 进一步地,芯片上电和下电复位测试装置还包括:外部电阻,用于与电位器模块内 部电阻,共同构成稳压器模块的反馈电路;输入电源,用于给控制器模块、稳压器模块、电位 器模块供电;显示器,用于显示测试信息和测试结果;至少一个电容,用于过滤电源的噪声。 (三)有益效果 本发明实施例提供的一种芯片上电和下电复位测试方法及装置,通过给第一电压 的电压值增加第一固定值、判断芯片是否工作的第一次循环操作的粗略调节方式,以及给 第一电压的电压值增加第二固定值、判断芯片是否工作的第二次循环操作的精细调节方 式,缩短了芯片上电和下电的测试时间、降低了芯片上电和下电的测试成本。 附图说明 图1示意性示出了根据本发明实施例芯片上电复位测试方法的流程图; 图2示意性示出了根据本发明实施例芯片上电复位测试方法的操作流程图; 图3示意性示出了根据本发明实施例芯片上电复位测试方法的测试数据表; 图4示意性示出了根据本发明实施例芯片下电复位测试方法的流程图; 图5示意性示出了根据本发明实施例芯片下电复位测试方法的操作流程图; 图6示意性示出了根据本发明实施例芯片上电和下电复位测试装置结构示意图; 图7示意性示出了根据本发明实施例芯片上电和下电复位测试装置的测试电路 图。