技术摘要:

本发明实施例公开了一种测量电路及其测量方法,所述测量电路包括:环路振荡电路以及与所述环路振荡电路耦接的周期测量电路;环路振荡电路包括振荡控制电路以及多级振荡单元电路,第一级振荡单元电路的输入端耦接至振荡控制电路的输出端,振荡控制电路的输入端耦接至前 全部

背景技术:

在芯片设计中,延迟时间是衡量电子器件最为重要的电参数之一。由于电子工艺 偏差的存在,芯片上的电子器件的延迟时间有所不同,因此,需要对电子器件的延迟时间进 行测量。同时,在芯片上,固定区域内部的多个相同类型的电子器件也可能存在延迟时间的 差异,对所述固定区域内部的相同类型的电子器件之间的延迟时间的偏差进行检测也十分 重要。 现有技术中,为了降低待测器件延迟的测量难度,一般采用环路振荡器(Ring Oscillator,RO)对待测器件的延迟进行测量。 现有测量电路中,测量待测器件的延迟的精确度有待提升。

技术实现要素:

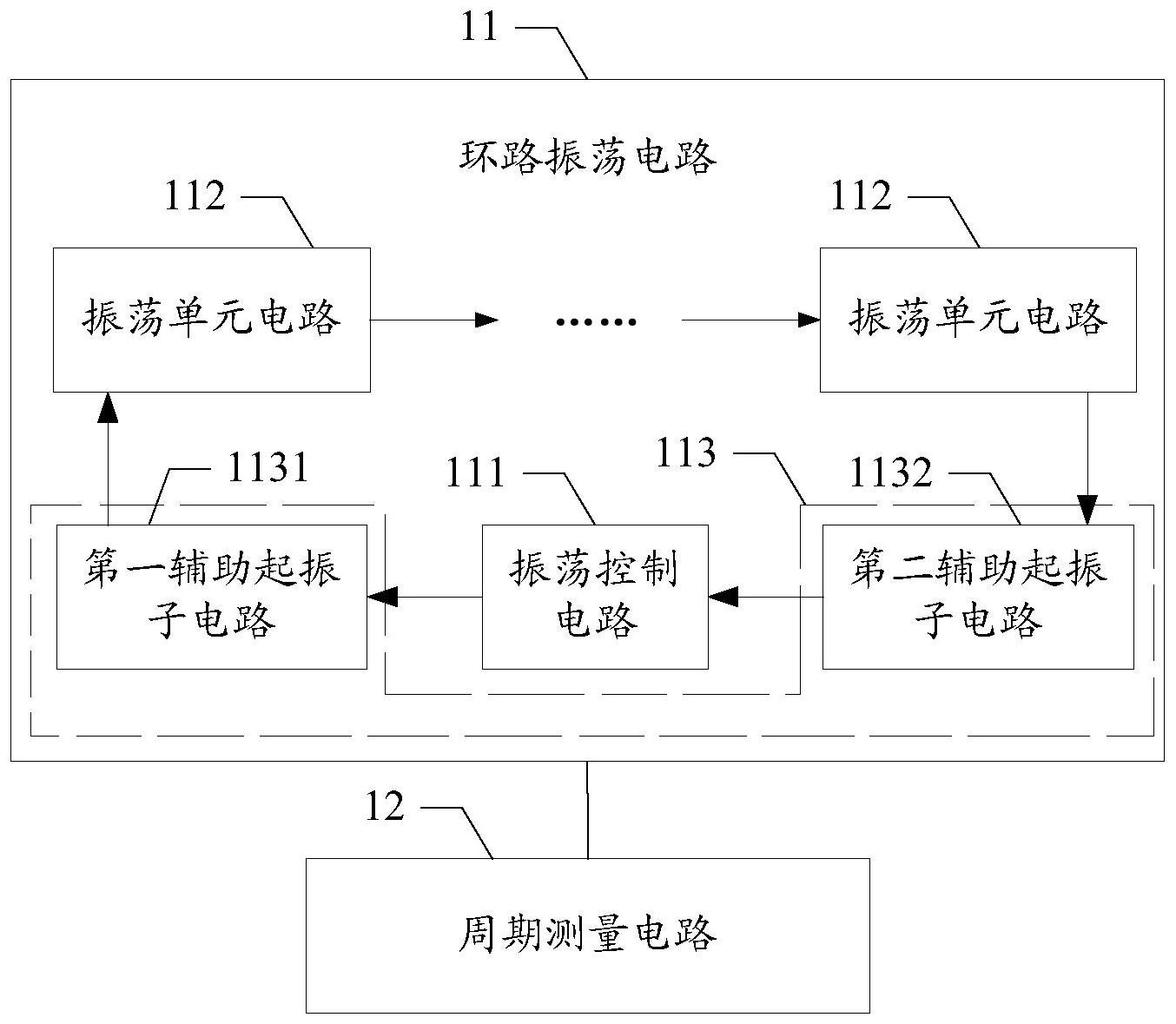

本发明实施例解决的技术问题是提升测量电路测量待测器件的延迟的精确度。 为解决上述技术问题,本发明实施例提供一种测量电路,包括:环路振荡电路以及 与所述环路振荡电路耦接的周期测量电路;其中:所述环路振荡电路包括振荡控制电路以 及多级振荡单元电路,第一级所述振荡单元电路的输入端耦接至所述振荡控制电路的输出 端,所述振荡控制电路的输入端耦接至前一级所述振荡单元电路的输出端,所述振荡控制 电路以及多级所述振荡单元电路构成环路;所述振荡单元电路包括第一数据选择电路、待 测元件、第二数据选择电路,所述第一数据选择电路的电路结构与所述第二数据选择电路 的电路结构基于所述待测元件对称,所述第一数据选择电路的第一输出端耦接至所述第二 数据选择电路的第一输入端,所述第一数据选择电路的第二输出端耦接至所述待测元件的 输入端,所述待测元件的输出端耦接至所述第二数据选择电路的第二输入端,所述第二数 据选择电路的第一输出端以及第二输出端耦接至后一级所述振荡单元电路的输入端,所述 第一数据选择电路以及所述第二数据选择电路适于在数据选择控制信号的作用下,控制振 荡信号通过或跳过所述待测元件;所述周期测量电路适于测量所述环路振荡电路的振荡周 期,并根据所述环路振荡电路的振荡周期得到所述待测元件的延迟;所述环路振荡电路适 于在所述振荡控制电路的控制端接收的振荡控制信号以及所述数据选择电路的控制端接 收的所述数据选择控制信号的作用下,满足起振条件。 可选的,所述第一数据选择电路包括第一数据分配器、第二数据分配器、第一数据 选择器、第二数据选择器,所述第二数据选择电路包括第三数据分配器、第四数据分配器、 第三数据选择器、第四数据选择器;所述第一数据分配器的第一输出端耦接至所述第一数 据选择器的第二输入端,所述第一数据分配器的第二输出端耦接至所述第二数据选择器的 第一输入端;所述第二数据分配器的第一输出端耦接至所述第二数据选择器的第二输入 端;所述第一数据选择器的输出端作为所述第一数据选择电路的所述第一输出端;所述第 5 CN 111596192 A 说 明 书 2/10 页 二数据选择器的输出端作为所述第一数据选择电路的所述第二输出端;所述第三数据分配 器的第二输出端耦接至所述第三数据选择器的第一输入端;所述第四数据分配器的第一输 出端耦接至所述第三数据选择器的第二输入端,所述第四数据分配器的第二输出端耦接至 所述第四数据选择器的第一输入端;所述第三数据选择器的输入端作为所述第二数据选择 电路的所述第一输入端;所述第四数据选择器的输入端作为所述第二数据选择电路的所述 第二输入端。 可选的,所述振荡单元电路还包括第一反向型电路器件,所述第一反向型电路器 件的输入端耦接至所述第二数据选择电路的第一输出端,所述第一反向型电路器件的输出 端耦接至后一级所述振荡单元电路的输入端。 可选的,还包括:译码器,所述译码器的输出端连接至所述数据选择电路的控制 端,适于基于接收的选择信号,生成用于控制所述数据选择电路的所述控制信号。 可选的,所述待测元件包括第二反向型电路器件。 可选的,多级振荡单元电路包括偶数个所述振荡单元电路,所述第一数据选择电 路以及所述第二数据选择电路适于在数据选择控制信号的作用下,控制所述振荡信号跳过 或通过偶数个所述反向型电路器件。 可选的,还包括:辅助起振电路,串联于所述环路振荡电路中,适于辅助所述环路 振荡电路中的振荡单元电路中的待测元件串联形成的所述环路满足所述环路振荡电路的 起振条件。 可选的,所述辅助起振电路包括第一辅助起振子电路和第二辅助起振子电路;所 述第一辅助起振子电路包括:第三数据选择电路、第三反向型电路器件;所述第二辅助起振 子电路包括:第四数据选择电路、第四反向型电路器件;所述第三数据选择电路的输入端耦 接至所述振荡控制电路的输出端,所述第三数据选择电路的第一输出端耦接至所述第三反 向型电路器件的输入端,所述第三反向型电路器件的输出端以及所述第三数据选择电路的 第二输出端耦接至后一级所述振荡单元电路的输入端;所述第四数据选择电路的输出端耦 接至所述第四反向型电路器件的输入端,所述第四反向型电路器件的输出端耦接至所述振 荡控制电路的输入端;在所述第三数据选择电路的控制端控制信号为低电平信号,所述第 四数据选择电路的控制端控制信号为高电平信号时,通过所述第三数据选择电路的振荡信 号通过所述第三反向型电路器件接入后一级所述振荡单元电路,通过所述第四数据选择电 路的振荡信号通过所述第四反向型电路器件接入所述振荡控制电路的输入端。 本发明实施例还提供了一种基于权利要求上述任一项所述测量电路的测量方法, 包括:控制环路振荡电路的振荡信号通过或跳过待测元件,在振荡控制电路接收的振荡控 制信号作用下,使所述环路振荡电路满足起振条件;测量所述环路振荡电路的振荡周期,并 根据所述环路振荡电路的振荡周期得到所述待测元件的延迟变化量。 可选的,所述环路振荡电路包括偶数个所述振荡单元电路,所述控制环路振荡电 路的振荡信号通过或跳过待测元件,在振荡控制电路接收的振荡控制信号作用下,使所述 环路振荡电路满足起振条件包括:控制所述振荡信号跳过偶数个所述振荡单元电路的待测 元件。 可选的,所述控制所述振荡信号跳过偶数个所述振荡单元电路的待测元件包括: 控制所述振荡信号通过第i级所述振荡单元电路、第i 1级所述振荡单元电路、第i 2级所述 6 CN 111596192 A 说 明 书 3/10 页 振荡单元电路的所述待测元件,所述环路振荡电路的所述振荡周期为T0;控制所述振荡信 号通过第i级所述振荡单元电路的所述待测元件,跳过所述第i 1级所述振荡单元电路以及 第i 2级所述振荡单元电路的所述待测元件,所述环路振荡电路的所述振荡周期为T1;控制 所述振荡信号通过第i 1级所述振荡单元电路的所述待测元件,跳过所述第i级所述振荡单 元电路以及第i 2级所述振荡单元电路的所述待测元件,所述环路振荡电路的所述振荡周 期为T2;控制所述振荡信号通过第i 2级所述振荡单元电路的所述待测元件,跳过所述第i 级所述振荡单元电路以及第i 1级所述振荡单元电路的所述待测元件,所述环路振荡电路 的所述振荡周期为T3;其中,i为大于0的整数。 可选的,所述测量所述环路振荡电路的振荡周期,并根据所述环路振荡电路的振 荡周期得到所述待测元件的延迟变化量包括:测量所述T0、T1、T2以及T3;根据公式(T0-T2- T3 T1)/2计算第i级所述振荡单元电路中的所述待测元件的延迟变化量;根据公式(T0-T1- T3 T2)/2计算第i 1级所述振荡单元电路中的所述待测元件的延迟变化量;根据公式(T0- T1-T2 T3)/2计算第i 2级所述振荡单元电路中的所述待测元件的延迟变化量。 与现有技术相比,本发明实施例的技术方案具有以下有益效果: 在本发明实施例中,通过设置振荡控制电路以及多级振荡单元电路,所述振荡单 元电路包括第一数据选择电路、待测元件以及第二数据选择电路,所述第一数据选择电路 的电路结构与所述第二数据选择电路的电路结构基于所述待测元件对称,使所述第一数据 选择电路的第一输出端耦接至所述第二数据选择电路的第一输入端,所述第一数据选择电 路的第二输出端耦接至所述待测元件的输入端,所述待测元件的输出端耦接至所述第二数 据选择电路的第二输入端,所述第二数据选择电路的第一输出端以及第二输出端耦接至后 一级所述振荡单元电路的输入端,并通过所述周期测量电路测量所述环路振荡电路的振荡 周期,得到所述待测元件的延迟。从而,第一数据选择电路与第二数据选择电路的电路结构 对称,可以使第一数据选择电路的电路结构对电路信号的影响通过第二数据选择电路抵 消,可以提升测量通过第一数据选择单元、待测元件以及第二数据选择单元构成的所述环 路振荡电路得到的振荡周期的准确性,进而可以提升测量得到的所述待测元件的延迟的精 确度。 进一步,通过将数据分配器的输出端与数据选择器的输入端耦接,数据选择器的 输出端与数据分配器的输入端耦接,可以使数据分配器或者数据选择器的输出端端口对振 荡信号的影响可以通过与之耦接的数据选择器或者数据分配器的输入端端口抵消,从而可 以降低电路端口对振荡信号的影响,进而可以提升振荡信号的稳定性,可以提升检测得到 的振荡周期的精确度,可以提升测量得到的所述待测元件的延迟的精确度。 进一步,通过多次测量跳过偶数个待测元件的振荡周期,并基于多次测量的振荡 周期计算跳过的待测元件的延迟,从而可以准确得到待测元件的延迟,提升测量得到的待 测元件的延迟的精确度。 附图说明 图1是本发明实施例中一种测量电路的结构示意图; 图2是本发明实施例中一种振荡单元电路的结构示意图; 图3是本发明一具体实施中振荡单元电路的结构示意图; 7 CN 111596192 A 说 明 书 4/10 页 图4是本发明一具体实施例中测量电路的结构示意图; 图5是本发明实施例中一种测量方法的流程图; 图6是本发明实施例中一种测量振荡周期的方法的流程图; 图7~图10是本发明一具体实施例中振荡信号通过振荡单元电路的路径的示意 图; 图11是本发明实施例中一种计算延迟变化量的方法的流程图。