技术摘要:

本发明实施例提供了一种基于CFFH/DS系统的帧同步方法及装置,所述方法将现有技术中分别进行的精搜索、跟踪及帧同步同时进行,可以大大缩短同步时间,实现快速的帧同步,同时避免消耗大量硬件资源。

背景技术:

目前,扩频技术是将传输信号的频谱用某个特定的扩频函数进行展宽以提高通信 系统的可靠性,常用的扩频技术包括直接序列扩频、跳频扩频、跳时及混合扩频等。 单一的直接序列具有扩频增益受限、远近效应严重、抗窄带干扰和对准式干扰能 力差等缺点,混合扩频是多种扩频技术结合在一起的扩频方式,例如结合了直接序列扩频 (Direct Sequence-Spread Spectrum,DS)技术与相干快跳频(Coherent Fast Frequency Hopping,CFFH)技术的混合扩频技术,基于这种混合扩频技术形成的通信系统为相干快跳 频/直接序列扩频混合系统(以下简称为CFFH/DS系统)。CFFH/DS系统结合了直接序列扩频 技术与跳频技术的特点,可以显著提高系统的信号处理增益,并且能有效的克服远近效应, 提高抗窄带干扰的能力,具有极强的抗干扰性和低检测概率,在军事通信中有着极为广泛 的运用。 CFFH/DS系统能正常通信的前提是能够成功进行捕获、精搜索、跟踪和帧同步。在 传统的CFFH/DS系统中,通常将捕获、精搜索、跟踪和帧同步四个过程分别进行,由于这四个 过程均需要占用帧同步头的资源,这将会导致一帧中的帧同步头过长,使同步时间较长,这 将严重影响帧效率和CFFH/DS系统的接收机开启时间。

技术实现要素:

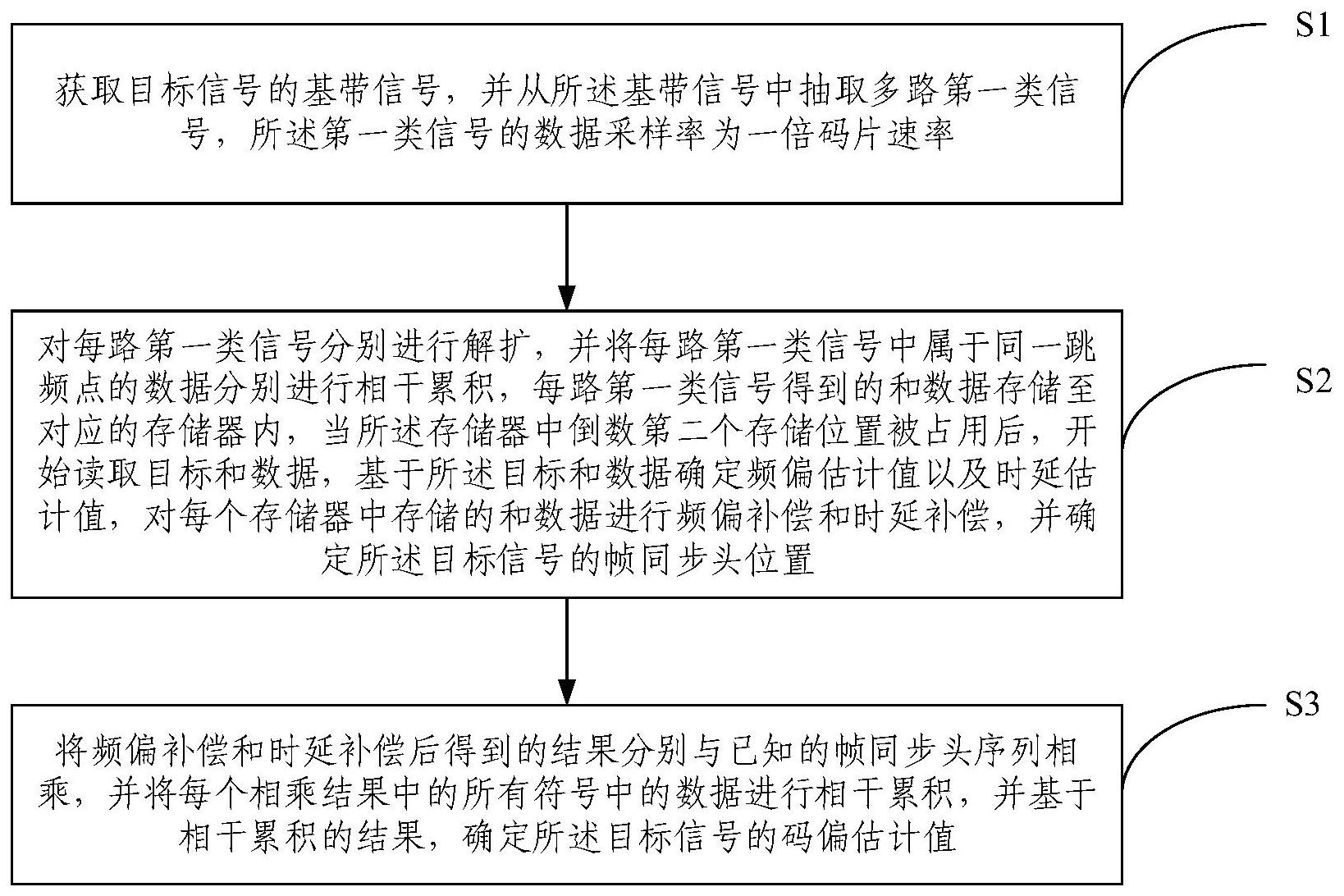

为克服上述问题或者至少部分地解决上述问题,本发明实施例提供了一种基于 CFFH/DS系统的帧同步方法及装置。 第一方面,本发明实施例提供了一种基于CFFH/DS系统的帧同步方法,包括: 获取目标信号的基带信号,并从所述基带信号中抽取多路第一类信号,所述第一 类信号的数据采样率为一倍码片速率; 对每路第一类信号分别进行解扩,并将每路第一类信号中属于同一跳频点的数据 分别进行相干累积,每路第一类信号得到的和数据存储至对应的存储器内,当所述存储器 中倒数第二个存储位置被占用后,开始读取目标和数据,基于所述目标和数据确定频偏估 计值以及时延估计值,对每个存储器中存储的和数据进行频偏补偿和时延补偿,并确定所 述目标信号的帧同步头位置;所述目标和数据为目标第一类信号对应的存储器中存储的和 数据; 将频偏补偿和时延补偿后得到的结果分别与已知的帧同步头序列相乘,并将每个 相乘结果中的所有符号中的数据进行相干累积,并基于相干累积的结果,确定所述目标信 号的码偏估计值。 优选地,所述基于所述目标和数据确定频偏估计值以及时延估计值,对每个存储 4 CN 111585611 A 说 明 书 2/12 页 器中存储的和数据进行频偏补偿和时延补偿,并确定所述目标信号的帧同步头位置,具体 包括: 构建频偏补偿矩阵,基于所述频偏补偿矩阵,对所述目标和数据进行第一轮残余 频偏搜索,并基于第一轮残余频偏搜索的结果对所述目标和数据进行第一轮时延搜索,确 定时延和频偏的第一类二维搜索平面; 基于所述第一类二维搜索平面,确定第一轮频偏估计值以及第一轮时延估计值, 并确定所述目标信号的帧同步头位置; 确定所述帧同步头位置后,基于所述第一轮频偏估计值以及所述第一轮时延估计 值,对每个存储器中存储的和数据进行第一轮频偏补偿和第一轮时延补偿。 优选地,所述基于所述目标和数据确定频偏估计值以及时延估计值,对每个存储 器中存储的和数据进行频偏补偿和时延补偿,还包括: 对所述目标和数据经第一轮频偏补偿和第一轮时延补偿的结果进行第二轮残余 频偏搜索,并基于第二轮残余频偏搜索的结果进行第二轮时延搜索,确定时延和频偏的第 二类二维搜索平面; 基于所述第二类二维搜索平面,确定第二轮频偏估计值以及第二轮时延估计值; 基于所述第二轮频偏估计值以及所述第二轮时延估计值,分别对每个存储器中存 储的和数据进行第二轮频偏补偿和第二轮时延补偿。 优选地,所述基于所述频偏补偿矩阵,对所述目标和数据进行第一轮残余频偏搜 索,并基于第一轮残余频偏搜索的结果对所述目标和数据进行第一轮时延搜索,具体包括: 将所述目标和数据中的每个符号分别与所述频偏补偿矩阵相乘,对所述目标和数 据中的每个符号进行频偏补偿,并将频偏补偿的结果与所述已知的帧同步头序列相乘,将 相乘的结果按照跳频点进行相干累积; 将相干累积的结果按频点补偿不同的时延,对所述目标和数据进行所述第一轮时 延搜索。 优选地,所述基于所述第一类二维搜索平面,确定第一轮频偏估计值以及第一轮 时延估计值,并确定所述目标信号的帧同步头,具体包括: 将所述第一类二维搜索平面上的数据进行取模,将最大的模与预设门限值进行比 较,若判断获知最大的模大于所述预设门限值,则确定所述目标和数据为所述目标信号的 帧同步头,并确定所述目标信号的帧同步头位置,且根据最大的模对应的所述第一类二维 搜索平面的横坐标和纵坐标,确定所述第一轮频偏估计值以及所述第一轮时延估计值。 优选地,基于CFFH/DS系统的帧同步方法,还包括: 若判断获知最大的模小于等于所述预设门限值,则更新所述目标和数据的读取位 置,并基于更新后的读取位置,读取所述目标第一类信号对应的存储器中存储的目标和数 据。 优选地,所述目标第一类信号基于如下方法确定: 将所有第一类信号按抽取位置的先后顺序进行排序; 选取排序结果中处于中间位置的抽取位置对应的第一类信号作为所述目标第一 类信号。 第二方面,本发明实施例提供了一种基于CFFH/DS系统的帧同步装置,包括:抽取 5 CN 111585611 A 说 明 书 3/12 页 模块、帧同步头确定模块和码偏估计值确定模块。 其中, 抽取模块用于获取目标信号的基带信号,并从所述基带信号中抽取多路第一类信 号,所述第一类信号的数据采样率为一倍码片速率; 帧同步头确定模块用于对每路第一类信号分别进行解扩,并将每路第一类信号中 属于同一跳频点的数据分别进行相干累积,每路第一类信号得到的和数据存储至对应的存 储器内,当所述存储器中倒数第二个存储位置被占用后,读取目标和数据,基于所述目标和 数据确定频偏估计值以及时延估计值,对每个存储器中存储的和数据进行频偏补偿和时延 补偿,并确定所述目标信号的帧同步头;所述目标和数据为目标第一类信号对应的存储器 中存储的和数据; 码偏估计值确定模块用于将频偏补偿和时延补偿后得到的结果分别与已知的帧 同步头序列相乘,并将每个相乘结果中的所有符号中的数据进行相干累积,并基于相干累 积的结果,确定所述目标信号的码偏估计值。 第三方面,本发明实施例提供了一种电子设备,包括:存储器、处理器以及存储在 存储器上并可在处理器上运行的计算机程序,所述处理器执行所述程序时实现如第一方面 所述的基于CFFH/DS系统的帧同步方法的步骤。 第四方面,本发明实施例提供了一种非暂态计算机可读存储介质,其上存储有计 算机程序,该计算机程序被处理器执行时实现如第一方面所述的基于CFFH/DS系统的帧同 步方法的步骤。 本发明实施例提供的一种基于CFFH/DS系统的帧同步方法及装置,所述方法首先 获取目标信号的基带信号,并从所述基带信号中抽取多路第一类信号,所述第一类信号的 数据采样率为一倍码片速率;然后对每路第一类信号分别进行解扩,并将每路第一类信号 中的数据分别按跳频点进行相干累积,每路第一类信号得到的和数据存储至对应的存储器 内,当所述存储器中倒数第二个存储位置被占用后,读取目标第一类信号对应的存储器中 存储的目标和数据,基于所述目标和数据确定频偏估计值时延估计值,对每个存储器中存 储的和数据进行频偏补偿和时延补偿,并确定所述目标信号的帧同步头;最后将频偏补偿 和时延补偿后得到的结果分别与接收端已知的帧同步头序列相乘,并将每个相乘结果中的 所有符号中的数据进行相干累积,并基于相干累积的结果,确定所述目标信号的码偏估计 值。本发明实施例中将现有技术中分别进行的精搜索、跟踪及帧同步同时进行,可以大大缩 短同步时间,实现快速的帧同步,同时避免消耗大量硬件资源。 附图说明 为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现 有技术描述中所需要使用的附图作一简单地介绍,显而易见地,下面描述中的附图是本发 明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根 据这些附图获得其他的附图。 图1为本发明实施例提供的一种基于CFFH/DS系统的帧同步方法的流程示意图; 图2为本发明实施例提供的一种基于CFFH/DS系统的帧同步方法中对基带信号进 行采样的示意图; 6 CN 111585611 A 说 明 书 4/12 页 图3为本发明实施例提供的一种基于CFFH/DS系统的帧同步方法的完整流程示意 图; 图4为本发明实施例提供的一种基于CFFH/DS系统的帧同步装置的结构示意图; 图5为本发明实施例提供的一种电子设备的结构示意图。