技术摘要:

分离的三维纵向存储器(3D‑MV)50含有一三维阵列芯片30和一周边电路芯片40/60。三维阵列芯片30含有多个3D‑MV阵列,每个3D‑MV阵列含有多个竖直存储串。3D‑MV阵列的一周边电路位于周边电路芯片40/60内,而非三维阵列芯片30内。在垂直于芯片30方向上竖直存储串16X所含 全部

背景技术:

三维纵向存储器(three-dimensional vertical memory,简称为3D-MV)是一种单 体(monolithic)半导体存储器,它含有多个竖直存储串。3D-MV包括三维只读存储器(3D- ROM)和三维随机读取存储器(3D-RAM)。3D-ROM可以进一步划分为三维掩膜编程只读存储器 (3D-MPROM)和三维电编程只读存储器(3D-EPROM)。基于其编程机制,3D-MV可以含有 memristor、resistive random-access memory(RRAM或ReRAM)、phase-change memory (PCM)、programmable metallization memory(PMM)、或conductive-bridging random- access memory(CBRAM)等。 美国专利8,638,611披露了一种3D-MV,它是一种纵向NAND(vertical NAND)。如图 1所示,该3D-MV芯片20V含有至少一3D-MV阵列16V和周边电路18。3D-MV阵列16V含有多个竖 直的存储串16X、16Y。每个存储串(如16X)含有多个垂直堆叠的存储元(如8a-8h)。这些存储 元通过一条竖直地址线相互耦合。每个存储元(如8f)含有一个纵向晶体管,该纵向晶体管 含有栅极6、存储膜7和纵向沟道9。周边电路18含有晶体管0t及其互连线0i。晶体管0t形成 在半导体衬底0中,它是传统的平面型晶体管。互连线0i为晶体管0t实现相互连接。在图1 中,衬底互连线0i含有金属层0M1、0M2。 周边电路18为3D-MV阵列16V产生读/写电压和/或转换地址/数据。具体说来,它将 外界提供的电源电压转换成读电压和/或写电压,也可将外界的逻辑地址/数据转换成3D- MV阵列16V的物理地址/数据。现有技术的3D-MV是一种集成3D-MV,即3D-MV阵列16V及其周边 电路18集成在同一芯片20V内。也就是说,3D-MV芯片20V在内部产生读/写电压和/或转换地 址/数据。由于3D-MV的竖直存储串16X、16Y占用其下方的衬底0,周边电路18只能位于3D-MV 阵列16V之外。 现有技术的主流观点是:集成降低成本。不幸的是,该观点对3D-MV不成立。对于 3D-MV来说,由于竖直存储串16X、16Y采用了繁复的后端(BEOL)工艺,而周边电路18的后端 工艺较简单,因此盲目地将存储串16X、16Y和周边电路18集成的直接结果就是不得不用制 造存储串16X、16Y的昂贵工艺流程来制造周边电路18,这不仅不能降低成本,反而会增加成 本。

技术实现要素:

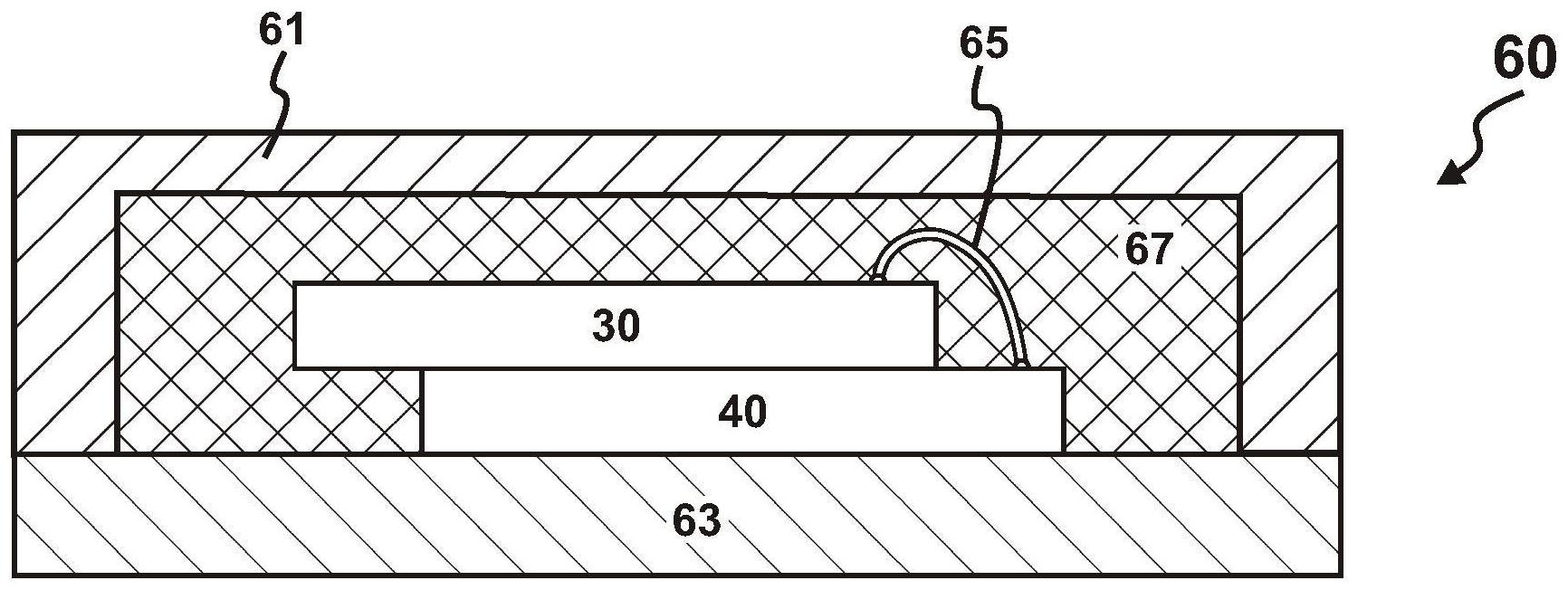

本发明的主要目的是提供一种更为廉价的三维纵向存储器(3D-MV)。 本发明的另一目的是提高3D-MV的阵列效率。 3 CN 111584490 A 说 明 书 2/4 页 为了实现这些以及别的目的,本发明遵从如下设计原则:将三维电路和二维电路 分离到不同芯片,以便将它们分别优化。为了提高三维阵列芯片的阵列效率,应尽量减少其 上的周边电路。例如说,可以将3D-MV的电压产生器分离到另外一个芯片中。相应地,本发明 提出一种分离3D-MV,它含有至少一三维阵列芯片和至少一电压产生器芯片。三维阵列芯片 (三维电路)构建在三维空间中并含有多个功能层,电压产生器芯片(二维电路)构建在二维 空间中并只含有一个功能层。由于电压产生器组件是实现3D-MV功能的必需组件,不含电压 产生器组件的三维阵列芯片本身不是一个能独立工作的存储芯片。分离3D-MV带来一个好 处:三维阵列芯片具有较高的阵列效率。 在分离3D-MV中,由于三维阵列芯片和电压产生器芯片可以分别设计和制造,它们 可以具有不同的后端(BEOL)结构:电压产生器芯片可以含有更少的后端薄膜。虽然三维阵 列芯片与集成3D-MV芯片的晶片成本相近,但由于电压产生器芯片可以采用独立的、廉价的 后端工艺流程来制造,其晶片成本较低。因此,对于相同的存储容量,分离3D-MV的总成本低 于集成3D-MV。 本发明提出一种分离3D-MV (50),其特征在于包括:一含有至少一3D-MV阵列(16V) 的三维阵列芯片(30),该3D-MV阵列(16V)含有多个竖直存储串(16X、16Y),每个竖直存储串 含有多个垂直堆叠的存储元(8a-8h);一含有至少部分电压产生器的电压产生器芯片(40), 该电压产生器为该三维阵列芯片(30)提供至少一与电源电压(VDD)不同的读电压(VR)和/或 写电压(VW);所述三维阵列芯片(30)不含所述部分电压产生器,所述三维阵列芯片(30)比 所述电压产生器芯片(40)含有更多的后端薄膜,所述三维阵列芯片(30)和所述电压产生器 芯片(40)为两个不同的芯片。 附图说明 图1是一种集成3D-MV芯片(现有技术)的截面图。 图2A是一种分离3D-MV的示意图,图2B是该分离3D-MV的电路框图。 图3是另一种分离3D-MV的示意图。 图4是一种分离3D-MV中三维阵列芯片的截面图。 图5是该分离3D-MV中电压产生器芯片的截面图。 图6A-图6C是三种电压产生器的电路图。 图7A-图7C是三种分离3D-MV的截面图。 注意到,这些附图仅是概要图,它们不按比例绘图。为了显眼和方便起见,图中的 部分尺寸和结构可能做了放大或缩小。在不同实施例中,相同的符号一般表示对应或类似 的结构。