技术摘要:

公开一种显示母板和显示基板的制作方法,显示母板包括:衬底,衬底包括:有效区以及位于有效区的至少一侧的边缘区,有效区包括:多个面板区和待切割区,待切割区将多个面板区彼此间隔开,并将边缘区与其相邻的面板区间隔开,面板区包括显示区和边框区;设置在衬底上的 全部

背景技术:

AMOLED(Active-matrix organic light emitting diode,有源矩阵有机发光二 极管)屏幕因其轻薄、对比度高、色域广等特点逐渐成为显示领域主流技术。在一些AMOLED 显示基板的生产过程中,会在有效显示区域之外设置虚拟像素的相关结构,例如,虚拟像素 电路和虚拟阳极。

技术实现要素:

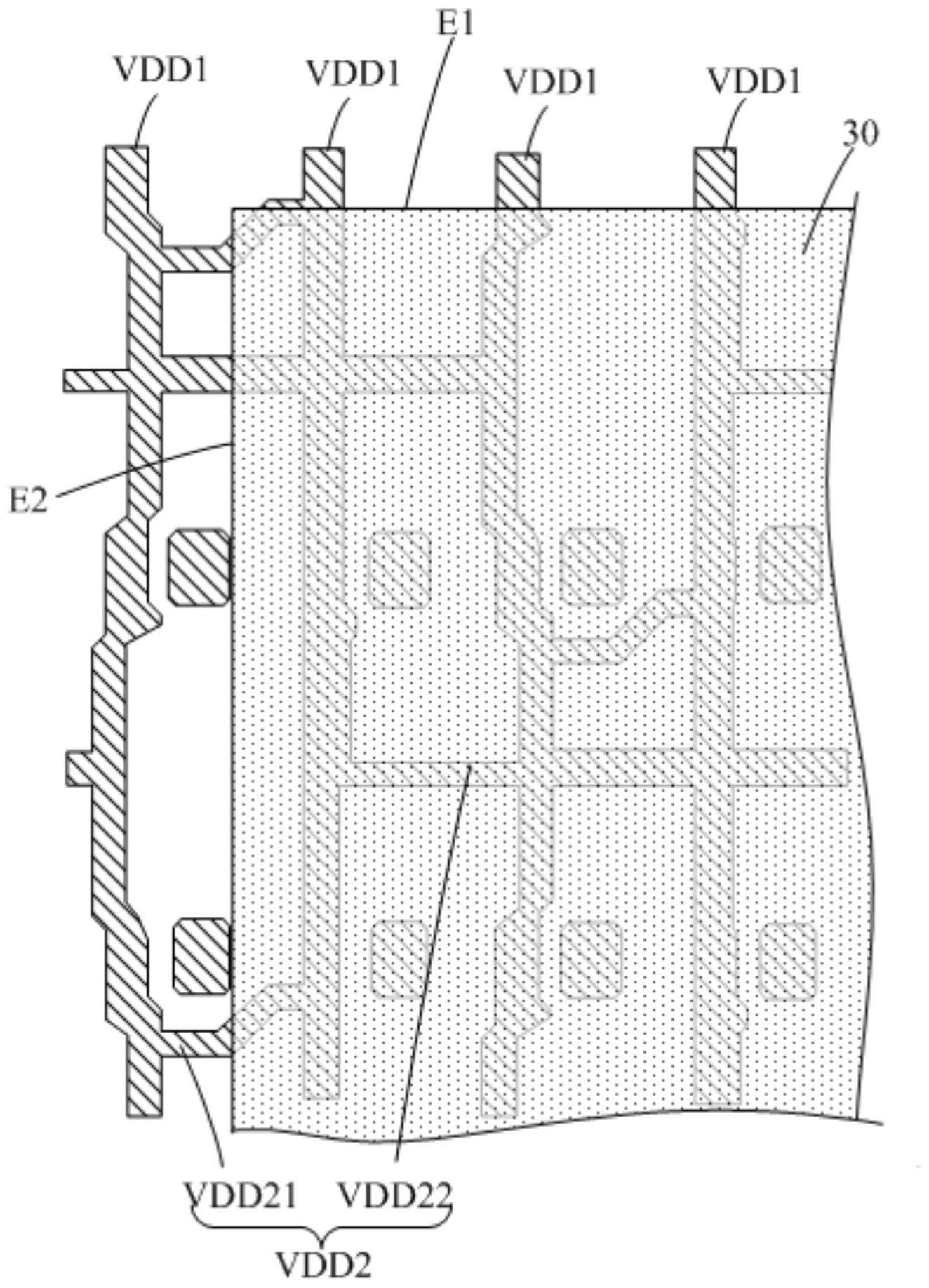

本公开实施例提供一种显示母板,包括: 衬底,所述衬底包括:有效区以及位于所述有效区的至少一侧的边缘区,所述有效 区包括:多个面板区和待切割区,所述待切割区将所述多个面板区彼此间隔开,并将所述边 缘区与其相邻的所述面板区间隔开,所述面板区包括显示区和环绕所述显示区的边框区; 设置在所述衬底上的多条第一电源线,每个所述显示区和所述边缘区均设置有多 条所述第一电源线;所述第一电源线沿第一方向延伸; 设置在每个所述显示区的多个第一显示电极和设置在所述边缘区的多个虚拟电 极,所述多个第一显示电极和所述多个虚拟电极同层设置; 其中,所述多个第一显示电极中的每个在所述衬底上的正投影与至多一条所述第 一电源线在所述衬底上的正投影存在交叠,所述多个虚拟电极中的每个在所述衬底上的正 投影与至少两条所述第一电源线在所述衬底上的正投影存在交叠。 在一些实施例中,每个所述虚拟电极在所述衬底上的正投影与3~40条所述第一 电源线在所述衬底上的正投影存在交叠, 在一些实施例中,所述虚拟电极在所述衬底上的正投影包括矩形。 在一些实施例中,任意两个所述虚拟电极之间具有间隔,相邻两个所述虚拟电极 之间的间隔宽度在5μm~15μm之间。 在一些实施例中,至少两个相邻的所述虚拟电极之间的间隔区域为沿所述第一方 向延伸的条形区域,所述条形区域在所述衬底上的正投影与任意一条所述第一电源线在所 述衬底上的正投影无交叠。 在一些实施例中,所述显示母板还包括:像素界定层,所述像素界定层包括: 位于所述显示区的第一像素界定部,所述第一像素界定部设置在所述第一显示电 极远离所述衬底的一侧,所述第一像素界定部具有多个像素开口,所述多个像素开口与所 述多个第一显示电极一一对应,所述多个像素开口中的每个暴露出相应的第一显示电极的 至少一部分; 位于所述边缘区的第二像素界定部,所述第二像素界定部设置在所述虚拟电极远 离所述衬底的一侧,所述第二像素界定部覆盖每个所述虚拟电极。 7 CN 111584757 A 说 明 书 2/15 页 在一些实施例中,所述显示母板还包括: 多个发光层,所述多个发光层一一对应地设置在所述多个像素开口中; 位于所述显示区的第二电极层,所述第二电极层设置在所述多个发光层远离所述 衬底的一侧。 在一些实施例中,所述显示母板还包括: 隔垫层,所述隔垫层包括位于所述显示区的第一隔垫物和位于所述边缘区的第二 隔垫物,所述第一隔垫物设置在所述第一像素界定部远离所述衬底的一侧,所述第二隔垫 物设置在所述第二像素界定部远离所述衬底的一侧。 在一些实施例中,每个所述第一隔垫物在所述衬底上的正投影与一条所述第一电 源线在所述衬底上的正投影存在交叠,每个所述第二隔垫物在衬底上的正投影与一条所述 第二电源线在所述衬底上的正投影存在交叠。 在一些实施例中,所述显示区中的第一隔垫物排成多行,所述第一显示电极在所 述衬底上的正投影与至多一个所述第一隔垫物在所述衬底上的正投影存在交叠; 所述边缘区中的第二隔垫物排成多行,所述虚拟电极在所述衬底上的正投影与分 别位于两行中的两个第二隔垫物在所述衬底上的正投影存在交叠。 在一些实施例中,所述显示母板还包括:位于所述显示区中的多个显示像素电路, 所述多个显示像素电路与所述多个第一显示电极一一对应地电连接, 所述第一显示电极包括主体部和连接部,所述连接部与所述显示像素电路电连 接,所述主体部在所述衬底上的正投影为五边形或六边形。 在一些实施例中,每个所述第一显示电极在所述衬底上的正投影与至多两个所述 显示像素电路在所述衬底上的正投影存在交叠。 在一些实施例中,所述显示像素电路包括显示发光控制晶体管,所述显示母板还 包括: 位于所述显示区和所述边缘区的第一平坦化层,所述第一平坦化层设置在所述显 示发光控制晶体管远离所述衬底的一侧; 位于所述显示区和所述边缘区的第二平坦化层,所述第二平坦化层位于所述第一 平坦化层远离所述衬底的一侧; 与所述第一显示电极一一对应连接的显示连接件,所述显示连接件设置在所述第 一平坦化层与所述第二平坦化层之间,所述第一显示电极的主体部位于所述第二平坦化层 背离所述衬底的表面,所述第一显示电极的连接部通过所述第二平坦化层上的过孔与相应 的显示连接件连接,所述显示连接件通过所述第一平坦化层上的过孔与所述显示发光控制 晶体管的漏极连接; 其中,所述虚拟电极设置在所述第二平坦化层背离所述衬底的表面。 在一些实施例中,所述显示母板还包括: 位于所述边缘区的多个虚拟像素电路,所述多个虚拟像素电路设置在所述衬底与 所述第一平坦化层之间,所述虚拟电极在所述衬底上的正投影覆盖所述多个虚拟像素电路 中的至少两个在所述衬底上的正投影。 在一些实施例中,所述多个虚拟像素电路中的每个包括多个虚拟晶体管,所述多 个虚拟晶体管包括虚拟复位晶体管,每个所述虚拟晶体管包括有源层, 8 CN 111584757 A 说 明 书 3/15 页 所述虚拟电极具有沿所述第一方向延伸的第一边界,所述第一边界在所述衬底上 的正投影与至少两个所述虚拟像素电路中的虚拟复位晶体管的有源层在所述衬底上的正 投影存在交叠。 在一些实施例中,所述虚拟电极还具有与所述第一边界相邻的第二边界,所述第 二边界的延伸方向与所述第一边界的延伸方向相交叉,所述第二边界在所述衬底上的正投 影与任意一个所述虚拟晶体管在所述衬底上的正投影无交叠。 在一些实施例中,所述多个虚拟像素电路中的每个包括虚拟发光控制晶体管,所 述显示母板还包括: 位于所述边缘区的多个虚拟连接件,所述多个虚拟连接件设置在所述虚拟像素电 路与所述虚拟电极之间,所述虚拟连接件设置在所述第一平坦化层背离所述衬底的表面。 在一些实施例中,所述显示母板还包括: 第一栅绝缘层,设置在所述虚拟发光控制晶体管的有源层和栅极之间,所述虚拟 发光控制晶体管的栅极位于有源层远离所述衬底的一侧; 第二栅绝缘层,设置在所述虚拟发光控制晶体管的栅极远离所述衬底的一侧; 层间介质层,设置在所述第二栅绝缘层远离所述衬底的一侧; 其中,所述虚拟发光控制晶体管的源极和漏极设置在所述层间介质层远离所述衬 底的一侧,所述第一平坦化层设置在所述虚拟发光控制晶体管的源极和漏极远离所述衬底 的一侧; 所述虚拟发光控制晶体管的源极和漏极均通过贯穿所述层间介质层、所述第二栅 绝缘层和所述第一栅绝缘层的过孔与所述有源层连接;或者,所述虚拟发光控制晶体管的 源极和漏极均位于所述层间绝缘层背离所述衬底的表面,以使所述虚拟发光控制晶体管的 源极和漏极均与所述有源层绝缘间隔开。 在一些实施例中,所述显示母板还包括:设置在所述显示区和所述边缘区的多条 第二电源线,所述多条第二电源线中的每条在所述衬底上的正投影均与所述第一电源线在 所述衬底上的正投影交叉设置; 每个所述第一显示电极在所述衬底上的正投影与至多一条所述第二电源线在所 述衬底上的正投影存在交叠, 每个所述虚拟电极在所述衬底上的正投影与至少两条所述第二电源线在所述衬 底上的正投影存在交叠。 在一些实施例中,每个所述虚拟电极在所述衬底上的正投影与3~40条所述第二 电源线在所述衬底上的正投影存在交叠。 在一些实施例中,所述第一电源线与所述第二电源线同层设置。 在一些实施例中,所述虚拟电极具有相邻的第一边界和第二边界,所述第一边界 的延伸方向与所述第一电源线的延伸方向相同,所述第二边界的延伸方向与所述第一边界 的延伸方向相交叉,所述第一边界在所述衬底上的正投影位于相邻两条第一电源线在所述 衬底上的正投影之间,所述第二边界在所述衬底上的正投影与所述第二电源线在所述衬底 上的正投影存在交叠。 在一些实施例中,所述第二电源线包括:沿第二方向排列的多个走线组,所述多个 走线组中的每个包括第一走线部和第二走线部,所述第一走线部的两端分别连接相邻的两 9 CN 111584757 A 说 明 书 4/15 页 条第一电源线,所述第二走线部沿所述第二方向延伸,且所述第二走线部与依次排列的多 条所述第一电源线连接;同一个所述走线组中,所述第一走线部和所述第二走线部在所述 第一方向和所述第二方向上均无交叠; 所述第二边界在所述衬底上的投影与所述第一走线部在所述衬底上的投影存在 交叠。 在一些实施例中,所述显示区中的多个第一显示电极被划分为多个重复单元,所 述多个重复单元中的每个包括沿第二方向依次排列的一个第一颜色电极、一个第二颜色电 极对以及一个第三颜色电极,所述第二颜色电极对包括的两个第二颜色电极沿所述第一方 向排列,所述多个重复单元沿所述第二方向排列以形成多个重复单元组,所述多个重复单 元组沿所述第一方向排列,且所述多个重复单元组中的相邻重复单元组沿所述第二方向彼 此错开; 所述边缘区中的多个所述虚拟电极呈阵列排布,每列中的多个所述虚拟电极沿所 述第一方向排列,每行中的多个所述虚拟电极沿所述第二方向排列。 在一些实施例中,每个所述第一颜色电极在所述衬底上的正投影、每个所述第二 颜色电极在所述衬底上的正投影均与所述第一电源线在所述衬底上的正投影无交叠; 每个所述第三颜色电极在所述衬底上的正投影与其中一条所述第一电源线在所 述衬底上的正投影存在交叠。 在一些实施例中,每个所述第一颜色电极在所述衬底上的正投影、每个所述第二 颜色电极在所述衬底上的正投影均与所述第二电源线在所述衬底上的正投影无交叠; 每个所述第三颜色电极在所述衬底上的正投影与其中一条所述第二电源线在所 述衬底上的正投影存在交叠。 在一些实施例中,所述边缘区在的宽度在30mm~60mm之间。 本公开实施例还提供一种显示基板的制作方法,包括: 提供衬底,所述衬底包括:有效区以及位于所述有效区的至少一侧的边缘区,所述 有效区包括:多个面板区和待切割区,所述待切割区将所述多个面板区彼此间隔开,并将所 述边缘区与其相邻的所述面板区间隔开,所述面板区包括显示区和环绕所述显示区的边框 区; 在所述衬底的每个所述显示区和所述边缘区均形成多条第一电源线,所述第一电 源线沿第一方向延伸; 在每个所述显示区形成多个第一显示电极,同时在所述边缘区形成多个虚拟电 极;其中,所述多个第一显示电极中的每个在所述衬底上的正投影与至多一条所述第一电 源线在所述衬底上的正投影存在交叠,所述多个虚拟电极中的每个在所述衬底上的正投影 与至少两条所述第一电源线在所述衬底上的正投影存在交叠; 沿所述待切割区对形成有所述第一电源线、所述第一显示电极和所述虚拟电极的 衬底进行切割,得到多个显示基板。 在一些实施例中,沿所述待切割区对形成有所述第一电源线、所述第一显示电极 和所述虚拟电极的衬底进行切割,之前还包括: 形成像素界定层,所述像素界定层包括: 位于所述显示区的第一像素界定部,所述第一像素界定部设置在所述第一显示电 10 CN 111584757 A 说 明 书 5/15 页 极远离所述衬底的一侧,所述第一像素界定部具有多个像素开口,所述多个像素开口与所 述多个第一显示电极一一对应,所述多个像素开口中的每个暴露出相应的第一显示电极的 至少一部分; 位于所述边缘区的第二像素界定部,所述第二像素界定部设置在所述虚拟电极远 离所述衬底的一侧,所述第二像素界定部覆盖每个所述虚拟电极。 在一些实施例中,形成像素界定层之后还包括: 形成多个发光层,所述多个发光层一一对应地设置在所述多个像素开口中; 形成第二电极层,所述第二电极层设置在所述多个发光层远离所述衬底的一侧, 所述第二电极层位于所述显示区,且与所述边缘区无交叠。 附图说明 附图是用来提供对本公开的进一步理解,并且构成说明书的一部分,与下面的具 体实施方式一起用于解释本公开,但并不构成对本公开的限制。在附图中: 图1为本公开的一些实施例提供的显示母板的衬底的区域划分示意图。 图2为本公开的一些实施例中提供的显示区中的部分结构示意图。 图3为本公开的一些实施例中提供的边缘区中的部分结构示意图。 图4为本公开的一些实施例中提供的第一电源线和第二电源线的部分示意图。 图5为本公开的一些实施例中提供的两个虚拟电极的位置关系示意图。 图6为本公开的一些实施例中提供的发光元件及其连接的显示像素电路的原理 图。 图7为本公开的一些实施例中提供的部分数量的第一显示电极和显示像素电路的 半导体层的示意图。 图8为本公开的一些实施例中提供的虚拟像素电路的半导体层和虚拟电极的示意 图。 图9为本公开的一些实施例中提供的沿图1中I-I’线的剖视图。 图10为本公开的另一些实施例中提供的沿图1中I-I’线的剖视图。 图11为本公开的一些实施例中提供的第一隔垫物/第二隔垫物和第一电源线、第 二电源线的位置关系示意图。 图12为本公开的一些实施例中提供的第一隔垫物与第一显示电极的位置关系示 意图。 图13为本公开的一些实施例中提供的第二隔垫物与虚拟电极的位置关系示意图。 图14为本公开的一些实施例提供的显示基板的制作方法流程图。