技术摘要:

公开了一种存储器系统,该存储器系统包括:被电耦合到与存储器阵列的列相关联的第一位线和第二位线的读出放大器;被电耦合到第一位线的bl晶体管,其中bl晶体管被配置为从第一位线接收第一电信号作为输入;以及被电耦合到第二位线的blb晶体管,其中blb晶体管被配置为从 全部

背景技术:

本公开的各方面总体上涉及存储器芯片中的读出放大器,并且更具体地涉及读出 放大器时钟方案等。 在计算机存储器中,读出放大器是在从存储器中读取数据时使用的半导体存储器 芯片的读取电路系统的一部分。半导体存储器芯片中的数据被存储在存储器单元中,该存 储器单元以行和列的阵列被布置在芯片上。连接一行存储器单元的导线被称为“字线”并且 通过在其上生成电压而被激活。存储器单元的每一列具有一对相关联的导线(存储器单元 的列的任一侧有一个导线),该导线被称为“位线”。每对位线附接到存储器阵列的边缘处的 读出放大器。每个存储器单元位于特定字线和位线的交点处,它们的交点可以用于“寻址” 该单元。 为了从静态随机存取存储器(SRAM)芯片中的特定存储器单元读取位,激活该单元 所在的字线(行)(即,在该字线上生成电流)。然后可以通过感测跨与存储器单元相关联的 一对位线(即,存储器单元的包含所涉及的存储器单元的列的任一侧上的位线)的电压差来 确定存储在单元中的值(逻辑“0”或“1”)。与位线对相关联的读出放大器的作用是感测跨位 线的电压差(该电压差表示存储在存储器单元中的值),并且将该电压差放大到可识别的逻 辑电平(即,逻辑“0”或““1”),使得可以通过存储器阵列外部的逻辑来正确地解释数据。然 后,将期望的存储器单元中的位被从该单元的读出放大器锁存到缓冲器中,并且然后被放 置在输出总线上。 具有附加功能的动态随机存取存储器(DRAM)芯片中的读出放大器的操作类似于 SRAM芯片中的读出放大器的操作。DRAM芯片的每个存储器单元中的数据作为电荷存储在存 储器单元中的电容器中。特定存储器单元的读取操作会耗尽该单元中的电荷,从而破坏数 据。这样,在数据被读出之后,读出放大器通过向单元施加电压来立即将其写回到单元中, 从而对电容器充电。这称为存储器刷新。 读出放大器由读出放大器使能信号生成器生成的读出放大器使能(“saen”)信号 驱动。为了使得读出放大器能够感测跨一对位线的电压电平,读出放大器使能信号生成器 接收外部时钟信号并且在一段时间的延迟之后生成读出放大器使能信号。在接收到读出放 大器使能信号时,读出放大器可以检测跨该对位线的电压差。 SRAM电路中的存储器单元通常由两个、四个或六个晶体管组成。在基于六晶体管 (6T)SRAM的设计中,读出放大器接收到读出放大器使能信号的时间与在其间该读出放大可 以准确地评估跨位线的电压(即,确定正在读取的存储器单元是否包含“0”或“1”)的时间之 间的“竞争”是一个重要的性能裕度。读出放大器使能信号需要到达,使得位线差分(即,跨 5 CN 111557031 A 说 明 书 2/10 页 该对位线的电压)足以满足读出放大器偏移(即,为使读出放大器正确地检测电压差,位线 上所需要的最小电压差)。另外,读出放大器使能信号的定时直接影响SRAM输出的延迟,其 中生成读出放大器使能信号的较长延迟导致读取存储器单元的延迟较长。 此外,需要利用六西格玛统计弱位评估来跟踪读出放大器使能信号(在任何集成 电路中,由于制造缺陷,晶体管的电流强度存在一些差异——因此,大多数SRAM电路被设计 为具有足够的裕度来覆盖过程的六倍的方差或“西格玛”)。在具有复杂译码的存储器(诸如 基于内容可寻址存储器(CAM)的译码或基于预测的译码)中,位线对电压差与读出放大器使 能信号的到达之间的发散路径可能很大,因此导通芯片变化(OCV)裕度也可能很大。这种差 异增加了SRAM阵列的输出延迟。 通常,由于读出放大器使能信号生成器从rd_bank_clk接收时钟信号,因此“rd_ bank_clk”(即,存储器芯片的存储体阵列内的时钟)用作该竞争裕度的发散点。然而,在需 要字线的字/字节门控的存储器中,可以存在多个确定发散点返路径,因此主时钟(“clk”) 也可能引起延迟。同样,双电压域要求该裕度跨过各种阵列和逻辑域电压两者。更具体地, 低功率存储器使用双电压域架构。在这种架构中,存储器位单元阵列被连接到具有有限扩 展性的电源(阵列电源域),而部分外围设备和其余逻辑被连接到不同的完全可扩展的电源 (逻辑电源域)。在低功率操作期间,逻辑电源被降低到比位单元可以工作的最小电压低得 多的电压。在这种架构下,字线和读出放大器路径跨越两个电压域,并且需要在整个电源范 围内彼此跟踪。 另外,最坏情况下的感测裕度出现在低电压电平上,这驱动了turbo角(即,设置最 高支持频率的高电压角)读出放大器使能信号定时。更具体地,在低压下增加的变化要求在 低压拐角处具有更大的裕度,并且影响在turbo拐角处的读出放大器使能信号的定时。减小 位线与读出放大器使能信号之间的差异可以帮助节省OCV裕度并且改善宏(例如,SRAM块) 的总体定时。

技术实现要素:

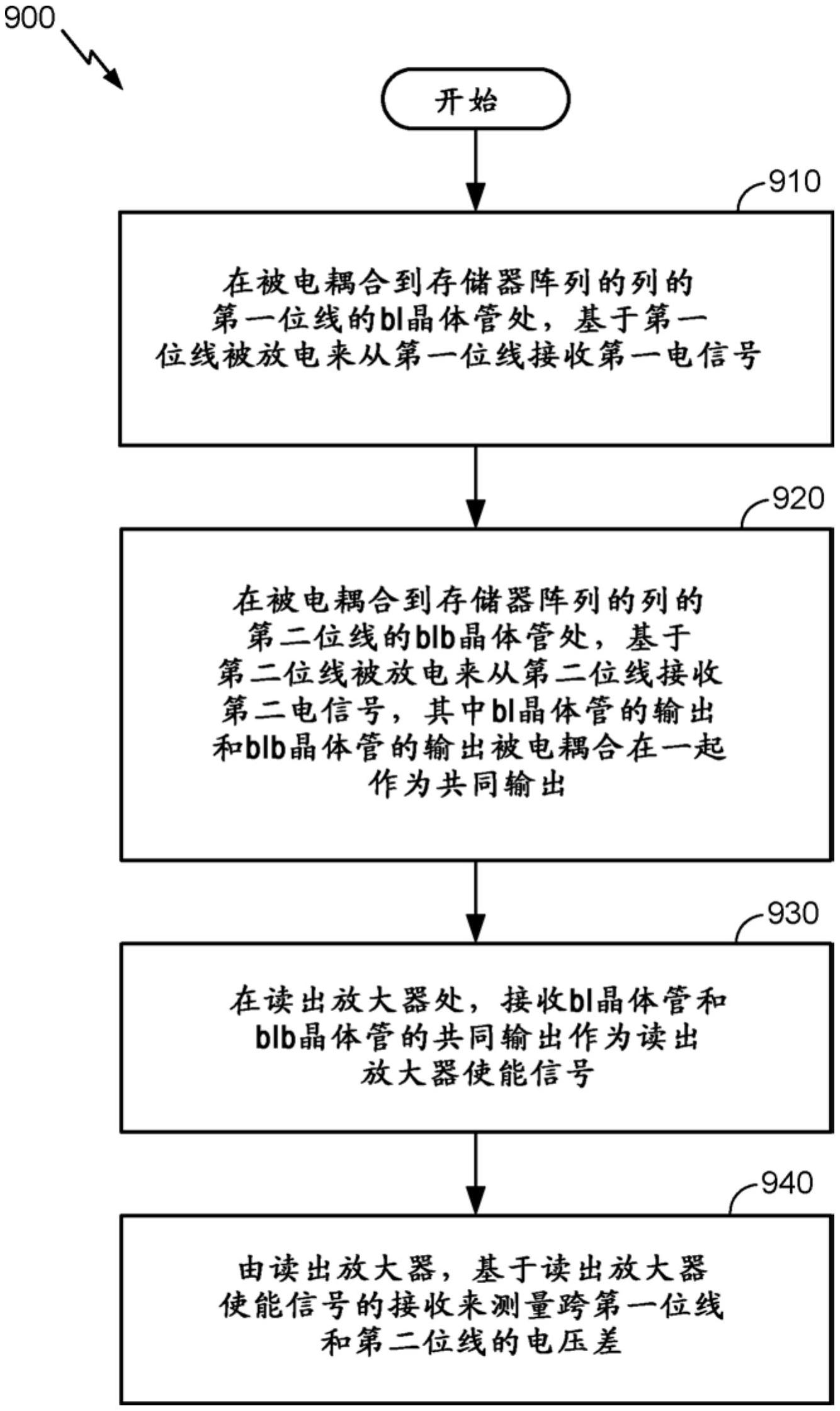

下面给出了与本文中公开的一个或多个方面有关的简化概述。这样,以下概述不 应当被认为是与所有预期方面有关的详尽概述,也不应当被视为标识与所有预期方面有关 的重要或关键要素或界定与任何特定方面相关联的范围。因此,以下概述的唯一目的是以 简化的形式在以下呈现的详细描述之前呈现与本文中公开的机制相关的一个或多个方面 的某些概念。 在一个方面,一种存储器系统包括:被电耦合到与存储器阵列的列相关联的第一 位线和第二位线的读出放大器;被电耦合到第一位线的bl晶体管,其中bl晶体管被配置为 从第一位线接收第一电信号作为输入;以及电耦合到第二位线的blb晶体管,其中blb晶体 管被配置为从第二位线接收第二电信号作为输入,其中bl晶体管的输出和blb晶体管的输 出被电耦合在一起作为共同输出,并且其中读出放大器被配置为接收bl晶体管和blb晶体 管的共同输出作为输入。 在一个方面,一种操作存储器系统的方法包括:在被电耦合到存储器阵列的列的 第一位线的bl晶体管处,基于第一位线被放电从第一位线接收第一电信号;在被电耦合到 存储器阵列的列的第二位线的blb晶体管处,基于第二位线被放电来从第二位线接收第二 6 CN 111557031 A 说 明 书 3/10 页 电信号,其中bl晶体管的输出和blb的输出晶体管被电耦合在一起作为共同输出;在被电耦 合到第一位线和第二位线的读出放大器处,接收bl晶体管和blb晶体管的共同输出作为读 出放大器使能信号;以及由读出放大器,基于读出放大器使能信号的接收来测量跨第一位 线和第二位线的电压差。 在一个方面,一种存储器系统包括:第一装置,用于基于存储器阵列的列的第一位 线被放电来从第一位线接收第一电信号的,用于接收的第一装置电耦合到该第一位线;第 二装置,用于基于存储器阵列的列的第二位线被放电,从第二位线接收第二电信号的,用于 接收的第二装置被电耦合到第二位线,其中用于接收的第一装置的输出和用于接收的第二 装置的输出被电耦合在一起作为共同输出;以及用于放大电压摆幅的装置,被配置为接收 用于接收的第一装置和用于接收的第二装置的共同输出作为读出放大器使能信号,该用于 放大电压摆幅的装置被电耦合到第一位线和第二位线,其中该用于放大电压摆幅的装置还 被配置为基于读出放大器使能信号的接收来测量跨第一位线和第二位线的电压差。 基于附图和详细描述,与本文中公开的各方面相关联的其他目的和优点对于本领 域技术人员将是很清楚的。 附图说明 附图被呈现以帮助描述本公开的各个方面,并且附图被提供仅用于说明各方面而 不是对其进行限制。 图1示出了SRAM的示例性架构。 图2更详细地示出了SRAM阵列的单个列的示例性架构。 图3示出了包括常规读出放大器的示例性电路。 图4示出了常规系统,其示出了读出放大器使能信号的生成。 图5示出了根据本公开的至少一个方面的示例性架构,其示出了读出放大器使能 信号的生成。 图6A和6B示出了根据本公开的至少一个方面的示例性系统,其示出了读出放大器 使能信号的生成。 图7示出根据本公开的一个方面的包括读出放大器的示例性电路。 图8示出了根据本公开的至少一个方面的各种曲线图,其示出了各种信号的定时。 图9示出了根据本公开的一个方面的操作存储器系统的示例性方法。