技术摘要:

本发明涉及半导体器件的制造方法,涉及半导体制造工艺,深沟槽结构的位于P型外延层的部分的侧壁包括N型多晶硅层,至少部分位于深N阱区域内的浅沟槽内的深沟槽一侧的N型多晶硅层与N型埋层和深N阱接触,N型埋层通过彼此连接的N型多晶硅层、深N阱、N型阱、N型重掺杂区、接 全部

背景技术:

随着LDMOS(Laterally Double-diffused MOS)应用电压的不断提高,对高低压器 件之间的隔离结构的耐压能力也提出了更高的要求。PN结的隔离结构被广泛应用在低压段 BCD工艺中,但是PN结隔离结构的尺寸随着耐压升高急剧增加,且结隔离的漏电也随之升 高。因此,为了减小隔离结构的尺寸并减小漏电效应,深沟槽隔离(Deep Trench Isolation,DTI)结构逐渐地被应用到中-高压BCD工艺中。对比于结隔离,DTI结构的最大优 势是尺寸小。

技术实现要素:

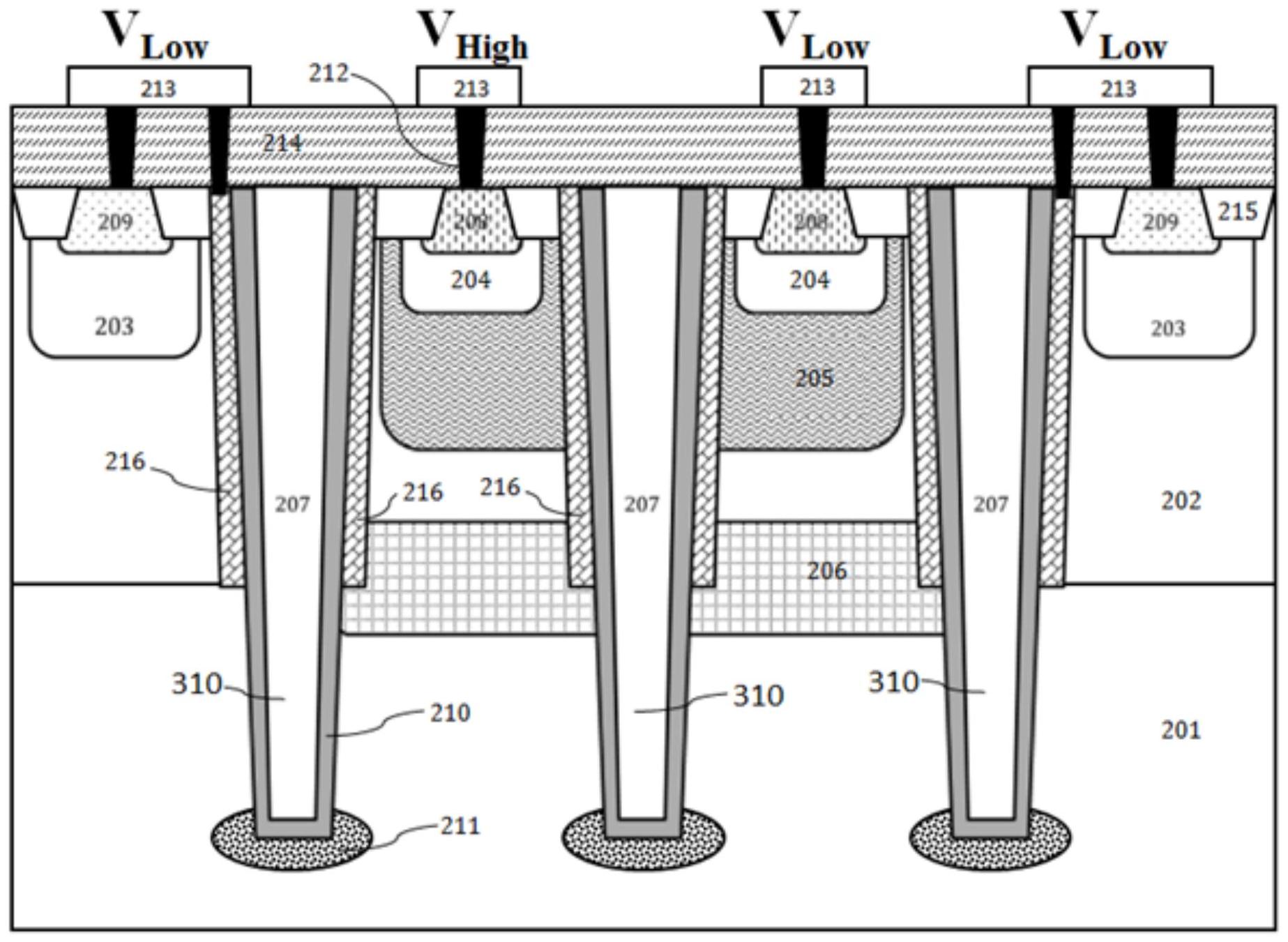

本发明提供的一种半导体器件的制造方法,包括:S1:提供P型衬底,在P型衬底上 形成N型埋层,进行P型外延层生长以在P型衬底上形成P型外延层,进行高能磷注入在P型外 延层上形成深N阱,并经高温热推进,随后依次沉积第一氧化硅层和氮化硅层,其中深N阱与 N型埋层在竖直方向上间隔开来,且横向方向上至少部分重叠;S2:进行光刻曝光工艺,形成 浅沟槽图形,以氮化硅层为硬质掩膜层刻蚀硅,形成浅沟槽,随后在硅表面热氧化形成致密 的氧化硅层并在其表面沉积第二氧化硅层以填充浅沟槽,以氮化硅层为停止层进行平坦化 工艺,然后沉积形成第三氧化硅层,其中一浅沟槽至少部分位于深N阱区域内,一浅沟槽至 少部分位于P型外延层区域内;S3:在浅沟槽区域内进行光刻刻蚀工艺去除硅表面以上的第 二氧化硅层和第三氧化硅层,暴露出浅沟槽底部的硅表面,以第三氧化硅层为掩模层,进行 第一次深沟槽硅刻蚀工艺,第一次深沟槽硅刻蚀工艺的刻蚀深度为P型外延层的厚度,使得 第一次深沟槽硅刻蚀工艺刻蚀的底部在P型衬底的表面,而形成深沟槽,其中一深沟槽至少 部分位于深N阱与N型埋层横向方向上重叠的区域内,一深沟槽至少部分位于P型外延层区 域内;S4:在深沟槽内的侧壁和底部形成在位重掺杂的N型多晶硅层,过刻蚀去除深沟槽底 部的N型多晶硅层,在N型多晶硅层的表面和硅表面沉积形成第四氧化硅层,并刻蚀去除深 沟槽底部的氧化硅层,暴露出深沟槽底部的硅表面,以使第四氧化硅层在多晶硅侧面及顶 部形成侧墙氧化层,其中至少部分位于深N阱与N型埋层横向方向上重叠的区域内的深沟槽 一侧壁的N型多晶硅层与N型埋层接触;S5:以第三氧化硅层和第四氧化硅层为掩膜层,进行 第二次深沟槽硅刻蚀工艺,第二次深沟槽硅刻蚀工艺刻蚀到深沟槽的目标深度,再在深沟 槽内形成第四氧化硅层,第四氧化硅层覆盖深沟槽的侧面和底部;S6:沉积多晶硅层,使多 晶硅层填充深沟槽,以氮化硅层为停止层,进行第二次平坦化工艺,去除氮化硅层之上的材 料,然后去除氮化硅层和第一氧化硅层,随后进行多晶硅和氧化硅刻蚀,并分别进行N型和P 型阱注入工艺以形成位于P型外延层区域内的P型阱和至少部分位于深N阱区域内的N型阱; 以及S7:在P型阱内进行P型重掺杂形成P型重掺杂区,在N型阱内进行N型重掺杂形成N型重 掺杂区,沉积层间介质层并平坦化,进行光刻刻蚀工艺在层间介质层内形成接触孔并在其 4 CN 111584366 A 说 明 书 2/7 页 中填充导电材料,形成第一金属层,并刻蚀形成多个金属线,P型重掺杂区和深沟槽内靠近P 型阱侧的N型多晶硅层分别通过一接触孔连接同一金属线,N型重掺杂区通过一接触孔连接 一金属线。 更进一步的,在步骤S1中,在P型衬底上注入锑金属并进行高温热推进形成N型埋 层。 更进一步的,在步骤S1中,N型埋层位于P型衬底表面的中间部分区域。 更进一步的,在步骤S1中,深N阱在空间上位于N型埋层的上方,且在横向方向上与 N型埋层至少部分重叠。 更进一步的,在步骤S2中,至少部分位于P型外延层区域内的浅沟槽可包括部分位 于深N阱内的区域。 更进一步的,在步骤S3中,至少部分位于深N阱与N型埋层横向方向上重叠的区域 内的深沟槽至少部分延伸至N型埋层内。 更进一步的,在步骤S4中,在形成第四氧化硅层之前还包括热氧化工艺以在N型多 晶硅层表面和硅表面形成一层氧化层。 更进一步的,在步骤S4中,第四氧化硅层厚度大于N型多晶硅层的厚度。 更进一步的,在步骤S5中,在形成深沟槽后还包括在所述深沟槽底部的所述P型衬 底表面形成沟道停止层。 更进一步的,在步骤S7中,在步骤S6中还在P型阱与N型多晶硅层之间形成N型阱, 使N型多晶硅层与N型阱连通,在步骤S7中还包括在P型阱与N型多晶硅层之间的N型阱内形 成N型重掺杂区。 本发明还提供一种半导体器件结构,包括:P型衬底,在P型衬底表面包括N型埋层, 在P型衬底和N型埋层上包括P型外延层;在P型外延层内包括深N阱,一至少部分位于深N阱 区域内的浅沟槽和一至少部分位于P型外延层区域内浅沟槽;至少部分位于深N阱区域内的 浅沟槽内的深沟槽和至少部分位于P型外延层区域内浅沟槽内的深沟槽,深沟槽包括位于P 型外延层的部分和位于P型衬底的部分,深沟槽的位于P型外延层的部分的侧壁包括N型多 晶硅层,深沟槽内的N型多晶硅层表面及硅表面包括第四氧化硅层,深沟槽内填充有多晶硅 层,其中至少部分位于深N阱区域内的浅沟槽内的深沟槽一侧的N型多晶硅层与N型埋层和 深N阱接触;位于P型外延层区域内的P型阱和至少部分位于深N阱区域内的N型阱,在P型阱 内包括P型重掺杂区,在N型阱内包括N型重掺杂区;沉积层间介质层,沉积层间介质层覆盖 硅表面、浅沟槽表面及深沟槽表面,层间介质层中包括接触孔,沉积层间介质层上包括金属 线,P型重掺杂区和深沟槽内靠近P型阱侧的N型多晶硅层分别通过一接触孔连接同一金属 线,N型重掺杂区通过一接触孔连接一金属线。 更进一步的,靠近P型阱侧的N型多晶硅层与P型重掺杂区分别通过接触孔与同一 金属线连接,P型重掺杂区与P型阱、P型外延层及P型衬底连通。 更进一步的,深N阱与N型埋层在竖直方向上间隔开来,且横向方向上至少部分重 叠,N型埋层通过彼此连接的N型多晶硅层、深N阱、N型阱、N型重掺杂区、接触孔及金属线引 出。 本发明提供的半导体器件的制造方法,深沟槽结构的位于P型外延层的部分的侧 壁包括N型多晶硅层,至少部分位于深N阱区域内的浅沟槽内的深沟槽一侧的N型多晶硅层 5 CN 111584366 A 说 明 书 3/7 页 与N型埋层和深N阱接触,N型埋层通过彼此连接的N型多晶硅层、深N阱、N型阱、N型重掺杂 区、接触孔及金属线引出,靠近P型阱侧的N型多晶硅层与P型重掺杂区分别通过接触孔与同 一金属线连接,P型重掺杂区与P型阱、P型外延层及P型衬底连通,使靠近P型阱侧的N型多晶 硅层与衬底形成短接,在N型埋层充分引出的情况下,大幅度缩短深N阱高温热推进的时间, 降低成本,此外,热推进时间的缩短可以减少N型埋层的往上扩散,增加纵向耐压长度,提高 纵向耐压。 附图说明 图1为一实施例的包括深沟槽隔离结构的半导体结构示意图。 图2a-图2f为本发明一实施例的半导体器件制造过程中的器件示意图。 图中主要元件附图标记说明如下: 201、P型衬底;202、P型外延层;211、停止层;210、第四氧化硅层;310、深沟槽;206、 N型埋层;216、N型多晶硅层;205、深N阱;204、N型阱;203、P型阱;208、N型重掺杂区;209、P型 重掺杂区;212、接触孔;213、金属线。