技术摘要:

一种半导体结构及其形成方法,形成方法包括提供半导体衬底,所述半导体衬底具有第一区域、第二区域及隔离区域,所述第二区域通过所述第一区域与所述隔离区域相隔;在所述半导体衬底上形成栅极结构,所述栅极结构横跨所述第一区域和所述第二区域,且所述栅极结构位于所 全部

背景技术:

随着半导体制造技术的飞速发展,半导体器件正朝着更高的元件密度以及更高的 集成度的方向发展。晶体管作为最基本的半导体器件目前被广泛应用,但是,在晶体管的测 试过程中,晶体管内会出现通道效应(pipeline defect),该通道效应会导致器件上的源极 和漏极之间发生漏电现象,从而导致晶体管失效,特别是在静电放电(ESD)大面积重复的 NMOS结构上,这种失效现象频繁发生。 现有技术中,在制作半导体器件时,通过调整离子注入并经回火工艺,或者在浅槽 隔离(STI)刻蚀时,调整掩膜层的厚度来减小应力,以消除通道效应。 但是NMOS本身参杂的元素原子序数较大,离子注入能量较高,对有源区(AA)的损 伤较大,有时候这种损伤即时经过回火也不能完全消除;再加上整个结构面积很大,在有源 区进行浅槽隔离刻蚀时会沉积的大面积的掩膜层,即使调整掩膜层的厚度,在有源区的两 端还是有很大的应力存在;这些因素叠加起来,由于有源区的损伤以及应力的存在,半导体 器件的两端依旧产生通道效应(pipeline defect),造成半导体器件失效。

技术实现要素:

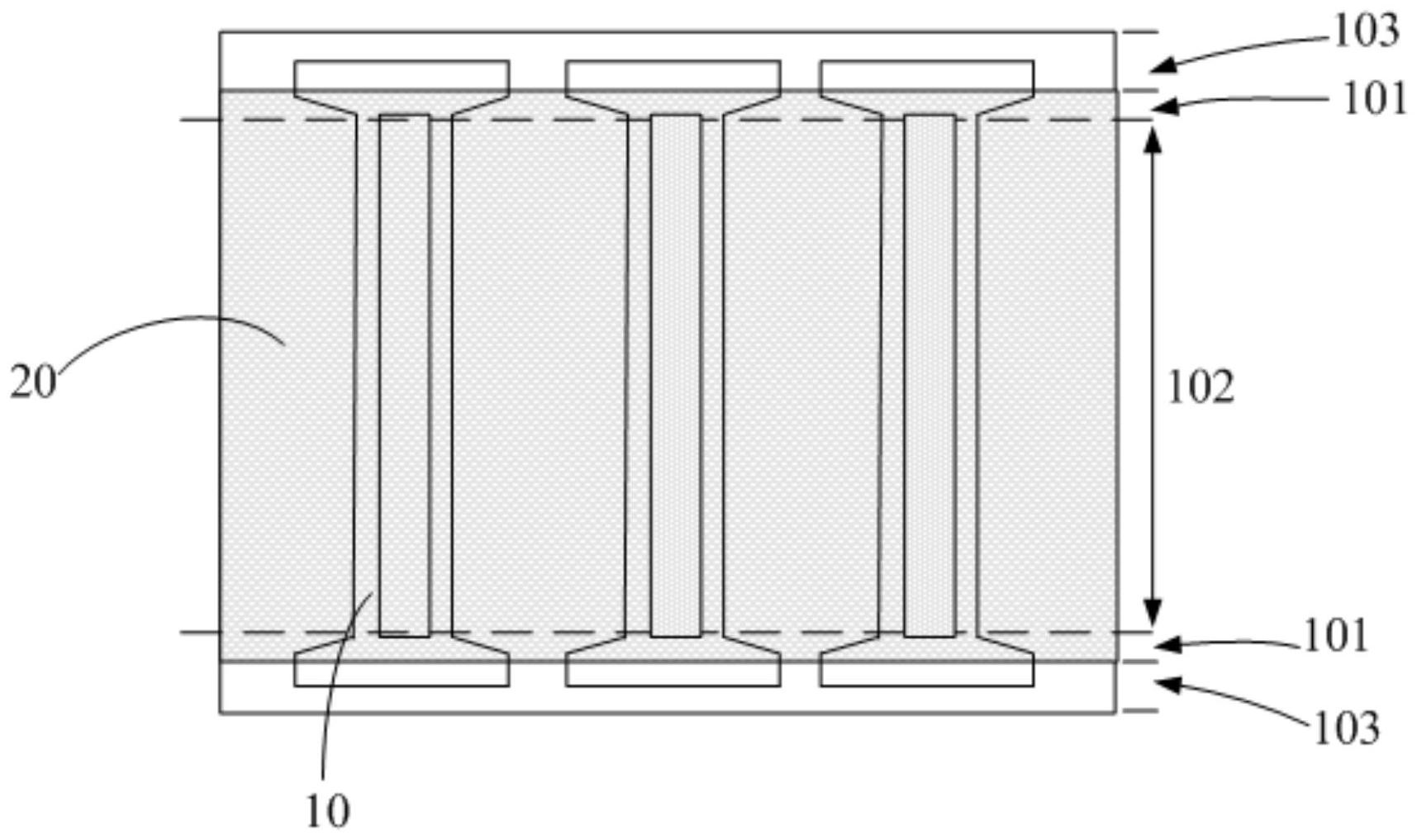

本发明解决的问题是提供一种半导体结构的形成方法,改善所形成半导体结构的 性能,减少失效发生。 为解决上述问题,本发明提供一种半导体结构的形成方法,包括半导体衬底,所述 半导体衬底具有第一区域、第二区域及隔离区域,所述第二区域通过所述第一区域与所述 隔离区域相隔;在所述半导体衬底上形成栅极结构,所述栅极结构横跨所述第一区域和所 述第二区域,且所述栅极结构位于所述第一区域部分的宽度大于位于所述第二区域部分的 宽度。 可选的,所述栅极结构位于所述第一区域部分的宽度与位于所述第二区域部分的 宽度比例为1.5-3。 可选的,在平行于所述栅极结构的延伸方向上,所述栅极结构位于所述第一区域 部分的长度值是位于所述第二区域部分的宽度值的1倍到2倍。 可选的,形成所述栅极结构包括:在所述半导体衬底表面形成栅介质层;在所述栅 介质层表面形成栅极层;在所述栅极层上形成图形化光刻胶层;以所述图形化光刻胶层为 掩膜,刻蚀所述栅极层以及所述栅介质层至露出所述半导体衬底层,形成所述栅极结构。 可选的,形成所述图形化光刻胶层包括:形成第一图形化光刻胶层以及第二图形 化光刻胶层。 可选的,以所述第一图形化光刻胶层为掩膜,刻蚀所述栅极层以及所述栅介质层 至露出所述半导体衬底层,形成位于第二区域部分的栅极结构;以所述第二图形化光刻胶 3 CN 111613534 A 说 明 书 2/6 页 层为掩膜,刻蚀所述栅极层以及所述栅介质层至露出所述半导体衬底层,形成位于第一区 域部分的栅极结构。 可选的,所述第一图形化光刻胶层以及第二图形化光刻胶层同步形成。 可选的,所述第一图形化光刻胶层以及第二图形化光刻胶层分步形成。 可选的,相邻位于所述第一区域的栅极结构在宽度方向上相连接或者不相连接。 可选的,在所述半导体衬底上形成栅极结构之后,还包括,在栅极结构两侧的所述 半导体衬底内形成源漏掺杂区。 本发明还一种半导体的结构,包括:半导体衬底,所述半导体衬底具有第一区域、 第二区域及隔离区域,所述第二区域通过所述第一区域与所述隔离区域相隔;栅极结构,所 述栅极结构横跨所述第一区域和所述第二区域,且所述栅极结构位于所述第一区域部分的 宽度大于位于所述第二区域部分的宽度。 与现有技术相比,本发明的技术方案具有以下优点: 在所述半导体衬底上形成栅极结构,所述栅极结构横跨所述第一区域和所述第二 区域,且所述栅极结构位于所述第一区域部分的宽度大于位于所述第二区域部分的宽度。 半导体器件的有源区与隔离结构的交界处往往会产生较大应力,使得出现通道效应;所述 第一区域为有源区上容易出现所述通道效应的区域,将此位置的栅极结构宽度做长,使所 述第一区域的沟道长度较长,较长的沟道长度避免源极与漏极之间贯通在一起,这样以来, 漏电引起器件失效也就无法发生。 附图说明 图1至图5为本发明提供的一实施例中栅极结构形成过程示意图; 图6为本发明提供的一实施例所形成栅极结构的俯视示意图(形成多个栅极); 图7为本发明提供的另一实施例所形成栅极结构的俯视示意图(形成多个栅极)。