技术摘要:

[课题]本发明提供一种像素结构,在间接TOF相机用的固态成像装置,抑制杂散光向浮置扩散区(FD)的泄漏,从而提高飞行距离测定精度。[解决方法]在用于固态成像装置的像素100中,具备:光电二极管(PD)10;形成于硅基板的第二表面,一端连接于PD10的多个传输晶体管(TG)20、2 全部

背景技术:

例如,专利文献1(日本特开第2013-98446号公报)公开了具有全局快门功能并且 能够抑制白点和暗电流的固态成像元件。 专利文献1(日本特开第2013-98446号公报)中描述的固态成像元件包括半导体基 板、在半导体基板上形成的光电二极管以及传输在光电二极管中累积的信号电荷的浮动扩 散区域,进一步具备遮光层,该遮光层包括与覆盖半导体基板中的浮动扩散区域的半导体 基体表面平行的水平遮光部分以及与半导体基体面垂直的垂直遮光部分。 另外,专利文献2(日本特开第2014-096490号公报)公开了一种能够减少杂散光影 响的成像元件。 专利文献2(日本特开第2014-096490号公报)中描述的成像元件,包括:光电转换 单元、用于保存光电转换单元中累积的电荷的电荷保持单元以及设置在光电转换单元彼此 相邻的方向的光电转换单元的四个边中的至少两个边的遮光部,电荷保持单元设置在由两 个遮光部遮光的区域,并且遮光部设置在形成有光电转换单元和电荷保持单元的基板上, 当光电转换单元彼此相邻的方向为水平方向时,遮光部以在垂直方向上贯通的状态设置在 基板上。 另外,专利文献3(日本特开第2017-168566号公报)公开了一种抑制杂散光对FD等 电荷累积单元影响的固态成像元件。 专利文献3(日本特开第2017-168566号公报)中描述的固态成像元件具备:由多个 像素构成且形成于每个像素,将入射光转换为电荷的光电转换单元、暂时保持转换的电荷 的电荷累积单元以及形成于像素之间,且在基板的厚度方向上具有预定的长度的第一遮光 部,电荷累积单元形成于在纵向上相邻的像素之间形成的第一遮光部与在横向上相邻的像 素之间形成的第一遮光部交叉的交叉部的下方。 专利文献4(日本特开第2013-026264号公报)公开了一种能够改善光晕特性的固 态成像元件。 专利文献4(日本特开第2013-026264号公报)中记载的固态成像元件包括:形成在 半导体基板表面上的光电二极管、具有水平型和垂直型的栅电极以及浮置扩散区。在电荷 累积且向栅电极施加电压时,垂直型栅电极在有效栅宽度Weff的方向上且在隔着垂直型栅 电极的两侧的水平栅电极下的区域,形成在有电势差的位置。 [现有技术文献] [专利文件1]日本特开第2013-098446号公报。 [专利文献2]日本特开第2014-096490号公报。 [专利文献3]日本特开第2017-168566号公报。 4 CN 111599828 A 说 明 书 2/14 页 [专利文献4]日本特开第2013-026264号公报。

技术实现要素:

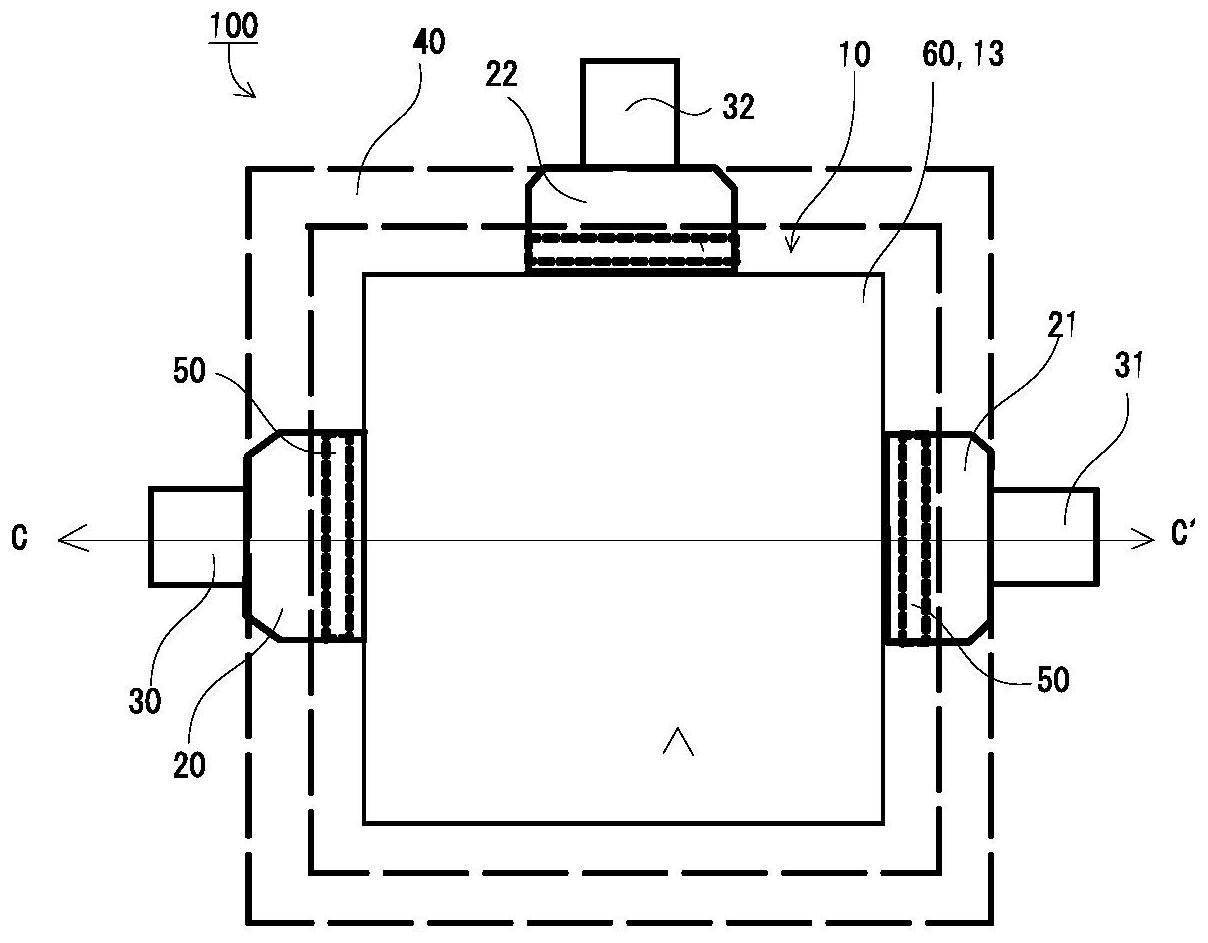

[本发明要解决的问题] 时间飞行(TOF)相机,这是一种通过测量从光源发射的光被对象物反射并返回到 相机的时间,根据已知的光的速度计算距离的方法。基于TOF方法的距离测量最初是光电二 极管、短脉冲激光器和时间测量电路由离散元件组成的单点测量。然而,近年来,随着CMOS 图像传感器的发展,开发了能够测量时间的图像传感器(时间飞行图像传感器)。 TOF方法通过测量光源发出的光到达传感器的时间来计算距离。作为测量该时间 的方法,一种是直接测量时间的直接TOF方法,一种是间接TOF方法,该方法将与光源同步的 多个时间窗口(时钟)采样的光电荷量转换为时间。间接TOF方法不需要像素内的时间计算 电路,且可以相对减少像素中的元件数量,因此具有容易实现高分辨率的优点。 然而,为了实现小型而且高分辨率的TOF图像传感器,需要减少多个时间窗口之间 的增益误差,减小像素大小,减少暗电流的影响,以低噪声读取。 在间接TOF相机的情况下,配置有多个传输晶体管(TG)以在多个时间窗口(时钟) 中对光电二极管(PD)的电荷进行采样。为了减小多个时间窗口之间的增益误差,在时间上 固定入射光的情况下,由多个TG采样并累积在相应的浮置扩散区(FD)中的电荷量理论上应 该相同,但存在如下问题:诸如斜入射光的杂散光直接泄漏到FD中,从而增加了多个时间窗 口之间的增益误差。特别是,由于在间接TOF相机中使用中长波长的特别是红外光作为入射 光,使得入射光容易泄漏到FD中,那么采取对策以抑制杂散光影响变得非常重要。 此外,即使对于非间接TOF相机的常规的固态成像装置中,所有像素中都包括FD, 在采用全局快门曝光情况下,特别是当使用背面辐照方法的传感器时,FD在表面侧形成,所 以很难避免红外光泄漏到FD中。 专利文献1中描述的固态成像元件包括遮光层,其由覆盖半导体基板内浮动扩散 区域的平行于半导体基板表面的水平遮光部、与半导体基体表面垂直的垂直遮光部组成, 来防止从背面照射的光泄漏到浮动扩散区域。然而,在专利文献1中描述的固态成像元件的 情况下,当传输栅极关闭时,光电二极管中传输晶体管正下方的电荷很有可能未传输完,并 且在光电二极管之间放遮光层会导致浮动扩散区域中产生暗电流,浮动扩散区域中暗电流 的产生是一个值得关注的问题。 在专利文献2所记载的固态成像元件中,在像素之间形成有嵌入金属材料制作的 遮光壁,在该遮光壁的下方形成浮动扩散区域。然而,在专利文献2所描述的结构中,浮动扩 散区域可能没有被充分地遮挡,浮动扩散区域本身根据收集到的杂散光进行光电转换,可 能产生错误信号。(例如,在图5的结构的情况下,入射光直接泄漏到传输晶体管的浮动扩散 区域侧的源极或漏极中,因此遮光是不充分的)。 专利文献3所记载的固态成像元件中,电荷累积单元设置在纵向的遮光部与横向 的遮光部的交叉部的下方。从光的入射的基板的背面侧到表面侧形成遮光部,但在专利文 献3中,除了遮光部以外,还具有在基板的表面侧也形成垂直晶体管的例子(见图6)。 然而,在图6的情况下,垂直晶体管的目的在于在从电荷累积单元的较深部分有效 地转移电荷,而它不是用来遮光的,并且,在垂直晶体管由多晶硅制成的情况下,不能遮挡 5 CN 111599828 A 说 明 书 3/14 页 到浮动扩散区域的光,这是一个问题。 作为第二实施方式,专利文献4描述了一种固态成像元件,该固态成像元件包括具 有多个垂直栅极的传输栅极。然而,专利文献4的第二实施方式旨在通过在第一垂直栅极 24B和第二垂直栅极24C之间形成溢出路径来改善固态成像元件的光晕特性,由于它不是基 于TOF或全局快门方式的固态成像装置,因此不存在阻止杂散光进入浮动扩散区域或提高 电荷从光电二极管到浮动扩散区域的传输速度的想法。 本发明的主要目的是在用于间接TOF相机的固态成像装置中提出一种像素结构, 该像素结构可以防止诸如斜入射光的杂散光泄漏到浮置扩散区中,从而提高飞行距离测量 精度。 本发明的第二目的是提供一种像素结构,该像素结构可以提高用于间接TOF相机 像素的传输晶体管的电荷传输速度,从而对应高的时钟频率。 (1) 根据第一发明的用于固态成像装置的像素,包括:多边形状的光电二极管,其根据 从硅基板的第一表面入射的光的光量产生电荷;多个传输晶体管,其形成在硅基板的第二 表面上,一端与光电二极管连接;多个浮置扩散区,其形成在硅基板的第二表面上,一端分 别与多个传输晶体管的另一端连接;第一深沟槽隔离,其从硅基板的第一表面朝向第二表 面以预定深度形成并且围绕光电二极管的周围,其中,在第一深沟槽隔离中嵌入了遮光材 料,或者在内部形成气隙等具有光学反射功能的结构,传输晶体管的栅极在至少一部分上 具有从第二表面朝向第一表面以预定深度形成的第一垂直金属栅,第一垂直金属栅的尖端 与第一深沟槽隔离的尖端在同一平面上或者比第一深沟槽隔离的尖端延伸到硅基板的第 一表面侧,第一垂直金属栅分别与光电二极管的一边平行,配置在比第一深沟槽隔离更靠 近光电二极管侧。 另外,传输晶体管的一端或另一端是指MOS晶体管的源极或漏极。 在这种情况下,可获得以下效果。 (a)通过嵌入有遮光材料或在其内部形成气隙等具有光反射功能的结构的第一深 沟槽隔离,阻挡硅基板第一表面附近的部分到浮置扩散区的杂散光。 (b)从硅基板的第二表面附近的部分到浮置扩散区的杂散光被第一垂直金属栅的 栅极金属阻挡。 (c)通过将第一垂直金属栅配置在比第一深沟槽隔离更靠近光电二极管侧,从而 提高了在光电二极管的第一表面附近的区域中累积的电荷向浮置扩散区的传输速度。 另外,在第一深沟槽隔离上形成有气隙的情况下,硅基板的折射率约为3.4,氧化 硅膜的折射率约为1.5,与此相对,由于气隙(充满空气等气体的空间)的折射率约为1.0,因 此硅基板的第一表面附近的部分经由第一深沟槽隔离的氧化硅膜入射到氧化硅膜与气隙 之间的界面上的光,在该界面处被全反射。因此,形成有气隙的第一深沟槽隔离可以阻挡从 硅基板的第一表面附近的部分到浮置扩散区的杂散光。 此外,也可以是,不是在第一深沟槽隔离上形成气隙,而是通过嵌入折射率比氧化 硅膜低的物质等来形成在与氧化硅膜的界面处具有光反射功能的结构。 (2) 根据第二发明的用于固态成像装置的像素,也可以是在根据第一发明的用于固态 6 CN 111599828 A 说 明 书 4/14 页 成像装置的像素中,每个传输栅极分别包括多个第一垂直金属栅,并且在多个第一垂直金 属栅之间存在没有第一垂直金属栅的平面栅极区域。 第一垂直金属栅有利于将光电二极管的较深部位(靠近硅基板的第一表面的部 分)中的电荷传输到浮置扩散区,但是将光电二极管的较浅部位(靠近硅基板的第二表面的 部分)中的电荷传输到浮置扩散区时,有效栅极长度变长,因此传输速度变慢。 在根据第二发明的用于固态成像装置的像素中,具有多个第一垂直金属栅,并且 在多个第一垂直金属栅之间配置了没有第一垂直金属栅的平面栅极区域,由此加速了从光 电二极管的较浅部位的电荷传输速率。 特别是,在用于间接TOF相机的固态成像装置中,传输晶体管的时钟频率高达几百 MHz,加快传输晶体管的电荷传输速率对提升TOF sensor深度性能很重要。 (3) 根据第三发明的用于固态成像装置的像素,也可以是在根据第二发明的用于固态 成像装置的像素中,多个第一垂直金属栅具有从彼此相邻的端部同时沿浮置扩散区方向延 伸的延伸部。 在根据本发明的第二发明的用于固态成像装置的像素中,由于在传输晶体管的一 部分中存在没有第一垂直金属栅的区域,所以存在一部分杂散光可能从光电二极管的第二 表面附近的区域泄漏到浮置扩散区中,但在根据第三发明的用于固态成像装置的像素中, 通过第一垂直金属栅具有从彼此接近的端部同时向浮置扩散区方向延伸的延伸部,与没有 延伸部的情况相比,可以进一步阻止杂散光从光电二极管的较浅部位进入到浮置扩散区。 (4) 根据第四发明的用于固态成像装置的像素,也可以是在第三发明的用于固态成像 装置的像素中,多个第一垂直金属栅的彼此相邻的端部之间的距离小于浮置扩散区的面向 传输栅极的边的长度。 在这种情况下,由于第一垂直金属栅的延伸部配置于浮置扩散区的面向传输晶体 管的边的内侧,因此除了面向彼此的内侧的通道区域外,第一金属栅的外侧的通道区域也 成为有效的通道区域,传输晶体管的传输能力增加。 (5) 根据第五发明的用于固态成像装置的像素,也可以是在第一发明的固态成像装置 的像素中,相对于第一深沟槽隔离,第一垂直金属栅设置在靠近浮置扩散区侧,而不是光电 二极管侧。 在这种情况下,因为可以在光电二极管附近形成第一深沟槽隔离,所以可以更可 靠地阻止入射光从硅基板的第一表面附近的部分到浮置扩散区的泄漏。 (6) 根据第六发明的用于固态成像装置的像素,也可以是在从第一发明到第五发明的 用于固态成像装置的像素中,还包括金属栅反射板,其中,金属栅反射板在硅基板的第二表 面的绝缘膜上形成在与光电二极管重叠的区域中。另外,金属栅极反射板只要与光电二极 管的大部分重叠地形成即可,例如,可以比光电二极管小一些或者比光电二极管大一些。 在这种情况下,可以抑制垂直入射光的透过光成分被布线之类反射带来的杂散 光。 7 CN 111599828 A 说 明 书 5/14 页 (7) 根据第七发明的用于固态成像装置的像素,也可以是在从第一发明到第六发明的 的用于固态成像装置的像素中,还包括第二垂直金属栅,其中,第二垂直金属栅以包围光电 二极管、第一深沟槽隔离、传输晶体管以及浮置扩散区的方式配置。 在这种情况下,可以抑制从自身像素的传输晶体管和相邻像素的传输晶体管之 间,通过硅基板的第二表面的区域绕回的到浮置扩散区的杂散光,以及来自像素内晶体管 的发光而引起浮置扩散区电压变化。 (8) 根据第八发明的用于固态成像装置的像素,也可以是在根据第七发明的用于固态 成像装置的像素中,还包括第二深沟槽隔离,第二深沟槽隔离配置为包围第二垂直金属栅。 在这种情况下,可以进一步抑制从自身像素的传输晶体管和相邻像素的传输晶体 管之间,通过硅基板的第二表面的区域绕回的到浮置扩散区的杂散光,以及来自像素内晶 体管的发光而引起浮置扩散区电压变化。 (9) 根据第九发明的用于固态成像装置的像素,也可以是在基于第八发明的用于固态 成像装置的像素中,还包括第三深沟槽隔离、第三垂直金属栅及用于在像素的浮置扩散区 和相邻像素的浮置扩散区之间切换输出的开关,第三深沟槽隔离和第三垂直金属栅重叠地 配置在开关的周围。 在多个像素被组合并且明显地被视为一个更大像素的情况下(在下文中,被称为 合并(binning)),多个像素的浮置扩散区被共同连接。并且,在某些情况下,固态成像装置 具有切换打开和关闭合并的功能。在这种情况下,在相邻像素的浮置扩散区之间设置有用 于输出切换的开关,以便独立地使用或者共同使用多个相邻像素。杂散光有可能泄漏到用 作开关的MOS晶体管的源极和漏极中。在根据第九发明的用于固态成像装置的像素中,第三 深沟槽隔离和第三垂直金属栅重叠布置在开关周围,从而可以防止杂散光泄漏到开关。 (10) 根据第十发明的用于固态成像装置的像素,也可以是在第八发明的用于固态成像 装置的像素中,将第一深沟槽隔离和第二深沟槽隔离组合以形成一个宽深沟槽隔离,宽深 沟槽隔离的尖端与第一垂直金属栅的尖端以及第二垂直金属栅的尖端之间存在预定的空 间。 在这种情况下,形成在一个宽深沟槽隔离上的遮光膜完全覆盖浮置扩散区,并且 可以防止杂散光从第一表面侧泄漏到浮置扩散区中。 附图说明 图1是从第二表面侧观察的第一实施方式的用于固态成像装置的像素的示意性俯 视图。 图2是沿着图1中的面C-C'截取的第一实施方式的用于固态成像装置的像素的示 意性截面图。 图3是第一实施方式的用于固态成像装置的像素的示意性等效电路图。 图4是从第二表面侧观察的第二实施方式的用于固态成像装置的像素的示意性俯 8 CN 111599828 A 说 明 书 6/14 页 视图。 图5是从第二表面侧观察的第三实施方式的用于固态成像装置的像素的示意性俯 视图。 图6是从第二表面侧观察的第四实施方式的用于固态成像装置的像素的示意性俯 视图。 图7是沿着图6中的面C-C'截取的第四实施方式的用于固态成像装置的像素的示 意性截面图。 图8是第五实施方式的用于固态成像装置的像素的示意性截面图。 图9是从第二表面侧观察的第六实施方式的用于固态成像装置的像素的示意性俯 视图。 图10是从第二表面侧观察的第七实施方式的用于固态成像装置的像素的示意性 俯视图。 图11是从第二表面侧观察的第八实施方式的用于固态成像装置的像素的示意性 俯视图。 图12是从第二表面侧观察的第九实施方式的用于固态成像装置的像素的示意性 俯视图。 图13是沿着图12中的面C-C'截取的第九实施方式的用于固态成像装置的像素的 示意性截面图。 图14是从第二表面侧观察的第十实施方式的用于固态成像装置的像素的示意性 俯视图。 图15是从第二表面侧观察的第十一实施方式的用于固态成像装置的像素的示意 性俯视图。 图16是垂直金属栅晶体管的示意性截面图。 图17是垂直金属电容的示意截面图。