技术摘要:

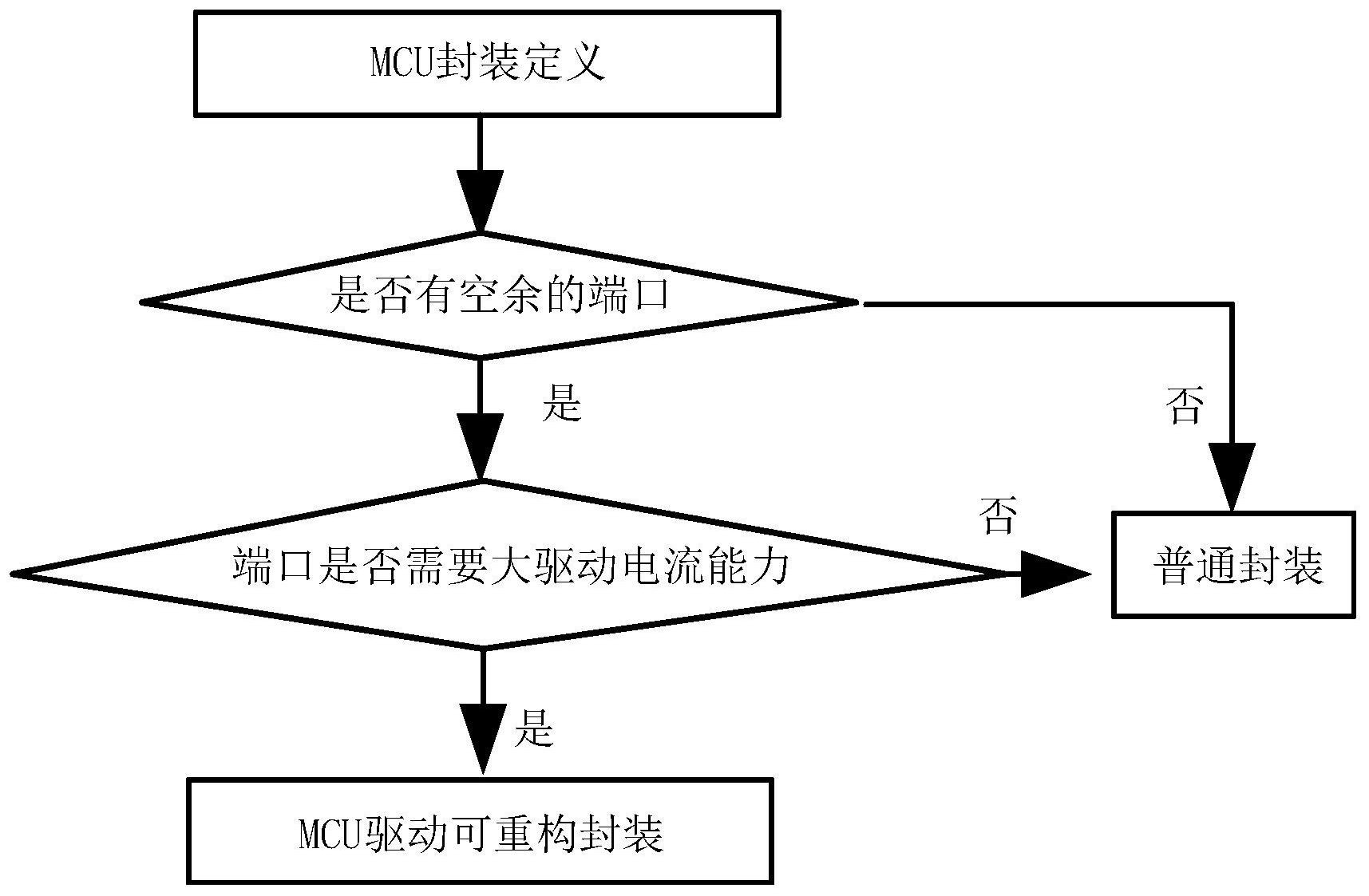

本发明公开了一种MCU端口驱动可重构方法,包括步骤S1:对MCU进行封装定义;步骤S2:判断封装定义的MCU是否有空余的端口;步骤S3:判断封装定义的MCU的端口是否需要更大的驱动电流能力;步骤S4:对MCU进行驱动可重构封装。本发明公开的一种MCU端口驱动可重构方法,其可 全部

背景技术:

现在的MCU,一次流片成本很高,为了满足市场不同的需求,以及营销手段,基本都 是一物多卖的策略。比如同一颗MCU die(晶圆裸片)可以封装成不同的封装形式,比如 LQFP64、LQFP48、LQFP32、TSSOP20等。 一个MCU芯片中都具有很多端口,但是在不同封装形式下,未封装出来所有的端 口,这就意味着使用者只能使用封装出来的端口,而无法使用未封装出来的端口,这将大大 降低使用者可使用资源和端口驱动电流,甚至一些重要功能无法使用。 公开号为:CN101419485B,主题名称为一种功能可变的可穿戴计算机主板的发明 专利,其技术方案公开了“所述可变功能芯片连接至X86系统级SOC的内存、VGA、LVDS、HDMI、 DVI、LAN、USB、IDE、CF、SATA、SPI、LPC、PCI、 GPIO、Smbus、I2C、MMC、SD、COM或者LPT总线上; 所述可变功能芯片对外实现USB、LAN、VGA、LVDS、HDMI、DVI、GPIO、Smbus、I2C、IDE、CF、SATA、 MMC、SD、COM、LPT或者耳麦接口;所述Flash/EEPROM作为可变功能芯片的外置配置芯片,用 于对可变功能芯片中编程文件进行存储;所述可变功能芯片由所述系统电压调节器提供所 需电源;所述可变功能芯片实现该可穿戴计算机主板在“系统综合控制功能”、“自定义逻辑 功能”、“协处理器与总线功能”、“接口功能”上的硬件层次的在线升级与扩展;所述可变功 能芯片内部包括配属模块组、接口模块组、存储模块组、片内CPU及片内总线控制器、显示核 心模块、系统综合控制模块、自定义逻辑功能模块;通过上述多个模块协同配合实现该可穿 戴计算机主板在“系统综合控制功能”、“自定义逻辑功能”、“协处理器与总线功能”、“接口 功能”上的硬件层次的在线升级与扩展;所述配属模块组包括电压调节模块、时钟模块、 JTAG总线模块、JTAG转接模块;其中,所述电压调节模块:用以生成一定占空比的脉冲序列, 打开或关闭片外MOS管或三极管,给所述可变功能芯片或系统其它部分提供PWM电压,控制 外部MOS管或三极管的打开和关闭,进行电源使能或上电时序管理,提供可变功能芯片所需 的各种电压;所述时钟模块:通过片内的锁相环PLL或分频倍频电路结构,提供可变功能芯 片所需的各种时钟或者为外部系统提供时钟信号;所述JTAG总线模块:通过片内的符合 JTAG协议的总线电路结构,提供对可变功能芯片编程下载的支持;所述JTAG转接模块:通过 JTAG协议与USB、COM、LPT、LPC/SPI 协议的转换电路结构,提供将可变功能芯片内的JTAG总 线连接到相应接口或总线的支持;所述系统综合控制模块:用于检测、控制系统当前各个部 分的状态,并将相关信息发送给X86系统SOC以提供上层应用支持;其中,所述系统综合控制 模块由ITP/DXP测试模块、BIOS信息反馈模块、焊点测试模块、电源切换与充电管理模块、加 速度计测量模块、热传感器测量模块、决策支持模块、键盘扫描与编码模块、系统休眠控制 模块、电压调节器使能与状态监测模块、音量控制模块、LCD亮度控制模块、无限装置开关模 块、移位寄存器、USB接口模块、SPI控制器以及寄存器组构成;其中,ITP/DXP测试模块连接 到CPU 和南北桥集成芯片的DXP接口,BIOS信息反馈模块通过LPC或SPI总线与BIOS 芯片相 3 CN 111581151 A 说 明 书 2/6 页 连,对BIOS当前反馈状态进行转译,电源切换与充电管理模块与电池及适配器相连,加速度 计测量模块与加速度计相连,热传感器测量模块与热敏传感器相连,键盘扫描与编码模块 与系统键盘矩阵相连,系统休眠控制模块与南北桥集成芯片的电源管理部分相连,电压调 节器使能与状态监测模块与系统电源模块相连,音量控制模块与系统扬声器相连,LCD亮度 控制模块与LVDS 接口的LCD相连,无线装置开关模块与无线通信模块相连;所述系统级SOC 包括:X86处理器、X86芯片组和显示核心,其中,X86芯片组包括北桥和南桥控制器,所述北 桥和南桥控制器可集成在南北桥集成芯片中”。 以上述发明专利为例,其所解决的技术问题是:针对可穿戴计算机多变的应用需 求和现有技术实现方法存在的功能单一和性能升级和功能扩展不便方面的不足,与本发明 所解决的对于单片机驱动能力重构的技术问题不同。因此,针对上述问题,予以进一步改 进。

技术实现要素:

本发明的主要目的在于提供MCU端口驱动可重构方法,其可以将所有端口在设计 时,进行可重构设计,最后可以把端口都封装出来,这样使用者可以使用可重构设计的端口 MCU时,可以用到这颗MCU的所有的端口,以及所有端口的驱动能力。 本发明的另一目的在于提供MCU端口驱动可重构方法,其可以设计出更有竞争力 的MCU产品,使用者可以最大灵活的使用这颗MCU内部所有端口的驱动能力。 本发明的另一目的在于提供MCU端口驱动可重构方法,可以配置把一个端口配置 成某一个功能,也可以把所有端口配置成一个功能,使用者通过软件配置这些端口之后,这 样使用者可以使用绑定在一起所有端口的所有功能以及所有驱动能力,简单得说,使用这 种可重构配置设计的MCU,可以把几个端口合封在一起,起到功能复用,驱动能力复用,形成 N倍的驱动能力。比如pin1 由3个芯片pad组成并封装在一起,pin1可以选择pad1的单个pad 输出驱动能力,又可以选择pad1 pad2的2个pad输出驱动能力,又可以选择 pad1 pad2 pad3的3个pad输出驱动能力,让使用者得到最大的资源利用。 为达到以上目的,本发明提供一种MCU端口驱动可重构方法,用于增加MCU 的驱动 能力,包括以下步骤: 步骤S1:对MCU进行封装定义(首先查看MCU刚开始的封装定义(即普通封装)是否 将端口都进行封装); 步骤S2:判断封装定义的MCU是否有空余的端口(如果MCU刚开始的封装定义都已 经把所有的端口都进行封装,直接按照刚开始的封装定义即可,也能满足MCU所有的端口和 所有端口的驱动能力); 步骤S3:判断封装定义的MCU的端口是否需要更大的驱动电流能力(如果 MCU刚开 始的封装没有把所有的端口都进行封装,即还有空余的端口,但是使用者在使用时并不需 要所有的端口或者部分封装的端口可以满足电流驱动,则直接按照刚开始的封装定义即 可,不要进行驱动可重构封装,可以根据使用者的需求进行灵活选择); 步骤S4:对MCU进行驱动可重构封装。 作为上述技术方案的进一步优选的技术方案,骤S2具体实施为以下步骤: 步骤S2.1:如果判断MCU有空余的端口,则执行步骤S3; 4 CN 111581151 A 说 明 书 3/6 页 步骤S2.2:如果判断MCU没有空余的端口,则对MCU进行普通封装。 作为上述技术方案的进一步优选的技术方案,骤S3具体实施为以下步骤: 步骤S3.1:如果判断MCU的空余端口需要更大的驱动电流能力,则执行步骤S4; 步骤S3.2:如果判断MCU的空余端口不需要更大的驱动电流能力,则对 MCU进行普 通封装。 作为上述技术方案的进一步优选的技术方案,步骤S4具体实施为以下步骤: 步骤S4.1:(在MCU封装设计时)在MCU至少两个端口封装打线时,将一个端口配置 成一个功能; 步骤S4.2:(在MCU封装设计时)在MCU至少两个端口封装打线时,将所有端口配置 成一个功能(使用这种可重构配置设计的MCU,可以把几个端口合封在一起,起到功能复用, 驱动能力复用,可以把N个端口合二为一输出,形成N倍的驱动能力,比如一个端口驱动电流 为20mA,那么2个端口共同的驱动能力有40mA,N个端口共同的驱动能力基本是N*20mA级 别)。 作为上述技术方案的进一步优选的技术方案,在步骤S4中: MCU的Y端口、IE端口和CS端口分别通过电平转换单元与第一单元电性连接; MCU的PU端口通过电平转换单元与开关电性连接; MCU的DR端、A端和OE端分别通过电平转换单元与第二单元电性连接; MCU的PD端通过电平转换单元与开关电性连接。 作为上述技术方案的进一步优选的技术方案,在步骤S4中: A0端、A1端、A2端和A3端分别连接第一信号选择单元的输入端,A_PA00 端连接第 一信号选择单元的输出端; DR0端、DR1端、DR2端和DR3端分别连接第二信号选择单元的输入端, DR_PA00端连 接第二信号选择单元的输出端; IE0端、IE1端、IE2端和IE3端分别连接第三信号选择单元的输入端,IE_PA00端连 接第三信号选择单元的输出端; PU0端、PU1端、PU2端和PU3端分别连接第四信号选择单元的输入端, PU_PA00端连 接第四信号选择单元的输出端。 附图说明 图1是本发明的MCU端口驱动可重构方法的流程示意图。 图2是本发明的MCU端口驱动可重构方法的MCU端口示意图。 图3是本发明的MCU端口驱动可重构方法的信号选择示意图。 图4是本发明的MCU端口驱动可重构方法的LQFP80的端口封装示意图。 图5是本发明的MCU端口驱动可重构方法的LQFP32的端口封装示意图。 图6是现有的MCU端口封装示意图。 图7是本发明的MCU端口驱动可重构方法的MCU端口封装示意图。