技术摘要:

本发明公开了一种半导体器件,该半导体器件包括被配置用于安装半导体管芯(108)的引线框架桨状件(114、312、412、512)。该半导体器件还包括形成在引线框架桨状件(114、312、412、512)上的电镀区域(304、404A‑404I、504)。该电镀区域(304、404A‑404I、504)被配置为从放 全部

背景技术:

半导体器件、集成电路、片上系统(SoC)和其他电子器件可以在芯片封装中制造。 芯片封装可以包括连接件和结构,以将封装内的半导体元件连接到封装内的其他部件和外 部元件。为了经由引线、引脚、管芯焊盘和类似连接件来连接半导体元件,封装可以包括引 线框架。引线框架可以由金属薄层制成。引线框架可以包括半导体元件可以附接到其上的 焊盘或桨状件。半导体元件可以置于引线框架的焊盘或桨状件上。 可以在芯片封装内制造多种连接件以连接封装中的各种元件。此类连接件可以包 括焊线、下接合和环氧树脂。 分层是一种可能影响芯片封装中的连接件的状况。分层可以包括封装内的两种材 料之间的分离。分层可能导致失效。某些区域中的分层导致可靠性风险,并且可能导致其他 失效。此类其他失效可以包括管芯腐蚀、封装破裂、接合脱离以及接合的颈部或根部的断 裂。分层还可能通过改变各种操作参数而导致集成电路故障。

技术实现要素:

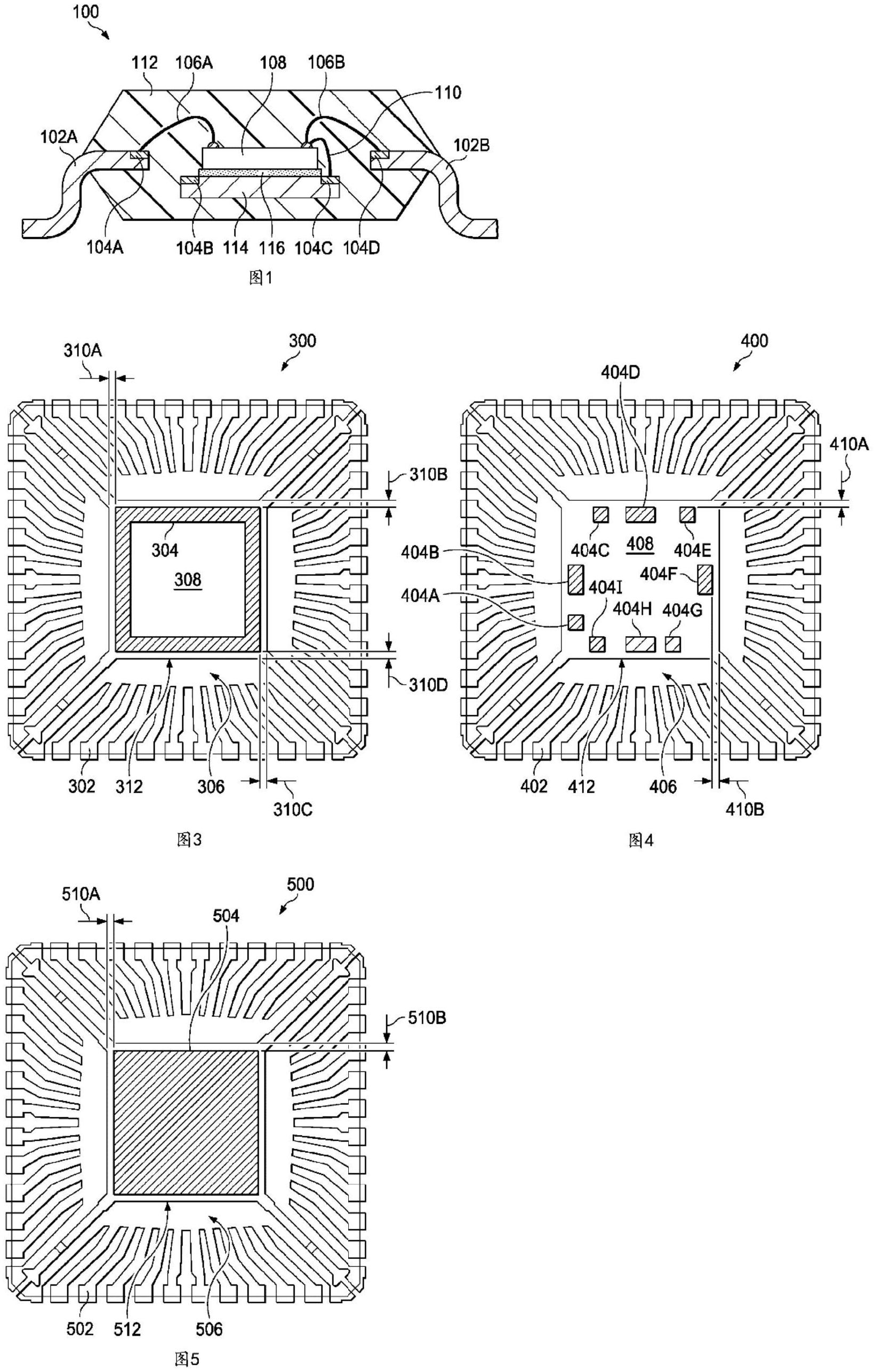

本公开的实施方案包括装置。该装置可以包括被配置用于安装半导体管芯的引线 框架桨状件。该装置还可以包括形成于引线框架桨状件上的电镀区域。该电镀区域可以被 配置为从置于引线框架桨状件上的半导体管芯接收下接合。装置可以包括暴露间隙,该暴 露间隙位于电镀区域的外边缘与引线框架桨状件的外边缘之间。结合上述实施方案中的任 一个,电镀区域可以由银形成。结合上述实施方案中的任一个,暴露间隙可以由铜形成。结 合上述实施方案中的任一个,电镀区域可以形成为围绕引线框架桨状件的周边的环。结合 上述实施方案中的任一个,装置还可以包括电镀区域内的中空部分,其中中空部分位于放 置在引线框架桨状件上的半导体管芯的下方。结合上述实施方案中的任一个,电镀区域可 以形成为引线框架桨状件上的矩形,矩形与所述引线框架桨状件的周边同延。结合上述实 施方案中的任一个,装置还可以包括附加电镀区域,其中每个附加电镀区域包括在该附加 电镀区域的外边缘与引线框架桨状件的外边缘之间的另外的暴露间隙。 本公开的实施方案包括一种集成电路封装。集成电路封装可以包括被配置用于安 装半导体管芯的引线框架桨状件。集成电路封装还可以包括形成在引线框架桨状件上的电 镀区域。电镀区域可以被配置为从置于引线框架桨状件上的半导体管芯接收下接合。集成 4 CN 111602242 A 说 明 书 2/6 页 电路封装可以包括暴露间隙,暴露间隙位于电镀区域的外边缘与引线框架桨状件的外边缘 之间。结合上述实施方案中的任一个,电镀区域可以由银形成。结合上述实施方案中的任一 个,暴露间隙可以由铜形成。结合上述实施方案中的任一个,电镀区域可以形成为围绕引线 框架桨状件的周边的环。结合上述实施方案中的任一个,集成电路封装还可以包括电镀区 域内的中空部分,其中该中空部分位于放置在引线框架桨状件上的半导体管芯的下方。结 合上述实施方案中的任一个,电镀区域可以形成为引线框架桨状件上的矩形,该矩形与引 线框架桨状件的周边同延。结合上述实施方案中的任一个,集成电路封装还可以包括附加 电镀区域,其中每个附加电镀区域包括在附加电镀区域的外边缘与引线框架桨状件的外边 缘之间的另外的暴露间隙。 本公开的实施方案可以包括用于形成或构建上述装置或集成电路封装中的任一 个的方法。所述方法可以包括形成引线框架桨状件、在引线框架桨状件上形成电镀区域、以 及在电镀区域的外边缘与引线框架桨状件的外边缘之间形成暴露间隙。结合上述实施方案 中的任一个,所述方法可以包括将半导体器件安装在引线框架桨状件上。结合上述实施方 案中的任一个,所述方法可以包括形成从半导体管芯到电镀区域的下接合。结合上述实施 方案中的任一个,电镀区域可以由银形成。结合上述实施方案中的任一个,暴露间隙可以由 铜形成。结合上述实施方案中的任一个,所述方法可以包括将电镀区域形成为围绕引线框 架桨状件的周边的环。结合上述实施方案中的任一个,所述方法可以包括将电镀区域形成 为引线框架桨状件上的矩形,矩形与引线框架桨状件的周边同延。结合上述实施方案中的 任一个,所述方法可以包括在引线框架桨状件上形成附加电镀区域,其中每个附加电镀区 域包括在附加电镀区域的外边缘与引线框架桨状件的外边缘之间的另外的暴露间隙。结合 上述实施方案中的任一个,所述方法可以包括形成从半导体管芯到附加电镀区域中的每个 附加电镀区域的下接合。 附图说明 图1是根据本公开的实施方案的示例性芯片封装的图示。 图2为具有分层的芯片封装的图示。 图3是根据本公开的实施方案的在引线框架中具有银环的芯片封装的顶视图。 图4是根据本公开的实施方案的在引线框架中具有隔离的银或银岛的芯片封装的 顶视图。 图5是根据本公开的实施方案的在引线框架中具有矩形镀银区域的芯片封装的顶 视图。 图6示出了在电镀区域与引线框架桨状件的边缘之间无间隙的芯片封装。