技术摘要:

一种半导体结构及其形成方法,形成方法包括:提供基底,基底上形成有栅极结构,栅极结构两侧的基底内形成有源漏掺杂层,基底上形成有保形覆盖源漏掺杂层及其露出的栅极结构侧壁的刻蚀停止层,栅极结构露出的基底上形成有层间介质层;在栅极结构两侧的层间介质层和刻蚀 全部

背景技术:

随着集成电路制造技术的不断发展,人们对集成电路的集成度和性能的要求变得 越来越高。为了提高集成度,降低成本,元器件的关键尺寸不断变小,集成电路内部的电路 密度越来越大,这种发展使得晶圆表面无法提供足够的面积来制作所需要的互连线。 为了满足关键尺寸缩小过后的互连线所需,目前不同金属层或者金属层与基底的 导通是通过互连结构实现的。互连结构包括互连线和形成于接触开口内的接触孔插塞。接 触孔插塞与半导体器件相连接,互连线实现接触孔插塞之间的连接,从而构成电路。 晶体管结构内的接触孔插塞包括位于栅极结构表面的接触孔插塞,用于实现栅极 结构与外部电路的连接,还包括位于源漏掺杂层表面的接触孔插塞,用于实现源漏掺杂层 与外部电路的连接。

技术实现要素:

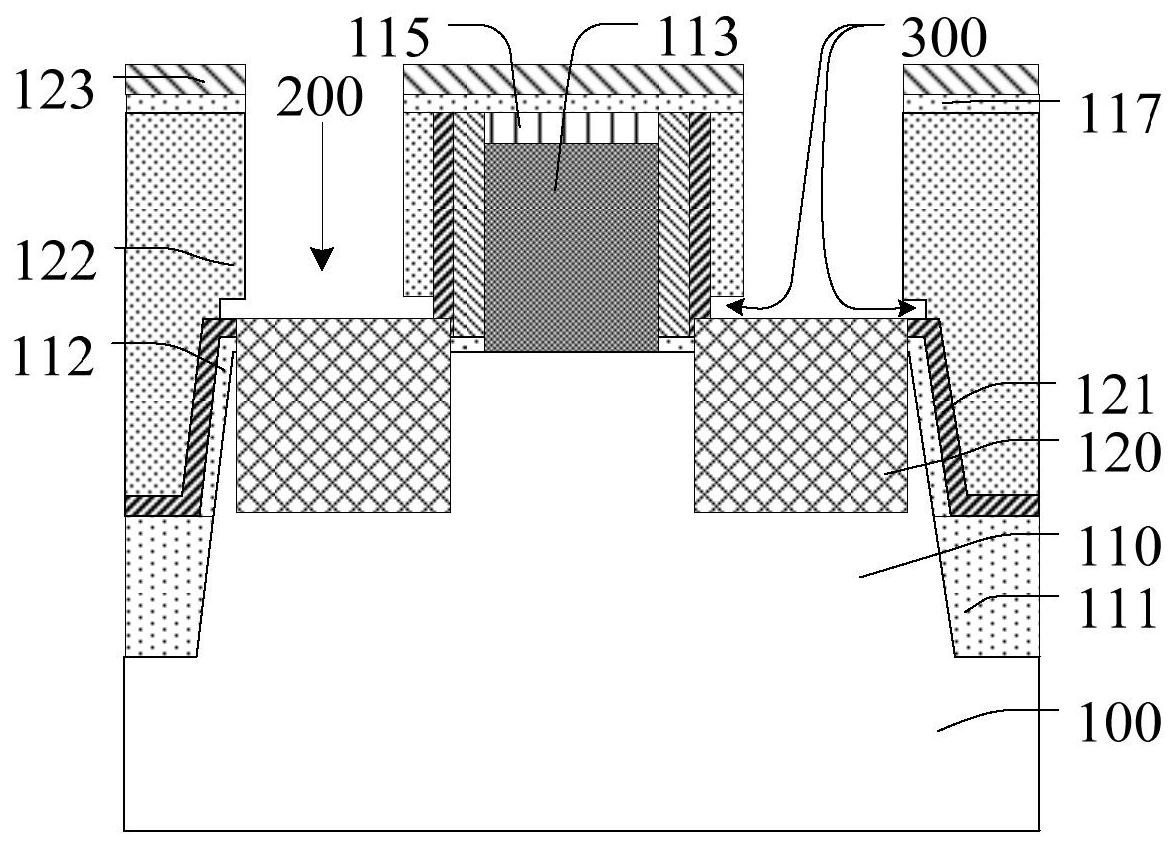

本发明实施例解决的问题是提供一种半导体结构及其形成方法,提升半导体结构 的性能。 为解决上述问题,本发明实施例提供一种半导体结构的形成方法,包括:提供基 底,所述基底上形成有栅极结构,所述栅极结构两侧的基底内形成有源漏掺杂层,所述基底 上形成有保形覆盖所述源漏掺杂层、以及所述源漏掺杂层露出的栅极结构侧壁的刻蚀停止 层,所述栅极结构露出的基底上形成有层间介质层,所述层间介质层覆盖所述刻蚀停止层 且露出所述栅极结构顶部;在所述栅极结构两侧的层间介质层和刻蚀停止层内形成接触 孔,所述接触孔露出所述源漏掺杂层顶部,且所述接触孔侧壁与位于栅极结构侧壁上的刻 蚀停止层之间保留有部分宽度的层间介质层;沿垂直于所述接触孔侧壁的方向,刻蚀所述 接触孔侧壁露出的刻蚀停止层,形成由所述层间介质层、剩余所述刻蚀停止层和源漏掺杂 层围成的沟槽;形成填充所述沟槽和接触孔的接触孔插塞,所述接触孔插塞与源漏掺杂层 电连接。 相应的,本发明实施例还提供一种半导体结构,包括:基底;栅极结构,位于所述基 底上;源漏掺杂层,位于所述栅极结构两侧的基底内;倒T形结构的接触孔插塞,位于所述源 漏掺杂层上且与所述源漏掺杂层电连接,所述接触孔插塞包括底部接触孔插塞、以及凸出 于所述底部接触孔插塞的顶部接触孔插塞;刻蚀停止层,覆盖所述接触孔插塞露出的源漏 掺杂层、以及所述接触孔插塞和源漏掺杂层露出的栅极结构侧壁,所述刻蚀停止层和所述 底部接触孔插塞相接触;层间介质层,位于所述栅极结构露出的基底上,所述层间介质层覆 盖所述顶部接触孔插塞露出的刻蚀停止层和底部接触孔插塞,且露出所述栅极结构顶部。 与现有技术相比,本发明实施例的技术方案具有以下优点: 本发明实施例在形成所述接触孔后,还沿垂直于所述接触孔侧壁的方向,刻蚀所 4 CN 111554578 A 说 明 书 2/12 页 述接触孔侧壁露出的刻蚀停止层,形成由所述层间介质层、剩余所述刻蚀停止层和源漏掺 杂层围成的沟槽,与未形成所述沟槽的方案相比,后续形成接触孔插塞后,所述接触孔插塞 还位于所述沟槽内,从而增大了所述接触孔插塞和源漏掺杂层之间的接触面积,因此,通过 合理设定接触孔侧壁与位于栅极结构侧壁上刻蚀停止层之间的层间介质层的厚度,在使得 所述栅极结构和接触孔插塞所形成的边缘寄生电容满足工艺要求的情况下,易于通过增加 所述接触孔插塞和源漏掺杂层之间的接触面积的方式,降低所述接触孔插塞和源漏掺杂层 之间的接触电阻,从而提升半导体结构的性能,例如:减小漏端输入电压的电压降、增大有 效驱动电流Ieff、以及减小后端(Back End Of Line,BEOL)RC延迟等。 附图说明 图1至图3是一种半导体结构的形成方法中各步骤对应的结构示意图; 图4至图11是本发明半导体结构的形成方法一实施例中各步骤对应的结构示意 图。