技术摘要:

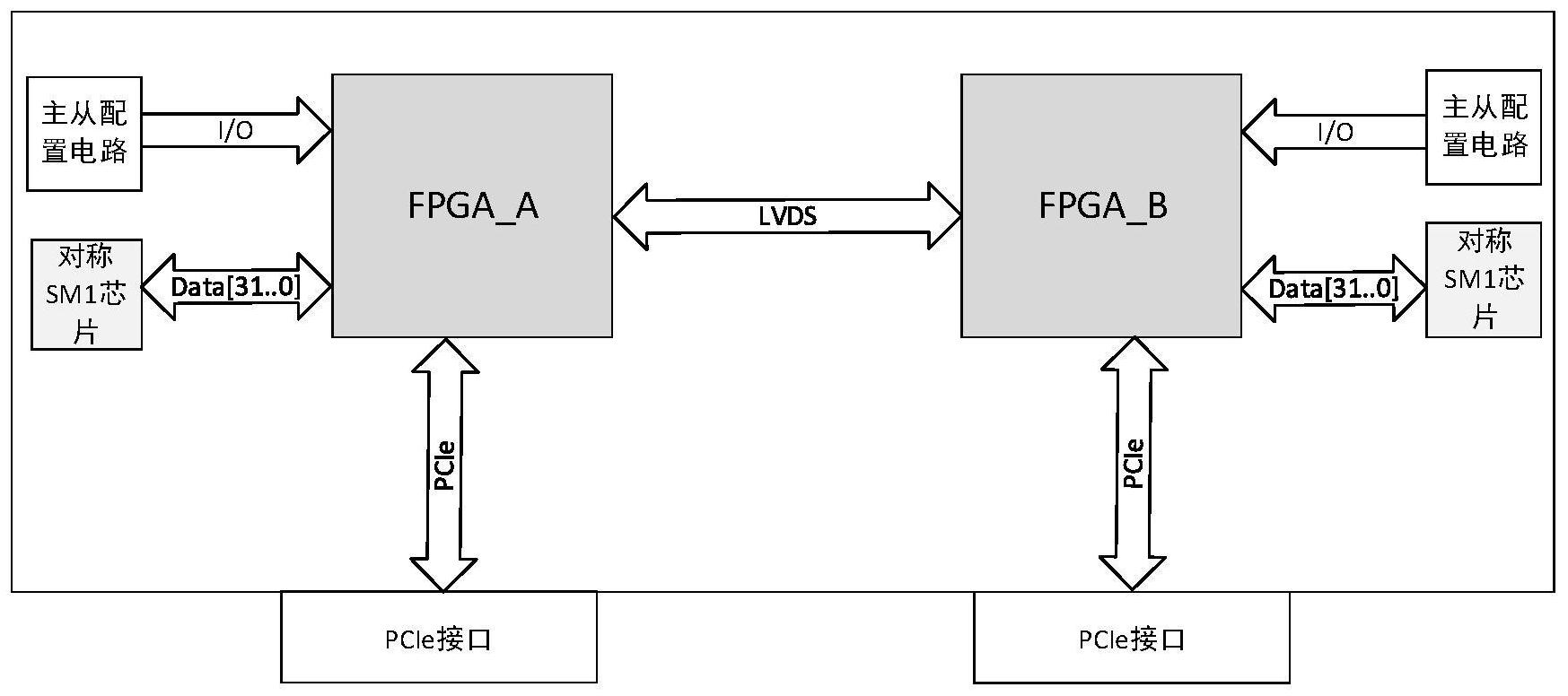

本发明公开了一种基于自协商机制的隔离卡,包括相互通信的两个FPGA芯片,分别与FPGA连接的对称算法SM1芯片及主从配置电路模块。两FPGA芯片通过PCIe接口分别与设备的内外网两端通信,两片FPGA之间通过高速串行接口通信,与算法芯片之间采用本地总线方式进行数据交互。本 全部

背景技术:

根据《电力监控系统安全防护总体方案》(国能安全[2015]36号)要求,在不同安全 区域之间要采取隔离措施,其中在生产控制大区与管理信息大区之间要部署单向数据传输 隔离装置。传统网络隔离装置的基本结构是两个完全独立的主机系统和一个数据摆渡板。 为了进一步增加数据传输保密性,在传统网络安全隔离装置的基础上增加了数据加解密功 能。数据由主机送到隔离卡上,首先对数据进行加解密处理,再对数据进行单向传输。确保 数据在不同安全区域之间传输也处于密文状态。 现有的数据隔离卡一般有电子开关、单向FIFO、光纤和使用协处理器(FPGA等)传 输数据四种方式,目前最广泛应用的是使用协处理器的方式。对数据的加解密功能则主要 有主机系统上通过软件实现数据加解密和分离的加解密模块这两种方式。软件加解密方式 在安全性上得不到保障,主要有密钥不安全、易破解等安全性问题,且加解密性能对主机系 统的性能有很大的依赖性,传输效率受限等问题。分离的加解密模块一般做成一块独立的 加密卡,加密卡上的核心器件主要包括CPU和密码芯片等,一般通过高速串行接口和主机进 行数据交换,通过密码芯片对数据进行加解密处理。分离的加密模块提高了系统的安全性, 但与传统的网络隔离装置相比,增加了一个独立板卡,同时也增加了多次数据交互,在传输 效率上大幅降低,同时增加了硬件成本。

技术实现要素:

本发明的目的在于提供了一种基于自协商机制的隔离卡,设计一种会话密钥自协 商机制,使用FPGA指纹作为会话密钥协商的身份信息,提高了数据的传输效率。 为了达到上述目的,本发明所采用的技术方案是: 一种基于自协商机制的隔离卡,包括两个FPGA芯片,每个FPGA芯片各连接一个对称SM1 算法芯片和一个主从配置电路; 所述两个FPGA芯片之间通过高速串行接口进行通信; 所述两个FPGA芯片通过PCIe接口分别与内、外网主机通信; 每个FPGA芯片用于与对端FPGA芯片进行会话密钥的协商,并将与之相连的主机内存中 的数据基于协商密钥进行加解密处理后发送至对端FPGA芯片,以及将对端FPGA芯片发送的 数据写入到本侧主机内存中; 所述对称SM1算法芯片用以对与其连接的FPGA芯片缓存的数据包进行加解密运算; 所述主从配置电路用于表示内、外网侧FPGA芯片的主从模式。 进一步的,每个FPGA芯片包括DMA控制器、数据解析模块、SM1算法芯片控制模块、 自协商模块、杂凑算法模块、数据接收模块和中断控制模块; 所述DMA控制器用于将与之相连的主机内存中的数据读入到FPGA芯片中的FIFO中缓 4 CN 111600705 A 说 明 书 2/5 页 存,以及将对端FPGA芯片处理完成并传输过来的数据写入到本侧主机内存中; 所述数据解析模块用于将FIFO中缓存的数据进行解析并根据数据包格式分别写入到 不同的下级FIFO中缓存; 所述SM1算法芯片控制模块用于将FIFO中缓存的数据包以及杂凑算法模块产生的协商 会话密钥和初始相量发送至对称SM1算法芯片,以及将对称SM1算法芯片加解密后的数据包 返回至FIFO中缓存; 所述自协商模块用于进行通信两端会话密钥的协商; 所述杂凑算法模块用于对协商因子进行杂凑产生协商会话密钥和初始相量; 所述数据接收模块用于接收对端FPGA芯片传输过来的数据包; 所述中断控制模块用于发送中断到本侧主机,通知本侧主机读取数据。 进一步的,每个FPGA芯片带有GTP/GTX接口。 进一步的,所述对称SM1算法芯片选用SSX30-D密码芯片。 进一步的,每个FPGA芯片选用XC7A75T FPGA芯片。 进一步的,所述下级FIFO包括明文透传FIFO和SM1算法芯片缓存FIFO;所述明文透 传FIFO用于缓存无需加解密的数据包,并通过高速串行接口传输到对端FPGA芯片;所述SM1 算法芯片缓存FIFO用于缓存需要加解密的数据包,并在SM1算法芯片控制模块的控制下,将 数据包写入到对称SM1算法芯片;以及将加解密后的数据包通过高速串行接口传输到对端 FPGA芯片。 进一步的,所述自协商模块具体用于, 从设备指纹模块获协商因子; 调用杂凑算法模块进行计算; 将计算的协商会话密钥和初始相量经由SM1算法芯片控制模块发送给对称SM1算法芯 片。 进一步的,所述自协商模块具体用于, 发起会话密钥协商的主端FPGA的自协商模块读取自身的128位设备指纹数据ID(m),作 为密钥协商因子之一,同时产生128位随机数r1组成256位密钥协商参数( ID(m) || r1 ) 发送给从端FPGA的自协商模块; 从端FPGA的自协商模块读取自身128位设备指纹数据ID(s),作为密钥协商因子之一, 同时产生128位随机数r2组成256位密钥协商参数( ID(s) || r2 )发送给主端FPGA的自协 商模块; 主端FPGA的自协商模块根据从端发来的协商因子,调用杂凑算法模块; 从端FPGA的自协商模块根据主端发来的协商因子,调用杂凑算法模块。 进一步的,所述杂凑算法模块具体用于, 主端FPGA的杂凑算法模块对协商因子进行杂凑H( (ID(m) || r1) ⊕ (ID(s) || r2) ),产生的256位杂凑结果前128位为会话密钥K,后128位作为初始相量IV; 从端FPGA的杂凑算法模块对协商因子进行杂凑H( (ID(s) || r2) ⊕ (ID(m) || r1) ),产生的256位杂凑结果前128位为会话密钥K,后128位作为初始相量IV。 进一步的,所述中断控制模块使用MSI中断方式,并根据主机的CPU核个数动态调 整中断数。 5 CN 111600705 A 说 明 书 3/5 页 本发明所达到的有益效果为: 本发明将对称SM1算法芯片设置在数据隔离卡内,同时去掉非对称算法SM2芯片,结合 数据隔离卡使用场景的特点,设计一种会话密钥自协商机制,通过两个FPGA芯片进行会话 密钥的协商,不占用主机资源,,具有速度快、集成度高、成本低、易移植的特点。 附图说明 图1为本发明所提供的数据隔离卡的结构框图; 图2为本发明基于自协商机制的隔离卡中FPGA芯片逻辑框图。