技术摘要:

本发明公开一种纳米线晶体管元件。具体是公开一种互补式金属氧化物半导体元件,包含基底,包括第一元件区和第二元件区。多个第一纳米线形成于该基底上并位于该第一元件区中,各该第一纳米线分别包含第一半导体核心以及第二半导体核心,其中该第二半导体核心环绕该第一 全部

背景技术:

当元件发展至65纳米技术世代后,使用传统平面式(planar)的金属氧化物半导体 (metal-oxide-semiconductor,MOS)晶体管制作工艺难以持续微缩,因此,现有技术提出以 立体或非平面(non-planar)多栅极晶体管元件取代平面晶体管元件的解决途径。举例来 说,双栅极(dual-gate)鳍式场效晶体管(Fin Field effect transistor,以下简称为 FinFET)元件、三栅极(tri-gate)FinFET元件、以及Ω(omega)式FinFET元件等都已被提出。 现在,则更发展出利用纳米线作为通道的全栅极(gate-all-around,GAA)晶体管元件,作为 继续提升元件积成度与元件效能的方案。

技术实现要素:

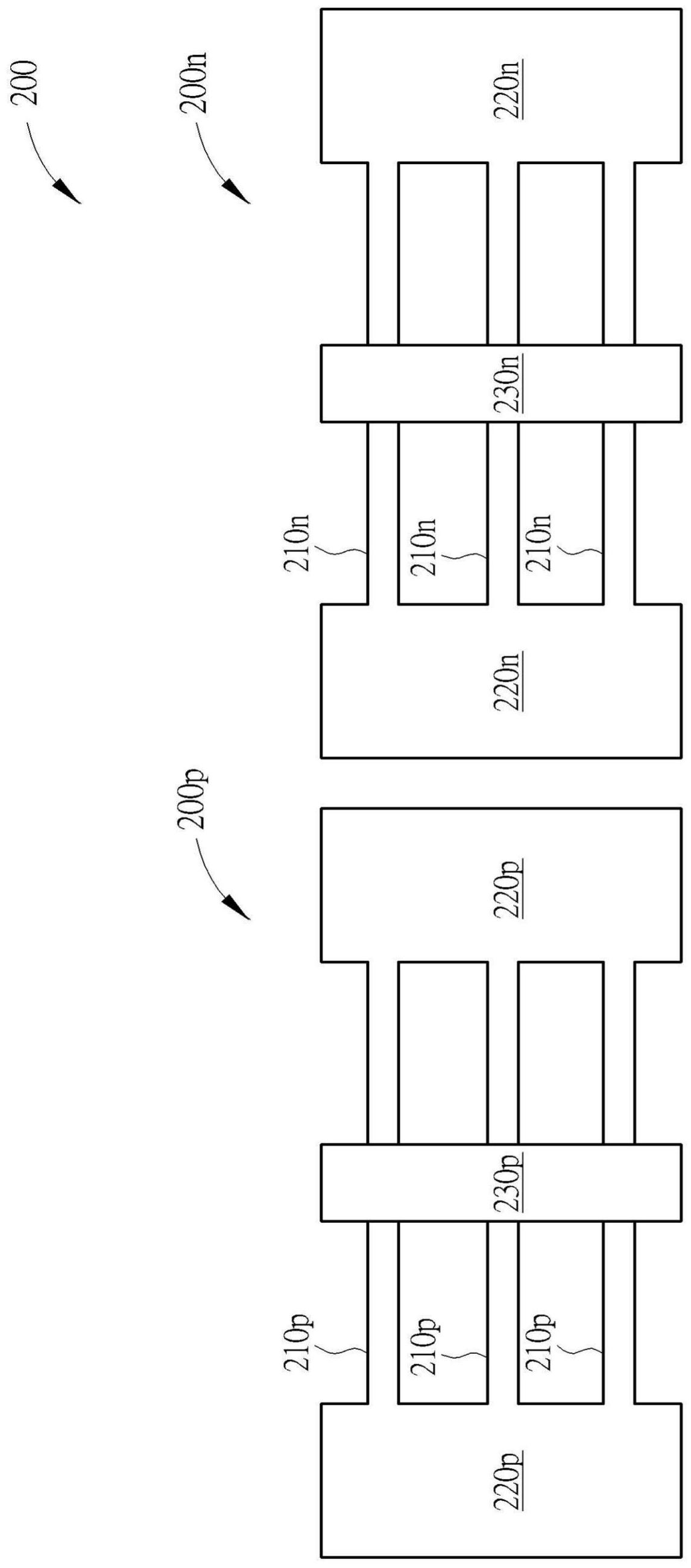

本发明的目的在于提供一种纳米线晶体管元件及其制作方法。 为达上述目的,本发明提供了一种互补式金属氧化物半导体元件,包含基底,包括 第一元件区和第二元件区。多个第一纳米线形成于该基底上并位于该第一元件区中,各该 第一纳米线分别包含第一半导体核心以及第二半导体核心,其中该第二半导体核心环绕该 第一半导体核心,且该第二半导体核心的一晶格常数不同于该第一半导体核心的一晶格常 数。多个第二纳米线,形成于该基底上并位于该第二元件区中,其中各该第二纳米线包含该 第一半导体核心。第一栅极,环绕部分的各该第一纳米线。第二栅极,环绕部分的各该第二 纳米线。 为达上述目的,本发明又提供了一种纳米线晶体管元件,包括基底,该基底包含凹 槽。纳米线,悬置于该凹槽上,其中该纳米线包含第一半导体核心以及第二半导体核心,其 中该第二半导体核心环绕该第一半导体核心,且该第二半导体核心的一晶格常数不同于该 第一半导体核心的一晶格常数。栅极,环绕部分的该纳米线。 根据本发明所提供的纳米线晶体管元件的制作方法,对已形成有纳米线的基底进 行至少一次SEG制作工艺,而于纳米线表面形成另一晶格常数不同于纳米线的半导体外延 层,用以增加纳米线通道的载流子迁移率。是以,本发明所提供的纳米线晶体管元件为一多 核心(multiple core)纳米线晶体管元件,该多核心纳米线晶体管元件的各纳米线通道分 别包含至少第一半导体核心与第二半导体核心,第一半导体核心被第二半导体核心环绕与 包覆,而第二半导体核心则作为具有较高载流子迁移率(carrier mobility)的纳米线通道 (nanowire channel)。 4 CN 111584625 A 说 明 书 2/9 页 附图说明 图1A至图2C为本发明所提供的一纳米线晶体管元件及其制作方法的一第一优选 实施例的示意图,其中 图1B为图1A中沿A-A’切线获得的剖视图; 图2B为图2A中沿A-A’切线获得的剖面放大图;以及 图2C为图2A中沿B-B’切线获得的剖视图; 图3A至图3C,图3A至图3C为本发明所提供的一纳米线晶体管元件及其制作方法的 一第二优选实施例的示意图,其中 图3B为图3A中沿A-A’切线获得的剖视图;以及 图3C为图3A中沿B-B’切线获得的剖面放大图; 图4至图5为本发明所提供的一纳米线晶体管元件及其制作方法的一第三优选实 施例的示意图; 图6为本发明所提供的一纳米线晶体管元件及其制作方法的变化型的示意图; 图7至图8为本发明所提供的一纳米线晶体管元件及其制作方法的一第四优选实 施例的示意图。 其中,附图标记说明如下: 100、200 SOI基底 200p pMOS元件区 200n nMOS元件区 102 基底 102d 掺杂区 104 绝缘层 104r 凹槽 106 半导体层 107、108 外延层 110、210p、210n 纳米线 112 第一半导体核心 114 第二半导体核心 116 第三半导体核心 120、220p、220n 连接垫 122、240 图案化硬掩模 130、230p、230n 栅极 A-A’、B-B’ 切线