技术摘要:

本申请公开了一种延迟电路、时钟控制电路以及控制方法,延迟电路,包括藕接成一链的N级延迟单元,每级延迟单元包括四态门电路和反相电路,每级的四态门电路和反相电路的输入端相连,反相电路的另一输入端与下一级反相电路的输出相连;输入信号连接至第一级四态门电路、 全部

背景技术:

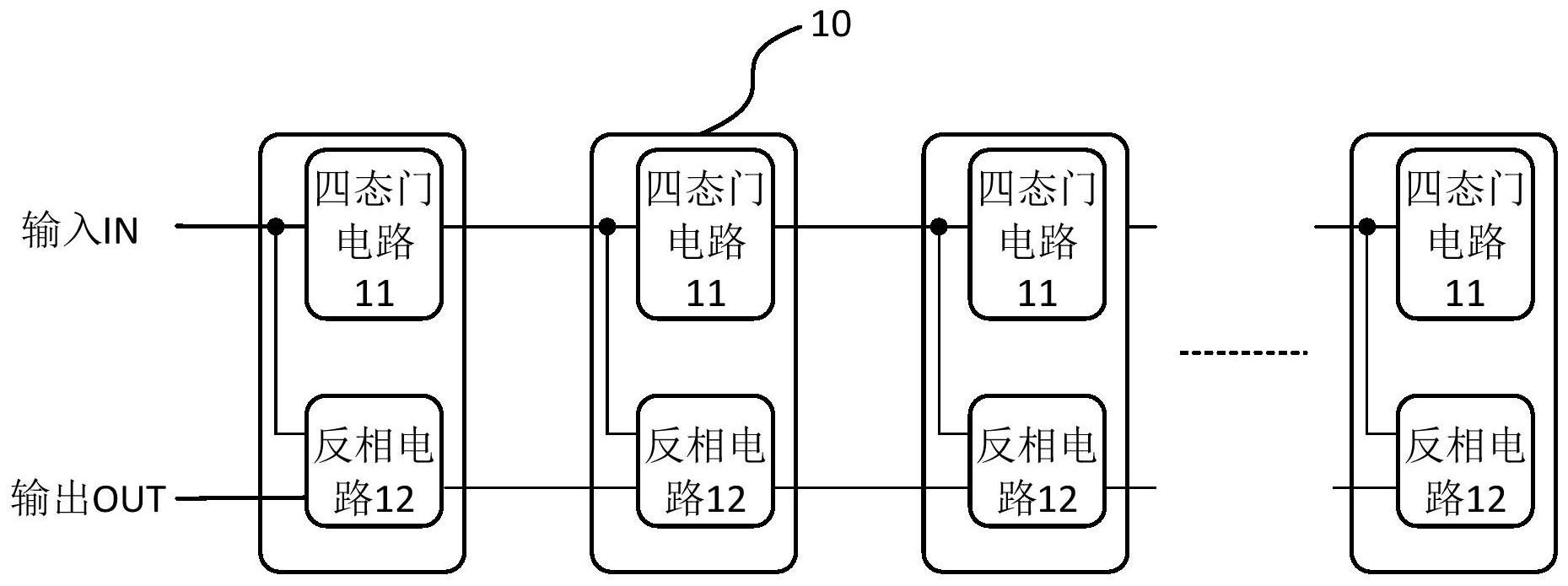

延迟元件是一些集成电路和系统中的时钟分配网络的构造块。延迟元件用于限定 数据在这些系统内传输(movement)的时间基准。可变延迟元件是用于在高速数字集成电路 中进行精细、精确和准确的脉冲延迟(或相位)控制的基于反相器的电路。为了实现范围较 宽的延迟或相位调整,可变延迟元件被是实现为反相器链。反相器链被称为延迟线。在许多 集成电路中,在诸如DLL(延迟锁相环)、TDC(时间-数字转换器)、VCO(压控振荡器)、脉宽控 制环(PWCL)等的系统中使用延迟线。在这些应用中,可变延迟元件被用于精确和准确的脉 冲时间基准。 现有的延迟线电路结构存在以下缺陷:在延迟控制信号切换时产生毛刺;输出信 号占空比损失随延迟线级数增加而增加;输入负载随延迟线级数增加而线性增加。 申请内容 本申请采用一种简单易行的延迟单元,避免了控制信号切换时的毛刺,同时不损 失占空比。 在一个实施例中,本申请提供一种延迟电路,包括藕接成一链的N级延迟单元,每 级延迟单元包括四态门电路和反相电路,每级的四态门电路和反相电路的输入端相连,反 相电路的另一输入端与下一级反相电路的输出相连;输入信号连接至第一级四态门电路、 反相电路的输入端,并逐级通过四态门电路、反相电路延迟一定时间输出。 在另一个实施例中,本申请提供一种时钟控制电路,包括上述实施例中的延迟电 路,时钟信号和屏蔽信号通过逻辑门连接至所述延迟电路的输入端;所述延迟电路的输出 端连接逻辑电路模块。 在另一个实施例中,本申请提供一种时钟控制方法,包括:控制第0至M-1级反相单 元打开、上拉单元、下拉单元关闭,第M级反相单元关闭;控制第0至M-1级第一反相器关闭、 第二反相器打开,第M级第一反相器打开、第二反相器关闭;时钟输入信号依次通过第0至M- 1级反相单元、第M级第一反相器、第M-1级至第0级第二反相器输出。 与现有技术相比,本申请至少具有以下有益效果: 1)每一级延迟单元都完全相同,因此每级反相电路随工艺、电压、温度偏移造成的 占空比损失也会被下一级反相电路完全补偿,从而没有占空比损失。 2)延迟电路的内部节点电压成为稳定的高低电平交替分布,此时无论控制信号切 换到任意一级打开或关闭,延时线内部节点电压仍然为稳定的高低电平交替分布,切换时 不产生任何毛刺信号。 4 CN 111726108 A 说 明 书 2/4 页 附图说明 本申请通过所附的附图用示例形式展示。附图应当被理解为作为示例而非限制, 本申请的范围是由权利要求所限定的。 图1是表示延迟电路实施例的框图。 图2是表示四态门电路实施例的框图。 图3是表示四态门电路实施例的图。 图4是表示延迟单元实施例的图。 图5是表示时钟控制电路实施例的图。 图6是表示时钟控制电路另一个实施例的图。 图7是表示一种实施例中时钟控制方法的流程图。 图8是表示另一种实施例时钟控制方法的流程图。 图9是表示另一种实施例时钟控制方法的流程图。

技术实现要素:

参考图1所示,延迟电路包括藕接成一链的N级延迟单元10,每级延迟单元10包括 四态门电路11和反相电路12,每级的四态门电路11和反相电路12的输入端相连,反相电路 12的另一输入端与下一级反相电路12的输出相连,输入信号IN连接至第一级四态门电路 11、反相电路12的输入端,逐级通过四态门电路11、反相电路12延迟一定时间输出OUT。 参考图2所示,所述四态门电路11包括反相单元111、上拉单元112、下拉单元113, 所述反相单元111、上拉单元112、下拉单元113的输出相连至下一级反相单元111的输入。 参考图3所示,所述反相单元111包括第一PMOS晶体管P1、第二PMOS晶体管P2、第一 NMOS晶体管N1、第二NMOS晶体管N2; 所述第一PMOS晶体管P1和第一NMOS晶体管N1的栅极连接至上一级反相单元111的 输出,其漏极连接至下一级反相单元111的输入; 所述第一PMOS晶体管P1的源极连接第二PMOS晶体管P2的漏极,第二PMOS晶体管P2 的源极接电源,其栅极连接第一控制指令enb; 所述第一NMOS晶体管N1的源极连接第二NMOS晶体管N2的漏极,第二NMOS晶体管N2 的源极接地,其栅极连接第二控制指令en,其中第一控制指令enb和第二控制指令en是一对 反相的控制信号。 所述上拉单元112包括第三PMOS晶体管P3,其栅极连接第三控制指令pu,源极接电 源,漏极连接下一级反相单元111的输入,通过第三控制指令pu打开第三PMOS晶体管P3,将 四态门电路10的输出端拉升为高电平,并稳定为高电平。 所述下拉单元113包括第三NMOS晶体管N3,其栅极连接第四控制指令pd,源极接 地,漏极连接下一级反相单元111的输入,通过第四控制指令pd打开第三NMOS晶体管N3,将 四态门电路10的输出端下拉为低电平,并稳定为低电平。 所述四态门电路11至少具有三种工作模式,分别为:反相单元111打开,上拉单元 112、下拉单元113关闭,输出端信号取反;反相单元111、上拉单元112打开,下拉单元113关 闭,输出端恒为高电平;反向单元111、下拉单元113打开,上拉单元112关闭,输出端恒为低 电平。此外,本申请的四态门电路11中反相单元111、上拉单元112、下拉单元113均关闭的情 5 CN 111726108 A 说 明 书 3/4 页 况下,四态门电路处于高阻状态,具有高阻工作模式。 参考图4所示,所述反相电路12包括第一反相器121、第二反相器122,所述第一反 相器121、第二反相器122的输出端相连接,所述第一反相器121的输入连接同一级反相单元 111的输入端,下一级第二反相器122的输出端连接上一级第二反相器122的输入端,所述第 一反相器121连接第一控制指令enb,第二反相器122连接第二控制指令en。第一反相器121、 第二反相器122分别处于打开或关闭的状态(例如,第一反相器121打开、第二反相器122关 闭,或者第一反相器121关闭、第二反相器122打开),使得四态门电路10的信号选择性通过 反相电路12输出。 在另一个实施例中,参考图5所示,本申请还提供一种时钟控制电路20,包括上述 实施例中的延迟电路21,时钟信号clk_in和屏蔽信号gate_en通过一与逻辑门23连接至所 述延迟电路的21输入端IN,屏蔽信号gate_en通过反相器24连接至与逻辑门23的输入端;所 述延迟电路21的输出端OUT连接逻辑电路模块22。所述延迟电路21还包括输入信号Vinit和 控制信号Code,如图4所示,输入信号Vinit连接至第N级第二反相单元122的输入端。控制信 号Code用于控制延迟电路21输出锁定时间。 在另一个实施例中,参考图6所示,本申请还提供一种时钟控制电路30,包括上述 实施例中的延迟电路21,时钟信号clk_in和屏蔽信号gate_en通过一或逻辑门33连接至所 述延迟电路的31输入端IN;所述延迟电路21的输出端OUT连接逻辑电路模块32。所述延迟电 路31还包括输入信号Vinit和控制信号Code,输入信号Vinit连接至第N级第二反相单元122 的输入端。控制信号Code用于控制延迟电路31输出锁定时间。 在另一个实施例中,结合图4、图7所示,本申请还提供一种时钟控制方法,包括: S110,控制第0至M-1级反相单元111打开、上拉单元112、下拉单元113关闭,第M级 反相单元111、上拉单元112、下拉单元113关闭,此时四态门电路11对输入信号取反; S120,控制第0至M-1级第一反相器121关闭、第二反相器122打开,第M级第一反相 器121打开、第二反相器122关闭,使得延迟电路的输入信号依次经过M-1级四态门电路,并 依次通过第M级第一反相器、第M-1至0级第二反相器122输出; S130,屏蔽信号gate_en关闭,时钟信号延迟一定时间输出。其中屏蔽信号gate_en 为低电平,时钟信号clk_in输入至延迟电路输入端IN,时钟信号依次通过第0至M-1级反相 单元111、第M级第一反相器121、第M-1级至第0级第二反相器122延迟一定时间输出,实现时 钟信号M级延迟。 本实施例中,每一级反相电路都完全相同,因此每级反相电路随工艺、电压、温度 偏移造成的占空比损失也会被下一级反相电路完全补偿,从而没有占空比损失。 结合图4、图5、图8所示,另一个实施例中,本申请的时钟控制方法,包括: S210,控制第0至M-1级反相单元111打开、上拉单元112、下拉单元113关闭,第M级 反相单元111、下拉单元113关闭,第M级上拉单元112打开,此时第M级四态门电路11的输出 端被拉升为高电平,并保持为高电平,其中M为0~N之间的自然数; S220,控制第0至M-1级第一反相器121关闭、第二反相器122打开,第M级第一反相 器121打开、第二反相器122关闭; S230,屏蔽信号gate_en打开,时钟信号输出OUT锁定为第一电平。其中,屏蔽信号 gate_en为高电平,通过反相器24、与逻辑门23使得延迟电路输入端IN恒定为低电平,时钟 6 CN 111726108 A 说 明 书 4/4 页 信号输出OUT锁定为低电平。此外,在本实施例中延迟电路的输出端还可以外接一反相器, 使得时钟信号输出OUT锁定为高电平。 延迟电路工作过程中,令被关断的奇数级四态门电路11输出逻辑高,被关断的偶 数级四态门电路11输出逻辑低。延迟电路的内部节点电压成为稳定的高低(1/0)电平交替 分布,此时无论控制信号切换到任意一级打开或关闭,延时线内部节点电压仍然为稳定的 高低电平交替分布,切换时不产生任何毛刺信号。 参考图4、图6、图9所示,另一个实施例中,本申请的时钟控制方法,包括: S310,控制第0至M-1级反相单元111打开、上拉单元112、下拉单元关闭113,第M级 反相单元111、上拉单元121关闭,第M级下拉单元113打开,此时第M级四态门电路11的输出 端被下拉为低电平,并保持为低电平; S320,控制第0至M-1级第一反相器121关闭、第二反相器122打开,第M级第一反相 器121打开、第二反相器122关闭; S330,屏蔽信号gate_en打开,时钟信号输出OUT锁定为第二电平。其中,屏蔽信号 gate_en为高电平,通过或逻辑门33使得延迟电路输入端IN恒定为低电平,时钟信号输出 OUT锁定为高电平。此外,在本实施例中延迟电路的输出端还可以外接一反相器,使得时钟 信号输出OUT锁定为低电平。 应当注意以上所描述的所有或者任一实施例可以彼此结合,除非另外声明或者此 类实施例可能在功能上和/或架构上相互排斥。 虽然本申请与引用的特定示例实施例一起被描述,但是本申请并不仅限于于此描 述的实施例,而是可以用在后附的权利要求的精神和范围内以修改或者变更的形式被实 施。相应的,说明书和附图应被视为说明的意思而非限制的意思。 由上所述,应当注意到本申请特定的实施例在这里以示例为目的被描述,但是在 不背离本申请范围的情况下可以做不同的修改。相应地,本申请除了后附的权利要求,并不 被限制。 本领域技术人员在实施本申请时可以通过对于附图、公开的内容和权利要求的研 究,了解并进行对于公开的实施例的其他改变。在权利要求中,词语“包括”并不排除其他组 件或步骤,并且不定冠词“一个”并不排除多个。即使特定的特征记载在不同的从属权利要 求中,本申请也涉及具有共同的这些特征的实施例。任何在权利要求中的附图标记不应当 被解释为限制范围。 不同实施例的特征和方面可以被整合到另外的实施例中,并且本文件所示的实施 例可以在没有所有示例或者描述的特征或者方面的情况下实施。本领域技术人员会注意 到,虽然本系统和方法的特定的示例和实施例为了示例目的而被描述,在不背离本申请的 精神和范围的情况下可以做出不同的修改。此外,一个实施例的特征可以被包含到另一个 实施例中,即使这些特征并未在本文件中在一个单一的实施例中被一起描述。相应地,本申 请被所附的权利要求描述。 7 CN 111726108 A 说 明 书 附 图 1/4 页 图1 图2 8 CN 111726108 A 说 明 书 附 图 2/4 页 图3 图4 9 CN 111726108 A 说 明 书 附 图 3/4 页 图5 图6 图7 10 CN 111726108 A 说 明 书 附 图 4/4 页 图8 图9 11