技术摘要:

本发明涉及一种用于测试ASIC的主要内部信号的电路,其中,设置仅一个测试引脚(TEST),通过所述测试引脚能够选择待考察的数字信号或模拟信号(D1,D2,...,Dn;A1,A2,...,An)。所述电路包括:布置在所述测试引脚(TSET)和所述电路的输出接头(TM)之间的施密特触发器(SM 全部

背景技术:

专用集成电路(英:application-specific integrated circuits,ASIC)在其制 造过程中以及在其交付之前都会接受测试。为此,必须能够提供能通过测试接口考察或测 量的内部数字信号和/或模拟信号。为此通常将ASIC置于测试模式,在该模式下,数字信号 和/或模拟信号能够通过多路复用器接通到ASIC的一个或多个单独的接头上。通常可以例 如通过串行外围接口(SPI)或借助符合IEEE标准1149.1的接口(也称为Joint Test Action Group,JTAG,联合测试行动小组)来选择依次待测试的信号。到目前为止,这需要ASIC基础 结构的重要部分处于运行中,例如内部电压供给、电压参考、通信接口、ASIC的数字部分或 至少ASIC的数字部分的一些区域以及模拟部分的一些部分。 由此可能限制ASIC的可测试性,尤其是主要内部测试变量,例如主要电压供给、主 要电压参考、主要电压供给的复位信号。 如果应能够通过测试接口将ASIC的主要内部信号引至外部,则需要谨慎的、有时 高开销的设计,以便确保不会由于相应的信号的可测试性而危害ASIC的正常运行,尤其是 其起动。如果例如应能够测试内部电压供给的复位信号,则有时必须在测试运行中抑制或 屏蔽该复位信号的影响。然而,在正常运行中进行抑制会损害ASIC的正常功能。因此必须确 保在正常运行中不损害这种信号。 此外,如果应将内部模拟电压(例如主要内部电压参考)通过分散式的模拟多路复 用器引至外部,则需确保在正常运行中不会损害这些信号。分布式的多路复用器的在起动 时被错误操控的传输门例如可能使主要内部电压参考与另一待测试的信号短路并因此阻 止起动,即使该错误操控仅短暂地进行。 例如,如果在此内部主要电压出于测试目必须足够小,使得从内部主要电压供给 导出的电压供给不足以用于运行数字部分,则在某些情况下,可能不能够通过测试接口来 考察内部主电压供给的复位信号或上电复位信号(Power-on-Reset-Signal)。

技术实现要素:

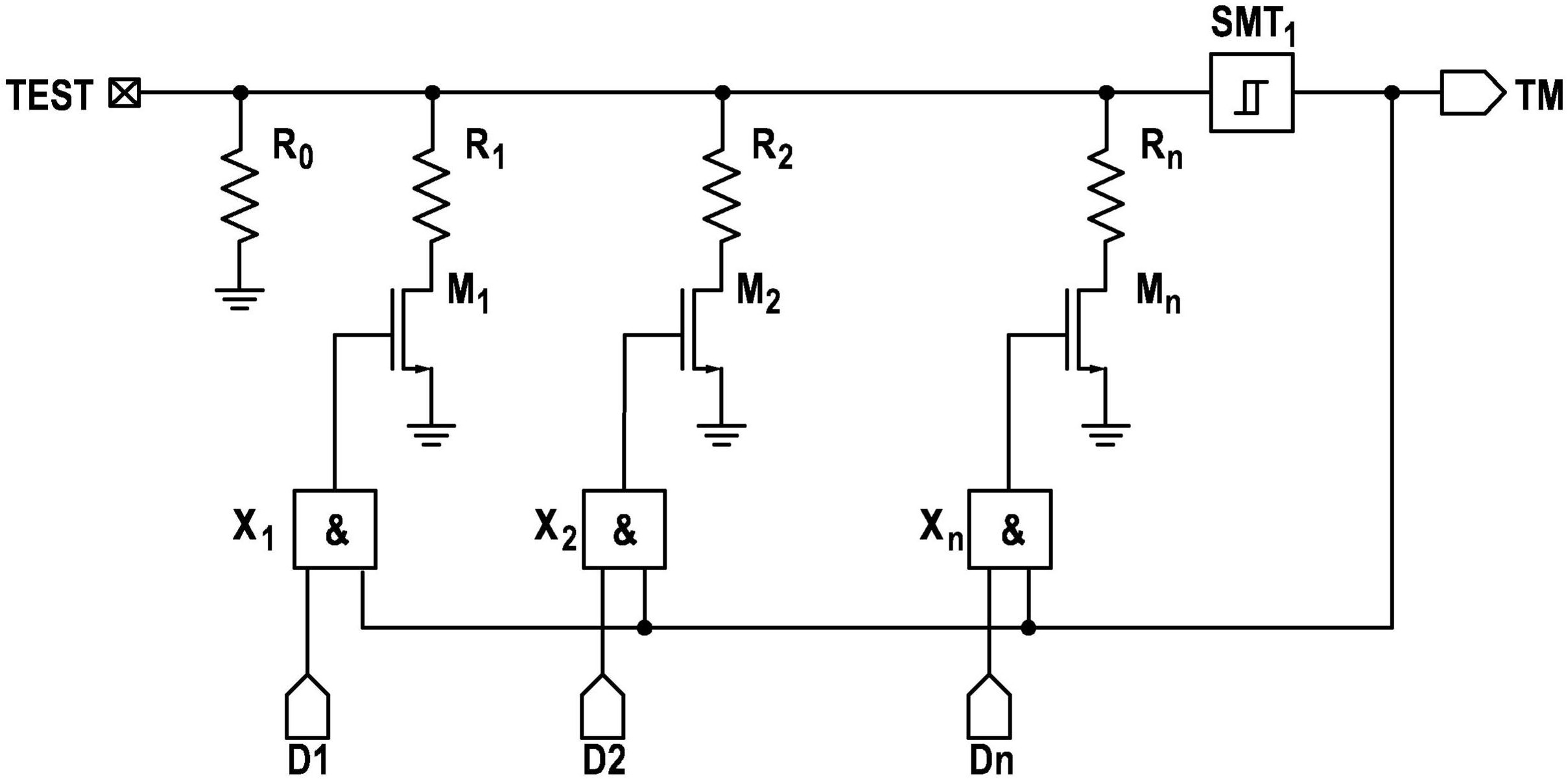

因此,根据本发明,提供一种用于测试ASIC的主要内部信号的电路,其中,设置仅 一个测试引脚,通过该测试引脚能够执行选择一个或多个待考察的数字信号或选择模拟信 号。 通过以这种方式实现的在测量技术上检测流入测试引脚接头的电流,可以推断出 一个或多个待考察的信号的状态。这种电路特别适合于测试前面提及的主要测试变量,例 如ASIC的主要电压供给、主要电压参考和主要电压供给的复位信号。 4 CN 111615635 A 说 明 书 2/8 页 根据本发明,在此设置布置在测试引脚和电路的输出接头之间的施密特触发器, 其中,在超过施密特触发器的切换阈值时激活测试模式。此外,根据本发明的电路包括用于 考察数字信号的至少一个子电路,所述至少一个子电路具有电阻、NMOS晶体管和与门,在与 门的第一输入端上存在所述数字信号。在此,电阻布置在测试引脚和NMOS晶体管的漏极接 头之间,NMOS晶体管的源极接头接地,NMOS晶体管的栅极接头和与门的输出端连接,与门的 第二输入端与所述电路的输出端接头连接。 本发明的优点 取决于相应的实现形式,所提出的电路原则上适合用于测试任何内部数字信号, 并且按照优选地实施方式也适合用于测试ASIC的任何内部模拟信号。 所述电路特别有利的是,ASIC基础设施只需在以下范围内是运行准备就绪的:在 测试数字信号或模拟信号期间仅内部电压可供使用。除了该电压供给和按照实施例提出的 电路之外,不需要ASIC的其他电路运行准备就绪。 ASIC的数字部分尤其不必是功能准备就绪的,而是可以处于复位状态。由ASIC的 数字部分操作的通信接口同样是不需要的。 与从现有技术中已知的解决方案相比,根据本发明进行用于可能切换到专门的测 试模式中的通信、用于选择待考察的数字信号或模拟信号之一的通信以及通过ASIC的唯一 接头对这些信号进行测量技术上的检测。 由此能够实现:主要测试变量(或任何其他数字信号或模拟信号)一定程度上在正 常功能中、即在正常运行中被测试或考察。因此例如不需要屏蔽复位信号。相应地可以简化 ASIC的用于描述实际功能的设计。 根据本发明,可以将测试引脚理解为双向接口,因为通过该测试引脚,可以通过以 合适的时间顺序施加不同高度的电压将信息(尤其是应准确地在测量技术上检测什么或应 该激活哪个测试模式)传输到ASIC中。此外,测试引脚还可以以流入引脚中的电流的形式提 供关于内部信号的信息。 在此,每个内部数字信号相应于公式I 0 1TEST=UTEST/R×[1/2 1/(D1×2 ) 1/(D2× 22) … 1/(Dn×2n)]加权地改变电流。如果所有数字信号均为“低”,则仅电流ITEST=UTEST/R ×1/20流入测试引脚。例如如果内部数字信号D1=“高”,则附加地有电流ITEST=UTEST/R×1/ 21流入测试引脚。在内部数字信号D2=“高”时,以模拟方式附加地有电流ITEST=UTEST/R×1/ 22流入测试引脚。电流是经过加权的并且相互重叠。以这种方式可以通过对电流进行测量 技术上的检测来同时或者说并行地推断所有内部数字信号的状态。因此,电流的加权对于 同时或并行检测内部数字信号是重要的,从而应重视为电路功能所使用的电阻的相应加 权。 如果选择模拟信号A1、A2…Am之一取代所有内部数字信号D1、D2…Dn,则可以推断出 测试引脚的内部电压值,其方式是测量流入测试引脚的电流。该电流的结果是ITEST=UTEST/R UA/R,其中,UA是所选择的内部模拟信号A1、A2…Am的电压值。 选择“在测试引脚上可以在测量技术上检测什么”,即,同时通过加权的电流检测 所有数字信号D1、D2…Dn还是通过与信号的电压成比例的电流检测模拟信号A1、A2…Am之一, 以及选择“测试模式”,均通过协议进行,该协议也通过ASIC的测试引脚传输至ASIC中。如此 实现这一点:根据测试引脚上的不同高度的电压电平借助分压器和借助施密特触发器和比 5 CN 111615635 A 说 明 书 3/8 页 较器探测并且由逻辑电路分析评价关于“应该在测量技术上检测什么”或“应激活哪个测试 模式”的信息。 在一种专门的实施方式中,根据本发明设置,电路还包括布置在测试引脚和地电 位之间的电阻,可以求取该电阻的值,其方式是,只要测试引脚上的电压低于施密特触发器 的切换阈值,就测量流入测试引脚的电流。通过知道该值并且测量流入测试引脚的电流,随 后能够实现推断出内部的数字信号和模拟信号的状态。 根据另一实施方式,所述电路还构造用于考察模拟信号并且包括运算放大器、具 有施密特触发器并用于限制测试引脚上的输入电压的电路以及设置为用于考察模拟信号 的至少一个子电路。以这种方式能够附加地实现测试用于本发明电路的模拟信号,以便测 试ASIC。 在此,根据一种优选的构型,设置为用于考察模拟信号的子电路包括具有两个D触 发器的计数器并且针对每个待考察的模拟信号包括一个具有与门的解码器以及包括一个 传输门。由此能够实现,根据D触发器的计数器状态(00、01、10或11)而定,使与门之一在其 输出端上具有“高”电平,因而驱控相应的传输门的“EN”输入端,使得传输门在它的另外两 个接头之间建立低电阻连接。优选的方式,计数器也可以由多于两个D触发器构成。相应地 可以考察m=2d-1个模拟信号A1、A2…Am,其中,d是D触发器的数量。设置呈一般性地已知的 构造方式的经典“1/m(1-aus-m)解码器”作为解码器,其在现有技术中也被称为“1/n(1- aus-n)”解码器,由2d个与门组成,每个与门分别具有d个输入端,其中,与门的输入端全部 与D触发器的反相输出端Q'连接,该与门同时设置为用于选择考察所有数字信号。 优选地,对应的与门的第一输入端与D触发器中的第一D触发器的非反相输出端或 反相输出端连接;对应的与门的第二输入端与D触发器中的第二D触发器的非反相输出端或 反相输出端连接;对应的与门的输出端与用于控制对应的传输门的输入端连接。由此实现, 所使用的D触发器可以占据计数状态00、01、10和11,使得以这种方式能够选择不同的内部 模拟信号用于考察。 根据该电路的一种优选构型,还设置有或门,该或门的第一输入端与至少两个D触 发器中的第一D触发器的非反相输出端连接,该或门的第二输入端与至少两个D触发器中的 第二D触发器的非反相输出端连接,该或门的输出端与用于控制运算放大器的输入端连接。 这种构型的优点在于,基于由D触发器输出的信号可以进行运算放大器的控制,并且以这种 方式使流入电路的测试引脚的电流受到对应选择的内部模拟信号的影响。 在另一有利构型中,还为根据本发明的电路设置与门,该与门的第一输入端与至 少两个D触发器中的第一D触发器的反相输出端连接,该与门第二输入端与至少两个D触发 器中的第二D触发器的反相输出端连接,该与门的输出端与至少一个与门各自的第三输入 端连接,所述至少一个与门布置在为考察数字信号所设置的子电路中。由此可以实现,可以 将用于考察数字信号的与门的输出端置于“低”,因此没有数字信号会影响到流入ASIC的测 试引脚中的电流。如此仅能够进行考察模拟信号。 在用于限制引脚处的输入电压的电路中,有利地将该电路的输入端布置在分压器 的两个电阻之间,该分压器布置在电路的测试引脚与地电位之间,所述电路的输出端与D触 发器的时钟信号输入端连接。 在本发明的一种有利构型中,电路的输出端接头借助反相器反相并且分别与D触 6 CN 111615635 A 说 明 书 4/8 页 发器的清零输入端(Clear-Eingang)连接。由此可以使D触发器的计数器状态再次复位,因 为借助反相器的“高”电平可以通过清零输入端使D触发器复位。 特别优选,电路还包括两个比较器,用于选择通过测试引脚待测量的数字信号或 模拟信号以及用于激活不同的测试模式。这种构型特别有利,因为如此实现的电路能够实 现不同的测试模式或测试方法,并且还能够容易地扩展成用多个接头运行,通过这些接头 可以以相同的方式选择和考察信号。 有利地,在此在比较器的正输入端处分别存在参考电压,比较器的负输入端分别 与测试引脚连接。存在以下可能性:即使运行电压或参考电压不具有其目标值,也能禁用比 较器并且因此能测试内部数字信号和/或模拟信号,使得例如能够在测量技术上检测,从哪 个内部供给电压起内部参考电压达到其目标值或内部上电复位信号改变其状态。 优选地,在比较器的负输入端与电路的测试引脚之间分别设置由晶体管以及由电 阻和电容组成的电路。这样能够保护比较器输入端避免其输入端上的过高电压以及能够对 输入信号进行滤波和延迟。 根据另一优选构型,在电路中还设置D触发器,该D触发器的时钟信号输入端与施 密特触发器的输出端连接,该D触发器的非反相输出端分别与用于控制对应的比较器的输 入端连接。 替代地有利地设置,电路包括两个D触发器,两个D触发器设置为用于提供输出信 号。输出这样的输出信号是有利的,因为这样的输出信号可以在ASIC中使用以便实现特定 的测试条件。 替代地,可以设置由D触发器组成的移位寄存器,用于选择待测试的信号以及用于 设定测试模式。 本发明的有利扩展方案在从属权利要求中说明,并在说明书中进行描述。 附图说明 参照附图和随后的说明书详细阐述本发明的实施例。附图中示出: 图1:用于测试数字信号的电路的一种实施例; 图2:用于测试数字信号和模拟信号的电路的一种实施例; 图3:用于测试数字信号和模拟信号的电路的一种实施例,该电路具有激活不同测 试模式的可能性; 图4:用于测试数字信号和模拟信号的电路的以上提及的实施例的信号变化过程, 该电路具有根据图3的激活不同测试模式的可能性。