技术摘要:

本发明的目的在于提供一种能够抑制阈值电压降低的半导体装置及其制造方法。一种半导体装置,其设有极性相同的第一MOS晶体管(HVNMOS)和第二MOS晶体管(LVNMOS),第一MOS晶体管包括多晶硅的栅极电极,第一MOS晶体管的栅极电极具有以使从栅极宽度W的端部通过的层叠方向的延 全部

背景技术:

在集成电路中已有使用MOS构造的半导体,MOS晶体管中,在形成源漏电极的工序 中例如掺入N型杂质,N型杂质也被注入栅极的多晶硅。 MOS型晶体管中,在与连接源极及漏极的直线垂直的方向上定义栅极宽度,但是发 现了在栅极宽度上的端部电场局部升高、阈值电压降低的扭折(kink)现象(驼峰现象)。 为了改善扭折现象,例如提出了向栅极中的靠近栅极宽度上的端部的位置掺入极 性与栅极的其他区域相反的杂质的技术(例如专利文献1:美国专利第5998848号说明书) 等。 另一方面,为了提高MOS晶体管的特性,提出了向栅极的多晶硅注入N型杂质的技 术(专利文献2:美国专利申请公开第2009/0096031号说明书)。在专利文献2中,对通过蚀刻 形成电极之前的栅极注入N型杂质。 在如专利文献2那样对栅极注入N型杂质、如专利文献1那样形成极性相反的区域的情 况下,在栅极形成N型区域和P型区域(靠近栅极宽度的端部)。但是,存在N型杂质向P型区域 扩散的情况。扩散例如发生在退火工序中。在像这样发生扩散的情况下,存在所形成的P型 区域不足够大的可能性。如果P型区域变狭小,则存在发生阈值电压降低的情况。

技术实现要素:

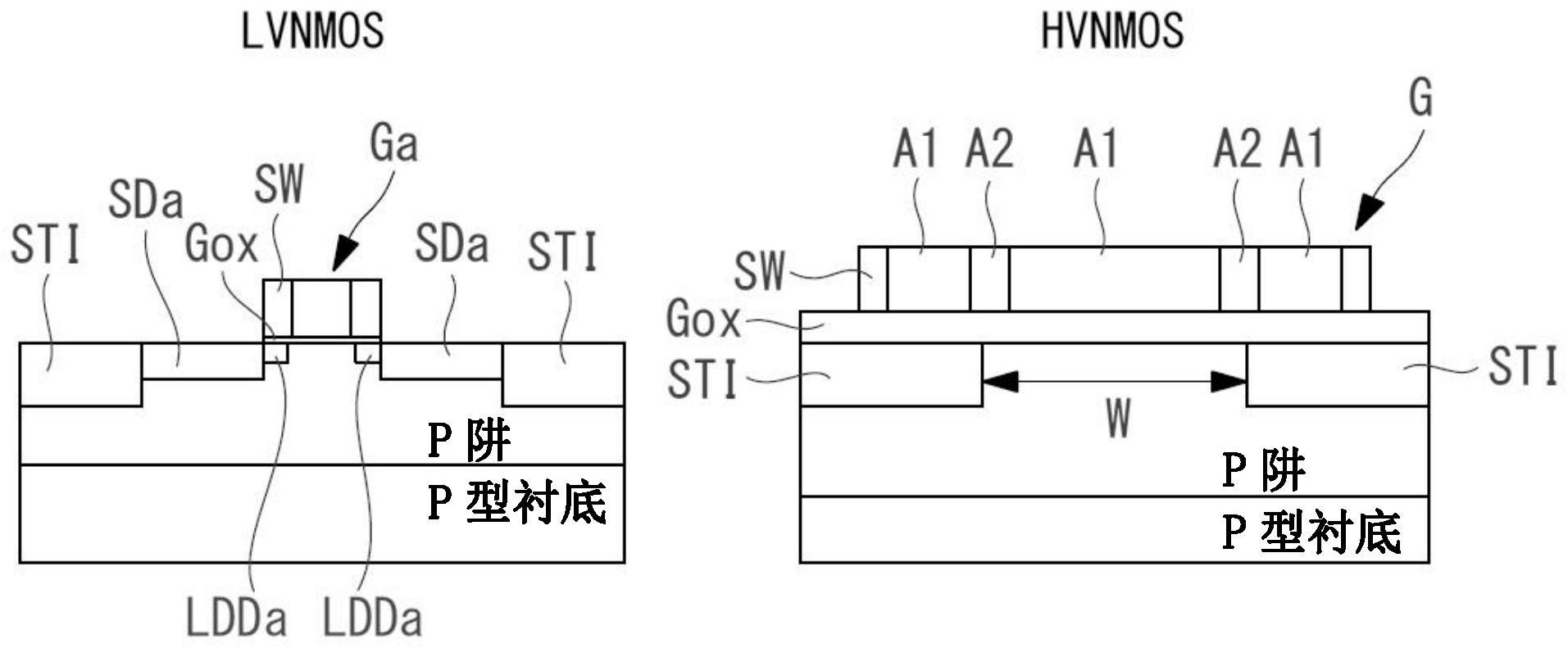

本发明是鉴于上述情况而完成的,其目的在于提供一种能够抑制阈值电压降低的 半导体装置及其制造方法。 本发明的一方式提供一种半导体装置,其是混合设置有极性相同的第一MOS晶体 管和第二MOS晶体管的半导体装置,所述第一MOS晶体管包括多晶硅的栅极电极、以及源漏 电极,所述第一MOS晶体管的栅极电极具有第一区域和所述第一区域以外的第二区域,所述 第二区域的极性与所述源漏电极的极性相同,所述第一区域的极性不同于所述第二区域的 极性,所述第二MOS晶体管包括被掺入极性与源漏电极相同的杂质的多晶硅的栅极电极,所 述第二区域的杂质的浓度比所述第二MOS晶体管的栅极电极的杂质的浓度低。所述第一区 域设置于栅极电极宽度的端部通过的层叠方向的延长线上,且与所述栅极电极宽度的各端 部对应地设置。 根据如上所述的结构,半导体装置混合设置有极性相同的第一MOS晶体管和第二 MOS晶体管,第一MOS晶体管的栅极电极具有第一区域和第一区域以外的第二区域,第二MOS 晶体管包括极性相同的多晶硅的栅极电极与源漏电极。而且,所述第二MOS晶体管的栅极电 极的杂质浓度高于所述第二区域的杂质浓度。因此,能够抑制第一区域因第二区域的杂质 的扩散而变得狭小。因此,能够抑制第一MOS晶体管的阈值电压降低。所述第一区域是设置 于栅极宽度的端部通过的层叠方向的延长线上,且与所述栅极宽度的各端部对应地设置。 4 CN 111599808 A 说 明 书 2/13 页 在上述半导体装置中,也可以是,所述第一MOS晶体管是高电压MOS构造,所述第二 MOS晶体管是低电压MOS构造。 根据如上所述的结构,即使在混合设置高电压MOS构造的第一MOS晶体管和低电压 MOS构造的第二MOS晶体管的情况下,也能够抑制第一MOS晶体管的阈值电压降低。 在上述半导体装置中,也可以是,所述第一MOS晶体管及所述第二MOS晶体管是N型 MOS构造。 根据如上所述的结构,能够抑制N型MOS构造的第一MOS晶体管的阈值电压降低。 在上述半导体装置中,也可以是,所述第二MOS晶体管中,在栅极蚀刻工序前向栅 极电极的多晶硅预掺入极性与源漏电极相同的杂质,所述第一MOS晶体管中,在栅极蚀刻工 序前向栅极电极的多晶硅预掺入极性不同于所述源漏电极杂质。 根据如上所述的结构,第二MOS晶体管中,在栅极蚀刻工序前向栅极电极的多晶硅 预掺入极性与源漏电极相同的杂质,另一方面,第一MOS晶体管中,在栅极蚀刻工序前向栅 极电极的多晶硅预掺入极性不同于所述源漏电极杂质,因此能够有效地使第二区域的杂质 的浓度比第二MOS晶体管的栅极电极的杂质的浓度低,从而抑制阈值电压降低。 在上述半导体装置中,也可以是,所述第一MOS晶体管并非由P型MOS构造的栅极电 极和N型MOS构造的栅极电极耦合构造而成。 根据如上所述的结构,能够以非耦合构造的MOS晶体管为对象。 本发明的另一方式提供一种半导体装置,其是设置有MOS晶体管的半导体装置,所 述MOS晶体管包括多晶硅的栅极电极,所述MOS晶体管的栅极电极具有第一区域和所述第一 区域以外的第二区域,所述第二区域的极性与所述源漏电极的极性相同,所述第一区域的 杂质机极性不同于所述第二区域的杂质极性,所述第一区域是设置于栅极宽度的端部通过 的层叠方向的延长线上,且与所述栅极宽度的各端部对应地设置。与通过下述方式制造出 的半导体装置的栅极电极相比,所述MOS晶体管的栅极电极中所述第二区域向所述第一区 域的杂质的扩散量较少:该半导体装置是在栅极蚀刻工序前进行的、向栅极电极的多晶硅 掺入极性与源漏电极相同的杂质的预掺杂工序中将与所述第一区域对应的第一注入区域 遮蔽,在栅极蚀刻工序之后进行的、掺入极性与通过所述预掺杂工序掺入的杂质相反的杂 质的逆极性注入工序中将与所述第二区域对应且与所述第一注入区域相接的第二注入区 域遮蔽而制造出。 根据如上所述的结构,与参考例相比,MOS晶体管的栅极电极中,能够使第二区域 向第一区域的杂质的扩散量较少,因此能够抑制第一区域的狭小化,从而有效地抑制阈值 电压降低。此外,参考例是指通过如下方式制造出的半导体装置的栅极电极:在栅极蚀刻工 序前进行的、向栅极电极的多晶硅掺入极性与源漏电极相同的杂质的预掺杂工序中将与第 一区域对应的第一注入区域遮蔽,在栅极蚀刻工序之后进行的、掺入极性与通过预掺杂工 序掺入的杂质相反的杂质的逆极性注入工序中将与第二区域对应且与第一注入区域相接 的第二注入区域遮蔽。 在上述半导体装置中,所述MOS晶体管也可以是N型高电压MOS构造。 根据如上所述的结构,能够抑制N型高电压MOS构造的晶体管的阈值电压降低。 在上述半导体装置中,也可以是,MOS晶体管中,预掺杂工序中的将栅极电极遮蔽 的范围设定得比与第一区域对应的第一注入区域大。 5 CN 111599808 A 说 明 书 3/13 页 根据如上所述的结构,预掺杂工序中的将栅极电极遮蔽的范围设定得比与第一区 域对应的第一注入区域大,因此能够更有效地减少第二区域向第一区域的杂质的扩散量, 从而抑制阈值电压降低。 在上述半导体装置中,也可以是,所述MOS晶体管中,在向源漏电极区域掺入杂质 的源漏电极形成工序前,在与所述第一区域对应的所述第一注入区域内掺入杂质,以及所 述第二区域对应的所述第二注入区域内掺入的杂质之间,隔开一预设间隔。 根据如上所述的结构,在源漏电极形成工序前,在第一注入区域内掺入的杂质,以 及第二注入区域内掺入的杂质之间隔开一预设间隔,因此能够使第二区域向第一区域的杂 质的扩散量减少,从而抑制阈值电压降低。 本发明提供的一种半导体装置的制造方法,还包括:制备第一MOS晶体管,所述第 一MOS晶体管包括多晶硅的栅极电极、以及源漏电极;所述第一MOS晶体管的栅极电极包括 第一区域以及所述第一区域以外的第二区域,所述第一区域设置于栅极电极宽度的端部通 过层叠方向的延长线上,所述第一区域与所述栅极电极宽度的各端部对应设置,所述第二 区域的极性与所述源漏电极的极性相同,所述第一区域的极性不同于所述第二区域的极 性;所述第一MOS晶体管中,在栅极蚀刻工序前向栅极电极的多晶硅预掺入极性不同于所述 源漏电极杂质; 制备与所述第一MOS晶体管极性相同的第二MOS晶体管,所述第二MOS晶体管包括极性 相同的多晶硅的栅极电极与源漏电极,所述第二MOS晶体管的栅极电极的杂质浓度高于所 述第二区域的杂质浓度;所述第二MOS晶体管中,在栅极蚀刻工序前向栅极电极的多晶硅预 掺入极性与所述源漏电极相同的杂质。 本发明的又一方式提供一种半导体装置的制造方法,包括:在硅衬底的表面形成多晶 硅层及源漏电极;在所述多晶硅层中设有第一注入区域及所述第一注入区域以外的第二注 入区域;在比第一注入区域大的范围被遮蔽的状态下,对所述多晶硅层掺入极性与源漏电 极相同的第一杂质;对所述多晶硅层进行蚀刻形成栅极电极;在第二注入区域被遮蔽的状 态下,向所述第一注入区域掺入与所述第一杂质极性相反的第二杂质;所述第一注入区域 形成第一区域,所述第二注入区域形成第二区域;所述第一区域设置于栅极电极宽度的端 部通过层叠方向的延长线上,所述第一区域与所述栅极电极宽度的各端部对应设置,所述 第二区域的极性与所述源漏电极的极性相同,所述第一区域的极性不同于所述第二区域的 极性。 在预掺杂工序中,在第一注入区域大的范围被遮蔽的状态下,对多晶硅掺入极性 与源漏电极相同的杂质,在逆极性注入工序中,针对蚀刻后得到的栅极电极,在将作为第一 注入区域以外的区域的第二注入区域遮蔽的状态下,向第一注入区域掺入极性与通过预掺 杂工序掺入的杂质相反的杂质。因此,在第一注入区域内掺入的杂质和第二注入区域内掺 入的杂质之间隔开预设间隔,因此能够抑制第一区域的狭小化,从而抑制阈值电压降低抑 制。 在上述半导体装置的制造方法中,也可以是,还包括在将第一注入区域遮蔽的状 态下对第二注入区域掺入极性与源漏电极相同的杂质的源漏电极形成工序。 根据如上所述的结构,在源漏电极形成工序中,能够阻止杂质向第一注入区域掺 入。 6 CN 111599808 A 说 明 书 4/13 页 在上述半导体装置的制造方法中,也可以是,还包括在源漏电极形成工序之后进 行的、对硅衬底进行退火工序。 根据如上所述的结构,能够通过对掺入杂质的硅衬底进行退火而使其活化。 发明效果 根据本发明,起到能够抑制阈值电压降低的效果。 附图说明 图1是本发明的第一实施方式涉及的半导体装置的俯视图的一个例子。 图2是本发明的第一实施方式涉及的半导体装置的X-X′截面图的一个例子。 图3是本发明的第一实施方式涉及的半导体装置的Y-Y′截面图的一个例子。 图4是本发明的第一实施方式涉及的LVNMOS的俯视图的一个例子。 图5是本发明的第一实施方式涉及的LVNMOS的Z-Z′截面图的一个例子。 图6是表示本发明的第一实施方式涉及的半导体装置的制造方法的第一工序的图的一 个例子。 图7是表示本发明的第一实施方式涉及的半导体装置的制造方法的第二工序的图的一 个例子。 图8是表示本发明的第一实施方式涉及的半导体装置的制造方法的第三工序的图的一 个例子。 图9是表示本发明的第一实施方式涉及的半导体装置的制造方法的第四工序的图的一 个例子。 图10是表示本发明的第一实施方式涉及的半导体装置的制造方法的第五工序的图的 一个例子。 图11是表示本发明的第一实施方式涉及的半导体装置的制造方法的第六工序的图的 一个例子。 图12是表示本发明的第一实施方式涉及的半导体装置的制造方法的第七工序的图的 一个例子。 图13是表示本发明的第一实施方式涉及的半导体装置的制造方法的第八工序的图的 一个例子。 图14是说明本发明的第一实施方式涉及的半导体装置的效果的图的一个例子。 图15是本发明的第二实施方式涉及的半导体装置的俯视图的一个例子。 图16是本发明的第二实施方式涉及的半导体装置的X-X′截面图的一个例子。 图17是本发明的第二实施方式涉及的半导体装置的Y-Y′截面图的一个例子。 图18是表示本发明的第二实施方式涉及的半导体装置的制造方法的第一工序的图的 一个例子。 图19是表示本发明的第二实施方式涉及的半导体装置的制造方法的第二工序的图的 一个例子。 图20是表示本发明的第二实施方式涉及的半导体装置的制造方法的第三工序的图的 一个例子。 图21是表示本发明的第二实施方式涉及的半导体装置的制造方法的第四工序的图的 7 CN 111599808 A 说 明 书 5/13 页 一个例子。 图22是表示本发明的第二实施方式涉及的半导体装置的制造方法的第五工序的图的 一个例子。 图23是表示本发明的第二实施方式涉及的半导体装置的制造方法的第六工序的图的 一个例子。 图24是表示本发明的第二实施方式涉及的半导体装置的制造方法的第七工序的图的 一个例子。 图25是表示本发明的第二实施方式涉及的半导体装置的制造方法的第八工序的图的 一个例子。 图26是表示参考例的制造方法的第三工序的图的一个例子。 图27是表示参考例涉及的半导体装置的栅极中的杂质分布状态的图的一个例子。 图28是表示本发明的第二实施方式涉及的半导体装置的栅极中的杂质分布状态的图 的一个例子。 附图标记说明 1a 半导体装置 1b 半导体装置 A1 第一区域 A2 第二区域 AI1 第一注入区域 AI2 第二注入区域 G 栅极电极 Ga 栅极电极 Gox 硅氧化膜 L 栅极长度 L1 抗蚀图案 L2 抗蚀图案 L3 抗蚀图案 L4 抗蚀图案 L6 抗蚀图案 S 隔离区域 SD 源漏电极 SDa 源漏电极 SW 侧壁 W 栅极宽度