技术摘要:

本申请提供一种刻蚀方法,包括:预刻蚀步骤,向刻蚀腔室内通入第一工艺气体,并开启电源,对多晶硅栅极顶部表面进行刻蚀;上射频电源和下射频电源皆输出连续波;掺杂刻蚀步骤,通入第二工艺气体,对多晶硅栅极进行刻蚀;上射频电源输出连续波,下射频电源输出脉冲波; 全部

背景技术:

MOS(Metal Oxide Semiconductor,金属-氧化物-半导体)集成电路因其具有低功 耗、大噪声容限、易于设计等优点,而被广泛应用于消费电子、移动互联网、智能通信、汽车 电子、工业控制、医疗电子等领域。随着电路集成度的不断提高,对半导体器件的加工线宽 要求也越来越小。例如,由于多晶硅栅极的形貌(Profile)及关键尺寸CD(Critical Dimension)对MOS器件的驱动电流、等效电阻等器件性能有较大影响,所以多晶硅栅极的刻 蚀精度则对MOS器件的稳定性具有较大影响。 双掺杂(N型掺杂和P型掺杂)多晶硅栅极是指顶部被掺入N型或P型的原子或元素 的多晶硅栅极。在等离子体刻蚀过程中,由于两种掺杂的多晶硅栅极对反应腔室中的离子 或电子的洛伦兹力不同,会使反应物或生成物在栅极表面的反应或吸附程度不同,从而造 成N、P两种掺杂的多晶硅栅极形貌不同,最终导致CD不同。随着半导体制造工艺向下节点推 进,器件的关键尺寸缩小,图形化刻蚀过程中的微观负载效应(图形密集度不同则刻蚀速率 不同,导致多晶硅栅极不同位置的刻蚀尺寸不一致)欲见明显。 现有技术中,针对这种微观负载效应的改善方案大多是通过光刻工艺补偿来改 善,但这些方式只能在一定程度上缩小这种微负载效应的影响,且缩小影响后获得的CD尺 寸仍无法满足器件的电性能要求。

技术实现要素:

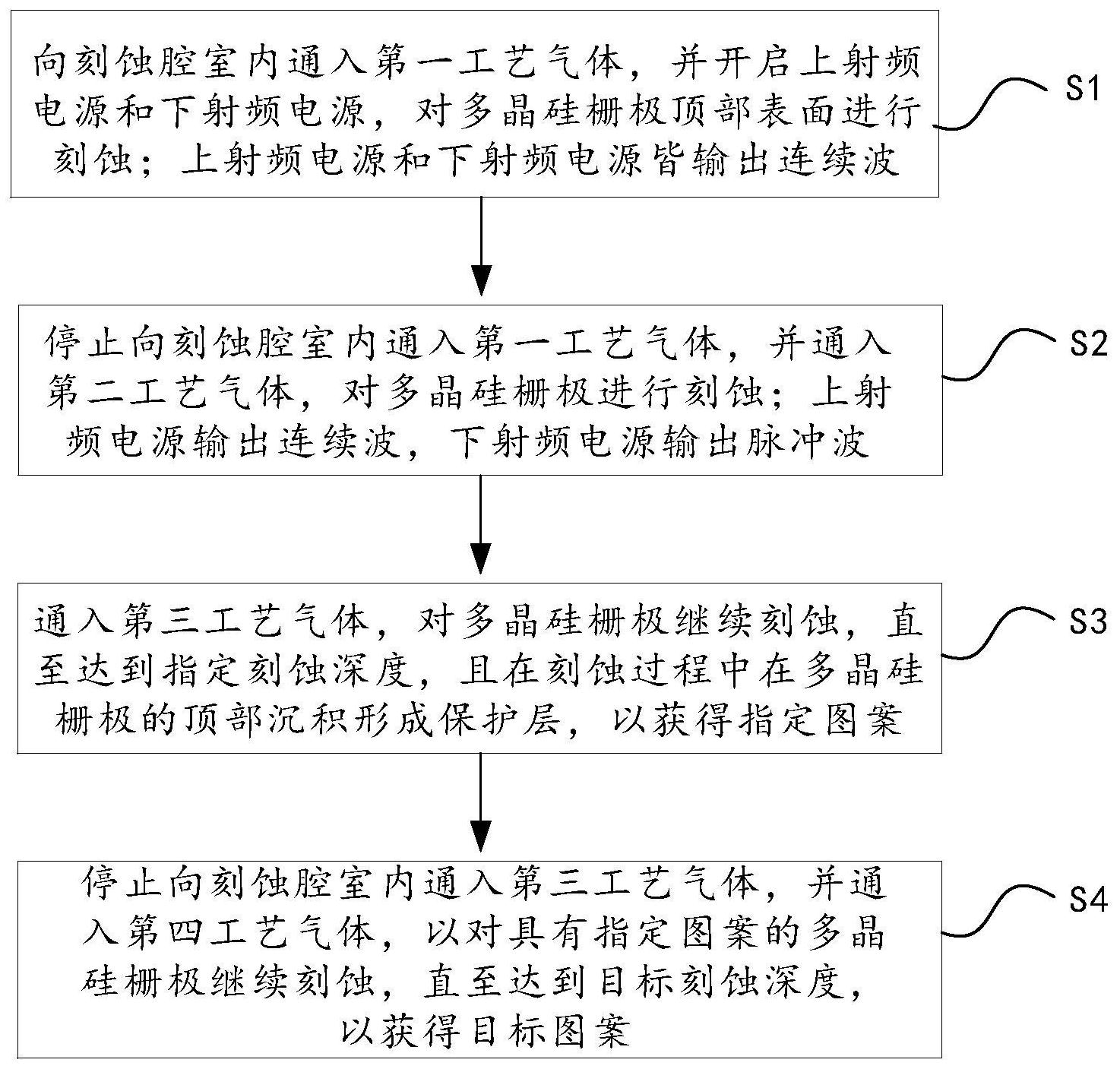

本发明旨在至少解决现有技术中存在的技术问题之一,提出了一种的刻蚀方法, 其可在现有技术之上大幅度缩小甚至消除微观负载效应。 为实现本发明的目的而提供一种刻蚀方法,包括: 预刻蚀步骤,向刻蚀腔室内通入第一工艺气体,并开启上射频电源和下射频电源, 对多晶硅栅极顶部表面进行刻蚀;所述上射频电源和所述下射频电源皆输出连续波; 掺杂刻蚀步骤,停止向所述刻蚀腔室内通入所述第一工艺气体,并通入第二工艺 气体,对所述多晶硅栅极进行刻蚀;所述上射频电源输出连续波,所述下射频电源输出脉冲 波; 主刻蚀步骤,通入第三工艺气体,对所述多晶硅栅极继续刻蚀,直至达到指定刻蚀 深度,且在刻蚀过程中在所述多晶硅栅极的顶部沉积形成保护层,以获得指定图案; 过刻蚀步骤,停止向所述刻蚀腔室内通入所述第三工艺气体,并通入第四工艺气 体,以对具有所述指定图案的多晶硅栅极继续刻蚀,直至达到目标刻蚀深度,以获得目标图 案。 可选地,所述第一工艺气体包括四氟甲烷。 可选地,所述掺杂刻蚀步骤中,所述下射频电源的占空比的取值范围为10%~ 3 CN 111739795 A 说 明 书 2/7 页 25%。 可选地,所述第二工艺气体包括六氟化硫和二氟甲烷。 可选地,所述掺杂刻蚀步骤中,自所述多晶硅栅极顶部向下刻蚀至所述多晶硅栅 极总厚度的三分之一位置处。 可选地,所述掺杂刻蚀步骤中,所述上射频电源的功率与所述下射频电源的功率 的比值的取值范围为0.8~1.2。 可选地,所述指定刻蚀深度为所述多晶硅栅总厚度的70%~80%。 可选地,所述第三工艺气体包括六氟化硫和二氟甲烷,其中,所述六氟化硫用作刻 蚀气体,所述二氟甲烷用作沉积气体。 可选地,所述主刻蚀步骤中,通过调节所述六氟化硫和所述二氟甲烷的比例来控 制所述多晶硅栅极侧壁的陡直程度。 可选地,所述第四工艺气体包括溴化氢和/或氧气。 本发明具有以下有益效果: 本发明提供的刻蚀方法,在进行主刻蚀步骤之前先进行掺杂刻蚀步骤,且掺杂刻 蚀步骤中下射频电源输出脉冲波,使得工艺气体被电离的等离子体形成脉冲等离子体,可 通过调节下射频电源输出脉冲波的频率和占空比,调节脉冲等离子体的运动及反应速度, 使得脉冲等离子体刻蚀多晶硅栅极顶部掺杂区域时,在N型掺杂部分和P型掺杂部分的刻蚀 速率的差异非常小,从而在去除多晶硅栅极顶部的N型掺杂部分和P型掺杂部分的同时,确 保刻蚀后N型多晶硅栅极与P型多晶硅栅极形貌的一致性,不具有“缩脖”或“内陷”效应,在 现有技术之上大幅度缩小甚至消除微观负载效应,将微观负载值调至1nm,为14nm(关键尺 寸)及以下节点制程中的微负载效应提供有效的解决方案。 附图说明 图1a为刻蚀后出现“缩脖”效应的N型多晶硅栅极的形貌示意图; 图1b为刻蚀后出现“缩脖”效应的P型多晶硅栅极的形貌示意图; 图2a为采用刻蚀气体与沉积气体混合的方式进行刻蚀后的N型多晶硅栅极的形貌 示意图; 图2b为采用刻蚀气体与沉积气体混合的方式进行刻蚀后的P型多晶硅栅极的形貌 示意图; 图3为本申请实施例提供的刻蚀方法的流程示意图; 图4a为采用本申请实施例提供的刻蚀方法刻蚀后的N型多晶硅栅极的形貌示意 图; 图4b为采用本申请实施例提供的刻蚀方法刻蚀后的P型多晶硅栅极的形貌示意 图。