技术摘要:

本发明涉及一种腔体谐振抑制结构及应用。所述腔体谐振抑制结构用于抑制三维异构集成射频结构的腔体谐振;所述三维异构集成射频结构包括内嵌有射频芯片的下层转接板、与所述下层转接板对位键合的上层转接板和设置在所述射频芯片上的片上传输线;所述上层转接板在与所述 全部

背景技术:

在毫米波相控阵应用中,半波长的天线阵元间距很小,射频通道间距小于5毫米, 传统单通道射频芯片难以在该尺度内完成布局。为解决上述矛盾,目前多采用多通道单片 集成射频芯片以减少通道间互连走线的空间占用,并采用三维集成方案实现通道芯片的垂 直堆叠以进一步减小空间占用。 随着硅基微机电(MEMS)和射频硅通孔(TSV)工艺技术的发展,三维异构集成(3D heterogeneous integration)技术成为毫米波相控阵射频通道实现小尺寸三维集成的重 要技术发展方向。该技术采用多层硅转接板为基板,在硅转接板上刻蚀空腔并内嵌射频芯 片实现通道集成。 现有毫米波相控阵射频通道多采用硅基4通道或16通道单片集成射频芯片,芯片 尺寸达到工作频率对应的半波长量级,应用时将该芯片内嵌于下层硅转接板空腔中,并在 上层硅转接板相同位置刻蚀空腔,与下层硅转接板进行对位键合。由于键合后两层硅转接 板外表面为金属地,构成金属谐振腔体,且腔体尺寸在半波长量级,当毫米波信号在内嵌射 频芯片上传输时,腔体谐振将在谐振频率点引入信号幅度和相位突变,显著恶化相控阵幅 相控制精度、带内幅度平坦度和带内相位线性度,无法满足毫米波相控阵应用需要。 综上所述,非常有必要提供一种腔体谐振抑制结构,用于支持毫米波相控阵三维 异构集成射频结构的腔体谐振抑制。

技术实现要素:

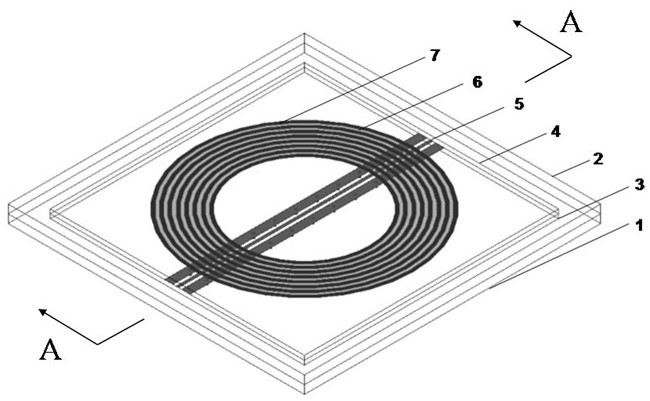

为了解决现有三维异构集成射频结构存在的不足,本发明提供了一种腔体谐振抑 制结构及应用,实现了硅转接板内嵌大尺寸多通道单片集成射频芯片结构(三维异构集成 射频结构)的腔体谐振抑制,显著改善了相控阵幅相控制精度、带内幅度平坦度和带内相位 线性度受腔体谐振的影响。 为了实现上述目的,本发明在第一方面提供了一种腔体谐振抑制结构,所述腔体 谐振抑制结构用于抑制三维异构集成射频结构的腔体谐振;所述三维异构集成射频结构包 括内嵌有射频芯片的下层转接板、与所述下层转接板对位键合的上层转接板和设置在所述 射频芯片上的片上传输线;所述上层转接板在与所述射频芯片相对应的位置设置有空气 腔;所述腔体谐振抑制结构包括依次设置在所述上层转接板的空气腔底部的电阻薄膜和谐 振环族。 优选地,所述谐振环族由多个间隔均匀排布的谐振环组成;所述谐振环的厚度小 于10μm,和/或所述谐振环的宽度为50~100μm。 优选地,每相邻两个所述谐振环的间距为50~100μm。 3 CN 111740204 A 说 明 书 2/6 页 优选地,所述电阻薄膜的厚度不大于0.5μm,和/或所述电阻薄膜的方阻为30~ 70Ohm。 优选地,所述谐振环族的周长变化范围覆盖需要抑制的腔体谐振频率对应的波 长;和/或所述谐振环的形状为圆环、椭圆环或多边形环。 优选地,所述电阻薄膜由镍镉合金、钛、氮化钽中的一种或多种制成;和/或所述谐 振环族由铜和/或金制成。 优选地,所述上层转接板和/或所述下层转接板的厚度为200~300μm;和/或所述下 层转接板中设置有用于内嵌所述射频芯片的空气腔,所述下层转接板的空气腔的深度与所 述射频芯片的厚度相同;和/或所述上层转接板的空气腔的深度为50~150μm。 优选地,所述腔体谐振抑制结构用于抑制三维异构集成射频结构的腔体谐振时, 使得100μm厚的射频芯片上的5μm厚的片上传输线在40GHz以下频段的反射系数小于-30dB, 传输系数大于-1dB。 本发明在第二方面提供了包含本发明在第一方面所述的腔体谐振抑制结构的三 维异构集成射频结构。 本发明在第三方面提供了本发明在第一方面所述的腔体谐振抑制结构或本发明 在第二方面所述的三维异构集成射频结构在毫米波相控阵中的应用。 本发明与现有技术相比至少具有如下有益效果: (1)本发明提出的由低Q谐振环族组成的腔体谐振抑制结构,是硅转接板内嵌大尺寸多 通道单片集成射频芯片结构实现高性能射频传输的关键,可支持毫米波相控阵三维异构集 成射频结构的腔体谐振抑制。 (2)与现有技术相比,本发明提出的由低Q谐振环族组成的腔体谐振抑制结构,采 用硅转接板空气腔底部沉积金属谐振环族覆盖腔体多模谐振频率,采用空气腔底部沉积电 阻薄膜降低金属谐振环族的Q值,实现了硅转接板大尺寸空气腔谐振抑制,以及空气腔内嵌 射频芯片的超宽带匹配和低插损传输。 (3)本发明的所述腔体谐振抑制结构用于抑制三维异构集成射频结构的腔体谐振 时,使得100μm厚的射频芯片上的5μm厚的片上传输线在40GHz以下频段的反射系数(S11)小 于-30dB,传输系数(S21)大于-1dB,并显著改善内嵌射频芯片幅相控制精度、带内幅度平坦 度和带内相位线性度受腔体谐振的影响,与无腔体谐振抑制结构的腔体内嵌射频芯片射频 特性相比,原幅度和相位抖动均已消除。 附图说明 本发明仅仅为说明目的提供,图中各部件的比例与数量不一定与实际产品一致。 图1是本发明的腔体谐振抑制结构应用在三维异构集成射频结构中的结构透视 图。 图2是图1的A-A的截面图。 图3是图2的B部分的放大图。 图4是无腔体谐振抑制结构的腔体内嵌射频芯片的S11与S21幅度仿真结果。 图5是无腔体谐振抑制结构的腔体内嵌射频芯片的S21相位仿真结果。 图6是含本发明腔体谐振抑制结构的腔体内嵌射频芯片的S11与S21幅度仿真结 4 CN 111740204 A 说 明 书 3/6 页 果。 图7是含本发明腔体谐振抑制结构的腔体内嵌射频芯片的S21相位仿真结果。 图1至图3中:1:下层转接板;2:上层转接板;3:射频芯片;4:空气腔;5:片上传输 线;6:电阻薄膜;7:谐振环族。