技术摘要:

本发明提供一种半导体封装及其制造方法,半导体封装包括多个第一管芯、横向密封第一管芯的绝缘包封体、设置在绝缘包封体的部分上并至少部分与第一管芯重叠的第二管芯、以及设置在绝缘包封体上并电性连接到第一管芯和第二管芯的重布线结构。第二管芯的第二有源面面向第 全部

背景技术:

近年来,电子装置对人类生活更为重要。为使电子装置设计实现轻薄短小,半导体 封装技术不断发展,试图开发体积更小、重量更轻、集成度更高、在市场更具竞争性的产品。 由于半导体封装技术受到集成电路发展的高度影响,因此,随着电子组件尺寸的变化,封装 技术的要求也变得越来越严苛。此外,半导体封装中的重布线层(redistribution layer, RDL)的导电特征的尺寸减小,但是当受到外力(例如接合、焊接、回焊等工艺)时,导电特征 对裂缝更为敏感。因此,如何在保持工艺简化和微型化的同时提供更加防止这种裂缝产生 的半导体封装已成为该领域研究人员的一大挑战。

技术实现要素:

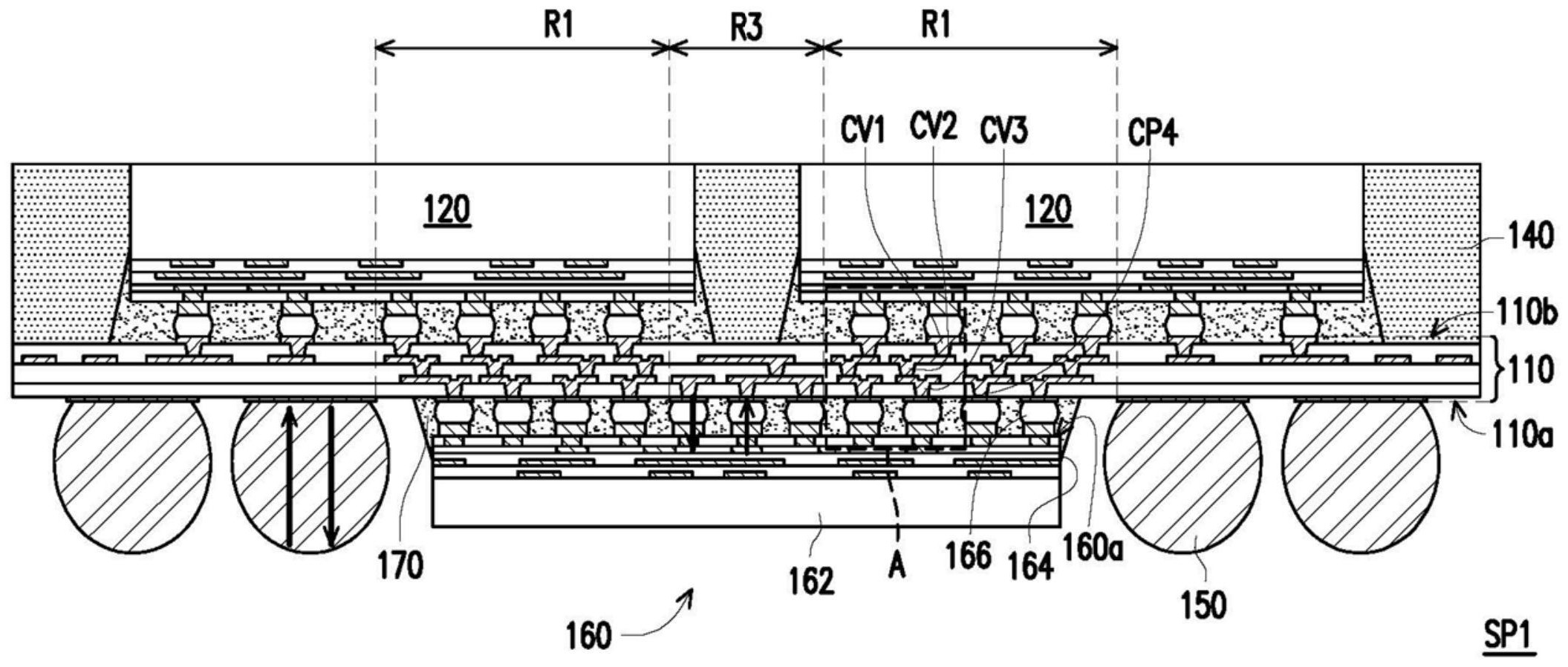

本发明提供一种半导体封装及其制造方法,其可提供电气性能的改善以及更高的 可制造性。 本发明的一种半导体封装包括并排设置的多个第一管芯、横向密封第一管芯的绝 缘包封体、设置在绝缘包封体的一部分上并至少部分地与第一管芯重叠的第二管芯、以及 设置在绝缘包封体上并电性连接到第一管芯和第二管芯的重布线结构。绝缘包封体的一部 分将第一管芯彼此分开。第二管芯的第二有源面面向第一管芯的第一有源面。重布线结构 包括设置在靠近第一管芯的重布线结构的第一层的第一导通孔,以及设置在靠近第二管芯 的重布线结构的第二层的第二导通孔。第二层堆叠在第一层上。第一导通孔和第二导通孔 电性耦合并设置在重布线结构的区域中,该区域插设在第二管芯的第二有源面和第一管芯 中的任一个的第一有源面之间,其中第一导通孔与第二导通孔错位成横向偏移。 在一些实施例中,半导体封装还包括底胶,其设置在重布线结构的第二层和第二 管芯的第二有源面之间。在一些实施例中,第一导通孔在第二管芯的第二有源面上的第一 正投影区域与第二导通孔在第二管芯的第二有源面上的第二正投影区域完全不重叠。在一 些实施例中,第一导通孔在第二管芯的第二有源面上的第一正投影区域至少部分地与第二 导通孔在第二管芯的第二有源面上的第二正投影区域重叠。在一些实施例中,第一管芯中 的一者通过第一管芯中的一者的第一接触特征的第一焊帽(solder cap)安装在第一导电 接垫上,第二管芯通过第二管芯的第二接触特征的第二焊帽安装在第二导电接垫上。在一 些实施例中,重布线结构和第一管芯之间的界面与重布线结构和绝缘包封体之间的界面基 本上齐平。 本发明的一种半导体封装的制造方法至少包括以下步骤。在重布线电路的第一表 面上设置多个第一管芯,其中重布线电路包括第一导通孔以及第二导通孔,第一导通孔形 成在靠近第一管芯的重布线电路的第一层,第二导通孔形成在堆叠于第一层上的重布线电 4 CN 111599795 A 说 明 书 2/12 页 路的第二层,第一导通孔的中心是从第二导通孔的中心横向偏移。在重布线电路上形成绝 缘包封体以密封第一管芯,其中绝缘包封体的一部分形成在相邻的第一管芯之间。在与第 一表面相对的重布线电路的第二表面上设置第二管芯,其中第二管芯覆盖绝缘包封体的部 分并通过重布线电路电性耦合到第一管芯。 在一些实施例中,半导体封装的制造方法还包括在设置第二管芯之前,在重布线 电路的第二表面的第二导通孔上形成多个导电接垫,其中在设置第二管芯之后,将第二管 芯的多个接触特征接合到导电接垫。在一些实施例中,半导体封装的制造方法还包括在设 置第二管芯后,在重布线电路的第二表面和第二管芯之间形成底胶。在一些实施例中,半导 体封装的制造方法还包括在设置第一管芯时,在第一管芯和重布线电路的第一表面之间的 第一界面上进行焊接工艺,以及在设置第二管芯时,在第二管芯和重布线电路的第二表面 之间的第二界面上执行焊接工艺。 本发明的一种半导体封装的制造方法至少包括以下步骤。用绝缘包封体密封多个 第一管芯,其中所述绝缘包封体的一部分形成在两个所述相邻的第一管芯之间。在所述第 一管芯和所述绝缘包封体上形成重布线电路,其中所述重布线电路包括第一导通孔及第二 导通孔,所述第二导通孔形成在所述重布线电路的第一层并连接到被所述绝缘包封体暴露 出来的所述第一管芯的任一者的接触特征,所述第二导通孔设置在堆叠于所述第一层的所 述重布线电路的第二层,所述第一导通孔的中心与所述第二导通孔的中心错开一偏移量。 在所述重布线电路的所述第二层上设置第二管芯以通过所述重布线电路电性耦合到所述 第一管芯。 在一些实施例中,用第一管芯密封第一管芯的步骤包括形成绝缘材料以覆盖第一 管芯,以及减薄绝缘材料以暴露出第一管芯中的一者的接触特征的至少一部分。在一些实 施例中,半导体封装的制造方法还包括在设置第二管芯后,在重布线电路的第二层和第二 管芯之间形成底胶。 基于上述,由于半导体封装包括以面对面(face-to-face)配置的方式所设置的第 一管芯和第二管芯,藉以缩短它们之间的互连距离,并可实现半导体封装的较低功耗和高 带宽。重布线结构的第一和第二导通孔以错位通孔(shifted-via)配置的方式设置,使得包 括这种错位通孔配置方式的半导体封装能够提供良好的可靠性并在工艺和操作期间可产 生较小的应力,从而消除裂缝和其他缺陷问题。 附图说明 为让本发明的上述特征和优点能更明显易懂,下文特举实施例,并配合附图作详 细说明如下。 图1A至图1F是依照本发明的一些实施例的半导体封装的制造方法的示意性剖视 图; 图2是依照本发明的一些实施例的图1F所绘的虚线框A的示意性放大图; 图3A是依照本发明的一些实施例的连接到第一管芯和第二管芯的重布线结构的 一部分的示意性剖视图; 图3B是依照本发明的一些实施例的图3A的虚线框B所绘的重布线结构的不同层中 的导通孔的示意性俯视图; 5 CN 111599795 A 说 明 书 3/12 页 图4A是依照本发明的一些实施例的连接到第一管芯和第二管芯的重布线结构的 一部分的示意性剖视图; 图4B是依照本发明的一些实施例的图4A的虚线框C中所绘的重布线结构的不同层 中的导通孔的示意性俯视图; 图5A至图5E是依照本发明的一些实施例的半导体封装的制造方法的示意性剖视 图。 [附图标号说明] 50、60:临时载体;51、61:剥离层;110、210、310、410:重布线结构;110a:第一表面; 110b:第二表面;112、412:图案化介电层;114、414:图案化导电层;120、420:第一管芯; 120a、160a、420a:有源面;120r、420r:背面;120w:侧壁;122、162:半导体基底;124、164:互 连结构;126、126A、126B、126C、126D、166、166A、166B、166C、166D、426:接触特征;126a:柱 体;126b:帽体;130、170:底胶;140、440:绝缘包封体;140t、426t、440t:顶面;150:导电端 子;160:第二管芯;440b:底面;A、B、C:虚线框;BP1、BP2:间距;C1:最上层的导电层;C2:中间 导电层;C3:最下层的导电层;CP1、CP2、CP3、P1a、P1b、P2a、P2b、P3a、P3b:导电接垫;CP4:第 一导电接垫;CP5:第二导电接垫;CT1、CT2、CT3、CT4:中心;CV1、CV2、CV3、V1a、V1b、V2a、V2b、 V2c、V3a、V3b、V3c:导通孔;D1:最上层的介电层;DN1:第一方向;DN2:第二方向;DN3:第三方 向;DN1’:方向;D2:中间介电层;D3:最下层的介电层;LD12、LD13、LD23:侧向距离;LD21、 LD31、LD32:偏移量;Lv1:最上层;Lv2:中间层;Lv3:最下层;R1:第一区;R2:第二区;R3:第三 区;R4:第四区;SP1、SP2:半导体封装;X31、X32:水平偏移量;Y31、Y32:垂直偏移量。