技术摘要:

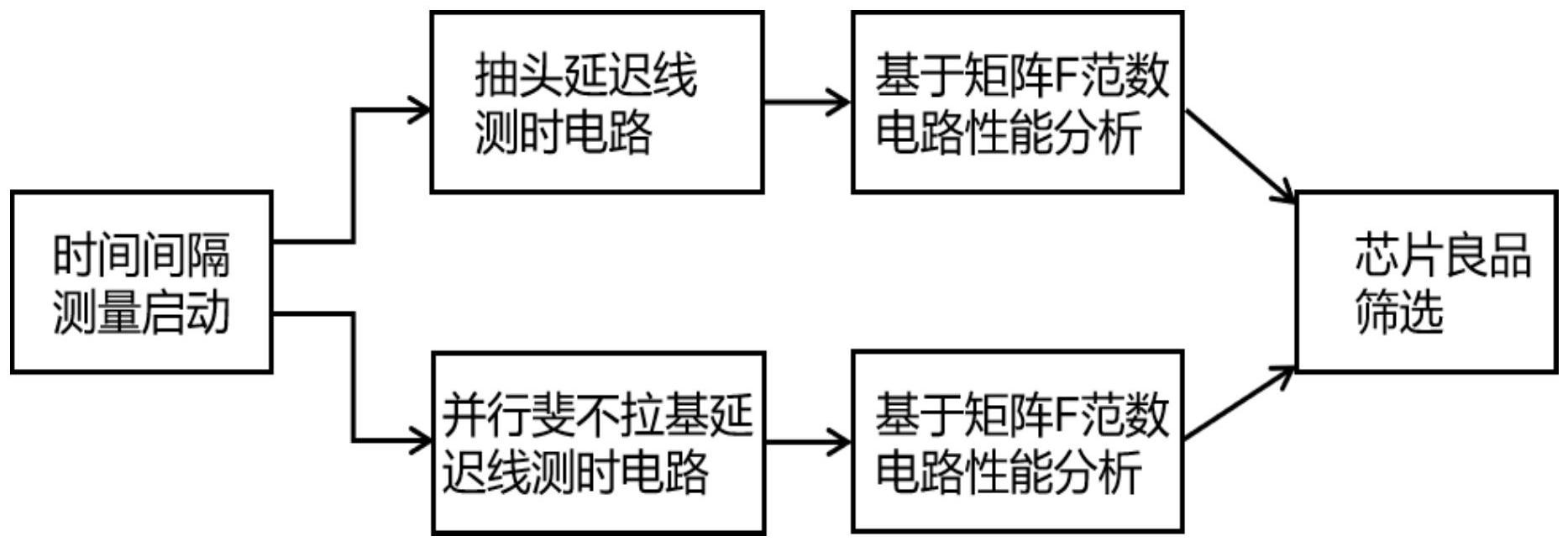

本发明公开一种双测时模式TDC芯片设计与制造,低功耗模式下,采用抽头延迟线测时电路完成测量,该电路的主体为延迟链,测时结构简单。高精度测量模式下,采用并行斐不拉基延迟线测时电路,该电路由四条延迟链并行构建,各延迟链包含四种不同延时单元,采用斐不拉基构建 全部

背景技术:

TDC(Time to digital converter)即时间数字转换电路。作为高精度时间测量电 路,该技术广泛用于激光测距、激光三维成像、天文实验、高能物理粒子实验、正电子发射断 层扫描(PET)成像等领域。TDC电路的分辨率、RMS精度、DNL/INL、功耗等性能指标直接影响 着这些应用的效能。 常规TDC电路的测量方案包括计数器直接计数测量、电流积分测量、时间放大测 量、游标测量、时间内插测量等等。TDC电路的性能指标也容易受温度、电压和工艺水平的影 响。针对多通道TDC电路,需设计有效方案降低功耗,总结说来,TDC根据实现方案,分为模拟 电路结构和数字电路结构。模拟TDC电路借助电容的充放电实现时间放大,例如时间间隔扩 展法和时间幅度转换法,但是该方法存在非线性问题和大规模集成问题。数字型TDC基于延 时单元链,可采用游标法、多相位时钟等方法实现高分辨率。 目前,德国ACAM公司设计的TDC-GP系列芯片具有高分辨率和优良的DNL/INL性能 指标,但存在测量范围的局限性。该系列芯片采用抽头延迟链架构。TDC-GP21和TDC-GP22芯 片的单通道测量分辨率为90ps,双精度模式45ps,四精度模式22ps,环境温度为-40℃~85 ℃。 TDC电路根据设计方案,分为基于FPGA和ASIC两种设计方案。基于FPGA设计TDC的 技术优点包括可进行反复编程、规避开发风险、开发周期短和成本低廉。设计人员可基于 FPGA内部大量的编程逻辑单元和布线资源搭建电路系统,但该方案实现的TDC电路分辨率 不高、DNL/INL数值过大,测量数据易受温度和电压的影响。定制ASIC芯片不仅能实现极高 的测量分辨率,而且DNL/INL数值低,线性度良好,但该方案开发周期长、成本昂贵且具有较 高的开发风险,利用这种测量方法能够达到的测量精度可优于10ps。

技术实现要素:

本发明的目的是针对现有技术中的缺陷,而提供一种双测时模式TDC芯片设计制 造,用以精密测量信号start与信号stop之间时间间隔ΔT,所述的TDC芯片包含抽头延迟线 测时电路和并行斐不拉基延迟线测时电路,基于矩阵F范数完成电路性能评估。 为实现本发明的目的所采用的技术方案是: 一种双测时模式TDC芯片设计制造,于两种工作模式完成电路设计,低功耗模式 下,设计抽头延迟线测时电路;高精度模式下,设计并行斐不拉基延迟线测时电路: 抽头延迟线测时电路中,针对某一时间间隔ΔT进行测量,主体电路为延迟链,延 迟链由若干个延时单元级联而成,各延时单元输出端接入D触发器;信号start输入延迟链 并稳定传送,当stop信号到来时完成采样并记录信号start通过延时单元的数目n;τ为延时 3 CN 111723539 A 说 明 书 2/7 页 单元的延时时间,Δτ为测时误差,即有 ΔT=n*τ Δτ(Δτ<τ) 并行斐不拉基延迟线测时电路,该并行斐不拉基延迟线测时电路包含四条延迟 链,信号start输入延迟链并稳定传送,当stop信号到来时完成采样,记录信号start在每条 延迟链中,通过的延时单元数目;每条延迟链包含四种延时单元,延时时间分别为τ1、τ2、τ 3、τ4,每条链的延时单元采用斐不拉基构建方法,第一条链中,从左到右依次为1个τ1,2个τ 2,3个τ3,5个τ4,8个τ1,13个τ2,21个τ3,34个τ4,55个τ1……第二条链中,从左到右依次为1 个τ2,2个τ3,3个τ4,5个τ1,8个τ2,13个τ3,21个τ4,34个τ1,55个τ2……第三条链中,从左到 右依次为1个τ3,2个τ4,3个τ1,5个τ2,8个τ3,13个τ4,21个τ1,34个τ2,55个τ3……第四条链 中,从左到右依次为1个τ4,2个τ1,3个τ2,5个τ3,8个τ4,13个τ1,21个τ2,34个τ3,55个τ 4…… 由于温度对TDC芯片的各项参数皆有影响,抽头延迟线测时电路中,温度分析范围 为5℃~85℃,以5℃为间隔,依次测试17组数据。理想情况下,延迟链所有单元的延时时间 为固定值,且不随温度变化,设置该固定值为θ,延迟链中延时单元的总数为s,构造17行s列 的矩阵M。实际情况下,抽头延迟线电路与并行斐不拉基延迟线测时电路中,各单元延时皆 随温度而改变。构造17行s列矩阵Mθ,采用矩阵F范数完成电路性能评估。 在并行斐不拉基延迟线测时电路中,温度分析范围为5℃~85℃,以5℃为间隔,依 次测试17组数据。理想情况下,四条延迟链中,各延时单元的延时时间不随温度而改变,依 次构造四个17行t列矩阵F1,F2,F3,F4。实际情况中,温度对各延时单元的延时时间皆存在影 响,依次构造四个17行t列矩阵FT1,FT2,FT3,FT4。采用矩阵F范数完成电路性能评估。 基于参数AT和参数BT来评估电路性能,两项参数皆合格时,TDC芯片属于良品芯片。 本发明的TDC芯片包含抽头延迟线测时电路和并行斐不拉基延迟线测时电路,前 者电路结构简单,具有低功耗的优势,后者包含四路延迟链,具有高精度的优势。 附图说明 图1是TDC电路制造流程; 图2是抽头延迟线测时电路结构分析; 图3是抽头延迟线测时电路数学模型; 图4是并行斐不拉基延迟线测时电路结构分析; 图5是并行斐不拉基延迟线测时电路数学模型。