技术摘要:

本发明公开了一种成像元件,包括其中光传感像素分组成包括多个像素的像素单位的像素区域,每个列包括来自至少两个像素单位的像素。所述像素单位的每个经由对应读出线与构造成对向其输出的像素信号进行模拟数字转换的对应读出单元连接。在列方向上延伸的扫描单元被构造 全部

背景技术:

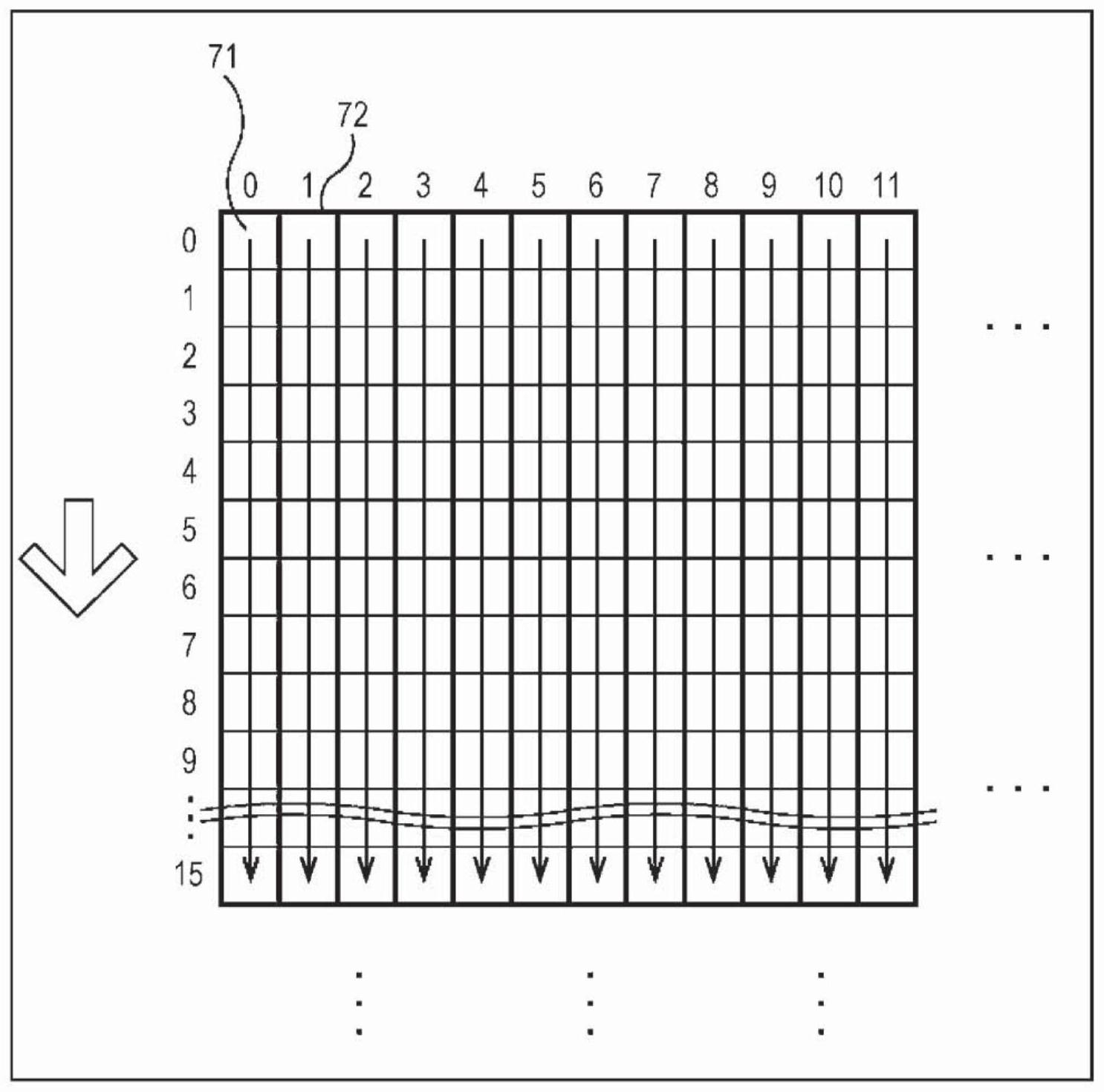

作为安装在数位相机或数码摄像机上的固态成像元件,CMOS图像传感器(以下,缩 写为CIS)是已知的。另外,将CIS用于传感用的成像装置中,并且在这种用途的情况下,特别 需要操作的快速性。 为了使CIS的操作高速化,其中将AD转换单元(以下,缩写为ADC)设置到一个或者 较少数量的像素上并且多个ADC并行操作的方法是已知的。 在这种方法中,当将ADC设置在像素的同一基板内时会牺牲像素的光学特性。 因此,为了不牺牲像素的光学特性,提出了一种其中像素和ADC设置在不同的基板 上并且两个基板使用Cu-Cu接合通过贴合而连接的构成。另外,由于一个ADC的大小通常相 当于多个像素的大小,所以在不同的基板上的多个像素相应地与一个ADC连接(例如,参照 PTL 1)。 图1是其中像素和ADC设置在不同的基板上的CIS的概念图。即,CIS 10由上基板11 和下基板12构成,并且上基板11和下基板12使用Cu-Cu接合等贴合并在对应部分彼此连接。 图2A和图2B示意性地示出了CIS 10的上基板11和下基板12的各个电路构成。 如图2A所示,配置成矩阵的多个像素21、垂直扫描单元23和水平扫描单元24设置 在基板11上。多个像素21的各个根据后述的ADC 31被分成4*4像素的一个像素块22。像素21 利用光电转换处理产生与入射光对应的电荷,蓄积该电荷,并且在基于来自垂直扫描单元 23和水平扫描单元24的控制的扫描时机将与蓄积的电荷对应的像素信号传递到下基板12 的ADC 31。 如图2B所示,下基板12设置有分别对应上基板11的像素块22的多个ADC 31、数字 信号处理单元32、时机生成单元33和DAC 34。各个ADC 31将从属于对应像素块22的多个像 素21顺次传递的模拟像素信号转换成数字信号。 例如,在上基板11的左上边的像素块22与在下基板12的左上边的ADC 31a对应。另 外,类似地,在上基板11的右上边的像素块22与在下基板12的右上边的ADC 31e对应。即,在 上基板11上的像素块22和在下基板12上的ADC 31的各自占用面积及其形状设定为彼此匹 配。 4 CN 111556263 A 说 明 书 2/13 页 图3示出了ADC 31的构成例。ADC 31包括比较单元41和锁存单元42。比较单元41将 从对应像素块22的各像素21顺次传递的模拟像素信号与从DAC 34输入的Ramp信号进行比 较,并且将其比较结果输出到锁存单元42。基于比较单元41的比较结果,当Ramp信号横切像 素信号时,锁存单元42保持输入的代码值。将在锁存单元42中保持的代码值作为数字像素 信号在数字信号处理单元32中读出。 图4示出了构成像素块22的4*4像素的一般扫描顺序。在图中,细线的矩形表示像 素21,粗线表示与一个ADC 31相关的像素块22,数字表示像素的位置,箭头表示像素的扫描 顺序。另外,位于X行和Y列上的像素也被描述为像素(X,Y)。 例如,在其像素(0,0)位于左上的顶点处的像素块中,通过将左上的像素(0,0)设 定为起始点来开始在水平右方向上扫描,顺次使待扫描的行在垂直下方向上移动,并且最 后读出右下的像素(0,3)。类似地,在另一个像素块22中,同样,通过将左上的像素21设定为 起始点来开始在水平右方向上扫描,顺次使待扫描的行在垂直下方向上移动,并且最后读 出右下的像素21。 图5示出了用于将像素块22中的扫描顺序改变到如图4所示的水平方向和垂直方 向上的各像素21的构成例。 像素21由光电二极管(PD)51、转移栅(Trf)52、浮动扩散(FD)53、放大晶体管(Amp) 54、垂直扫描用的选择晶体管(Sel)55、水平扫描用的选择晶体管(Sel)56、复位晶体管 (Rst)57、电源配线58和信号线59构成。 在像素21中,将在作为光电转换元件的PD 51中产生的电荷通过Trf 52传递到与 Amp 54的栅极连接的FD 53。此时,当打开由垂直扫描单元23控制的Sel 55和由水平扫描单 元24控制的Sel 56时,Amp 54将与在FD 53中保持的电荷的电位对应的电压信号经由垂直 信号线59输出到后段的ADC 31。另外,在FD 53中蓄积的电荷在当打开Rst 57时丢弃到电源 配线58中。 [引用文献列表] [专利文献] [PTL 1] 日本未审查专利申请公开No.2009-177207

技术实现要素:

[技术问题] 如图5所示,例如,为了实现图4所示的扫描顺序,两个选择晶体管(Sel 55,56)对 于像素21是必需的,并且如图2A和图2B所示,对于整个CIS 10,水平扫描单元24和垂直扫描 单元23是必须的。因此,一直难以实现像素单元和CIS单元的小型化或者成本的降低。 另外,例如,对于整个CIS,也可以通过省略水平扫描单元仅由垂直扫描单元构成 CIS,然而,即使在这种情况下,由于在4*4像素的像素块的各行中必需四根不同的Sel配线, 所以也难以实现像素单元的小型化。 另外,当4*4像素的像素块22通过与一个ADC 31相关而与其连接时,各像素21的垂 直信号线59一次性一起放在像素块22的中央等。然而,在这种情况下,存在各像素21的配线 的布局变为非对称的并且光学和电气特性由于像素的位置而变得稍微不同的问题。 5 CN 111556263 A 说 明 书 3/13 页 考虑到这种情况完成了本公开,并且以实现像素或CIS的小型化和成本的降低或 者像素之间特性的均匀性的方式完了本公开。 [问题的解决方案] 根据本公开的一种示例性说明,一种成像元件可以包括像素区域,所述像素区域 包括配置成行和列的矩阵形式并分组成包括N个像素的像素单位的多个像素。N可以大于1, 每个列可以包括来自至少两个像素单位的像素,所述多个像素的每个可以被构造成感测光 并将像素信号输出到多根读出线中的一根,所述多根读出线的每根与所述像素单位中对应 像素单位的像素连接。所述成像元件可以包括扫描单元,所述扫描单元在列方向上延伸并 被构造成通过向与对应行的像素连接的扫描线施加扫描脉冲来选择用于读出的像素。所述 成像元件可以包括多个读出单元,每个读出单元与所述多根读出线中对应的读出线连接并 被构造成对向其输出的像素信号进行模拟数字转换。没有在行方向上延伸并向与像素的列 连接的线施加脉冲而能够进行所述的选择用于读出的像素的扫描单元。 根据本公开的另一种示例性说明,一种电子设备可以包括与本公开的第一示例性 说明相关的上述成像元件。 根据本公开的另一种示例性说明,提供了一种图像传感器的驱动方法。所述图像 传感器可以包括像素区域,所述像素区域包括配置成行和列的矩阵形式并分组成包括N个 像素的像素单位的多个像素,其中N>1,每个列包括来自至少两个像素单位的像素,所述多 个像素的每个被构造成感测光并将像素信号输出到多根读出线中的一根,所述多根读出线 的每根与所述像素单位中对应像素单位的像素连接;每个读出单元与所述多根读出线中对 应的读出线连接并被构造成对向其输出的像素信号进行模拟数字转换。所述方法可以包括 通过向与对应行的像素连接的扫描线施加扫描脉冲来选择用于读出的像素。上述选择用于 读出的像素不依赖于向与像素的列连接的线施加任意脉冲。 根据本公开的另一种示例性说明,一种成像元件可以包括像素区域,所述像素区 域包括配置成行和列并分组成包括N个像素的像素单位的多个像素。N可以大于1,每个列可 以包括来自至少两个像素单位的像素,所述多个像素的每个可以被构造成感测光并当被选 择用于读出时将像素信号输出到多根读出线中的一根,所述多根读出线的每根与所述像素 单位中对应像素单位的像素连接。所述成像元件可以包括扫描单元,所述扫描单元在列方 向上延伸并被构造成通过向与对应行的像素连接的扫描线施加扫描脉冲来选择用于读出 的像素。所述成像元件可以包括多个读出单元,每个读出单元与所述多根读出线中对应的 读出线连接并被构造成对向其输出的像素信号进行模拟数字转换。每个扫描脉冲可以独立 于任意其他选择信号来选择与向其施加各个扫描脉冲的所述扫描线连接的用于读出的像 素。 [发明的有益效果] 根据本公开的实施方案,可以实现小型化、成本的降低和像素之间特性的均匀性。 附图说明 图1是由上基板和下基板构成的现有技术中的CIS的概念图。 图2A是示出了图1中的CIS的上基板的构成例的框图。 图2B是示出了图1中的CIS的下基板的构成例的框图。 6 CN 111556263 A 说 明 书 4/13 页 图3是示出了ADC的构成例的框图。 图4是示出了图2A的各像素块中的像素的扫描顺序的图。 图5是示出了其中执行图4中的扫描顺序的像素的构成例的图。 图6A是示出了本公开适用的CIS的上基板的构成例的框图。 图6B是示出了本公开适用的CIS的下基板的构成例的框图。 图7是示出了图6A的各像素块中的像素的扫描顺序的图。 图8是示出了图6A的各像素块中的像素的扫描顺序的图。 图9是示出了其中执行图7中的扫描顺序的像素的第一构成例的图。 图10是示出了其中执行图7中的扫描顺序的像素的第二构成例的图。 图11是示出了根据本公开的成像装置的构成例的框图。