技术摘要:

本申请实施例提供了一种半导体器件及其制造方法,在衬底上可以形成介质层,在介质层中形成第一堆叠层和第二堆叠层,第一堆叠层和第二堆叠层的材料不完全相同,第一堆叠层和第二堆叠层之间的介质层可以作为隔离层,第一堆叠层形成于纵向贯穿介质层的第一通孔中,包括第 全部

背景技术:

随着半导体制造工艺技术的更新迭代,半导体器件的尺寸不断缩小,集成度不断 提高,然而,随着工艺节点的微缩,工艺节点会达到一个极限点,其尺寸无法继续缩小,性能 的提升越来越困难。如何获取小尺寸高性能的器件,是本领域面临的一项重要问题。

技术实现要素:

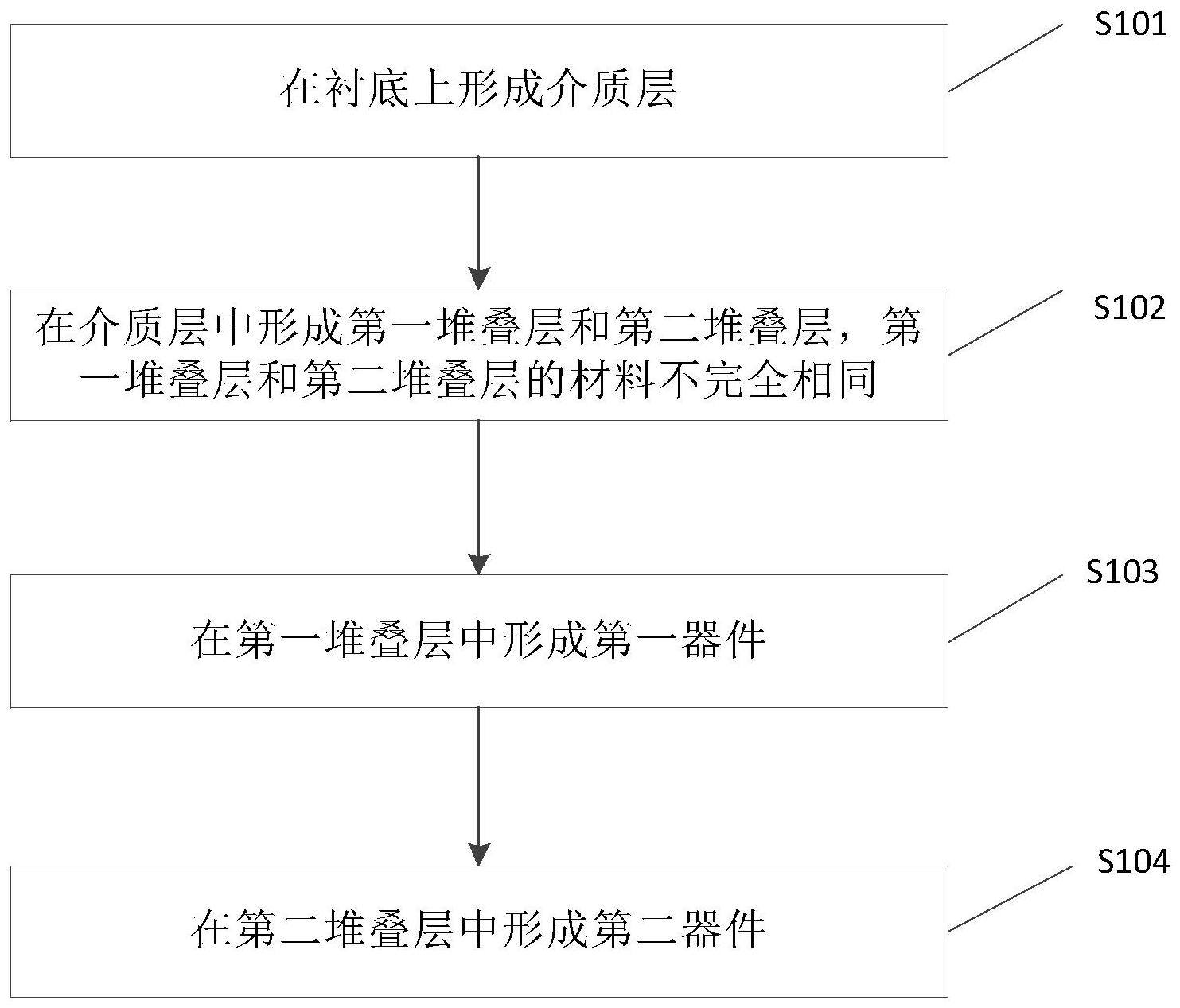

有鉴于此,本申请的目的在于提供一种半导体器件及其制造方法,能够在较小的 器件尺寸的前提下实现较高的性能。 为实现上述目的,本申请有如下技术方案: 本申请实施例提供了一种半导体器件的制造方法,包括: 在衬底上形成介质层; 在所述介质层中形成第一堆叠层和第二堆叠层,所述第一堆叠层和所述第二堆叠 层的材料不完全相同,所述第一堆叠层和所述第二堆叠层之间的介质层作为隔离层;所述 第一堆叠层形成于纵向贯穿所述介质层的第一通孔中,包括第一掺杂材料层、第一沟道层 和第二掺杂材料层;所述第二堆叠层形成于纵向贯穿所述介质层的第二通孔中,包括第三 掺杂材料层、第二沟道层和第四掺杂材料层; 在所述第一堆叠层中形成第一器件; 在所述第二堆叠层中形成第二器件; 其中,所述第一器件包括所述隔离层侧壁的第一掺杂材料层、第一沟道层和第二 掺杂材料层,以及第一间隙中的第一栅介质层和第一栅极层;所述第一沟道层在所述第一 堆叠层除与所述隔离层接触的侧壁之外的至少一侧侧壁上凹于所述第一掺杂材料层和所 述第二掺杂材料层,使所述第一掺杂材料层和所述第二掺杂材料层之间形成所述第一间 隙; 所述第二器件包括所述隔离层侧壁的第三掺杂材料层、第二沟道层和第四掺杂材 料层,以及第二间隙中的第二栅介质层和第二栅极层;所述第二沟道层在所述第二堆叠层 除与所述隔离层接触的侧壁之外的至少一侧侧壁上凹于所述第三掺杂材料层和所述第四 掺杂材料层,使所述第三掺杂材料层和所述第四掺杂材料层之间形成所述第二间隙。 可选的, 在所述第一堆叠层中形成第一器件,包括: 对所述介质层进行刻蚀形成第一沟槽,以暴露所述第一堆叠层除与所述隔离层接 触的侧壁之外的至少一侧侧壁;通过所述第一沟槽从侧向对所述第一沟道层进行刻蚀,保 留所述隔离层侧壁上的第一沟道层,以形成所述第一掺杂材料层和所述第二掺杂材料层之 间的第一间隙;通过所述第一沟槽在所述第一间隙中形成第一栅介质层和第一栅极层;利 5 CN 111599757 A 说 明 书 2/15 页 用介质材料填充所述第一沟槽; 在所述第二堆叠层中形成第二器件,包括: 对所述介质层进行刻蚀形成第二沟槽,以暴露所述第二堆叠层除与所述隔离层接 触的侧壁之外的至少一侧侧壁;通过所述第二沟槽从侧向对所述第二沟道层进行刻蚀,保 留所述隔离层侧壁上的第二沟道层,以形成所述第一掺杂材料层和所述第二掺杂材料层之 间的第一间隙;通过所述第二沟槽在所述第二间隙中形成第二栅介质层和第二栅极层;利 用介质材料填充所述第二沟槽。 可选的, 所述通过所述第一沟槽从侧向对所述第一沟道层进行刻蚀,包括: 进行多次第一氧化去除工艺,所述第一氧化去除工艺包括:进行所述第一沟道层 的氧化工艺,以在所述第一沟槽中暴露的第一沟道层表面上形成第一氧化层;去除所述第 一氧化层; 所述通过所述第二沟槽从侧向对所述第二沟道层进行刻蚀,包括: 进行多次第二氧化去除工艺,所述第二氧化去除工艺包括:进行所述第二沟道层 的氧化工艺,以在所述第二沟槽中暴露的第二沟道层表面上形成第二氧化层;去除所述第 二氧化层。 可选的, 所述通过所述第一沟槽在所述第一间隙中形成第一栅介质层和第一栅极层,包 括: 沉积第一栅介质层和第一栅极层,并通过所述第一沟槽去除所述第一间隙之外的 第一栅极层和第一栅介质层; 所述通过所述第二沟槽在所述第二间隙中形成第二栅介质层和第二栅极层,包 括: 沉积第二栅介质层和第二栅极层,并通过所述第二沟槽去除所述第二间隙之外的 第二栅极层和第二栅介质层。 可选的,所述第一掺杂材料层、所述第一沟道层和所述第二掺杂材料层依次为硅 锗、硅、硅锗,或硅、硅锗、硅,或锗、锗锡、锗;所述第三掺杂材料层、所述第二沟道层和所述 第四掺杂材料层依次为硅锗、硅、硅锗,或硅、硅锗、硅,或锗、锗锡、锗。 可选的,所述衬底和所述第一掺杂材料层之间形成有缓冲层,和/或,所述衬底和 所述第三掺杂材料层之间形成有缓冲层。 可选的,所述第一掺杂材料层和所述第一沟道层之间形成有所述第一掺杂材料层 的本征层,所述第一沟道层和所述第二掺杂材料层之间形成有所述第二掺杂材料层的本征 层;和/或,所述第三掺杂材料层和所述第二沟道层之间形成有所述第三掺杂材料层的本征 层,所述第二沟道层和所述第四掺杂材料层之间形成有所述第四掺杂材料层的本征层。 可选的,还包括: 将所述隔离层替换为绝缘层;所述绝缘层包括第一应变材料层和/或第二应变材 料层,所述第一应变材料层形成于所述第一堆叠层侧壁,用于为所述第一沟道层提供压应 力或张应力,所述第二应变材料层形成于所述第二堆叠层侧壁,用于为所述第二沟道层提 供压应力或张应力。 6 CN 111599757 A 说 明 书 3/15 页 本申请实施例还提供了一种半导体器件,包括: 衬底; 所述衬底上的介质材料; 所述介质材料中的第一堆叠层;所述第一堆叠层形成于纵向贯穿所述介质材料的 第一通孔中,包括第一掺杂材料层、第一沟道层和第二掺杂材料层; 所述介质材料中的第二堆叠层,所述第一堆叠层和所述第二堆叠层的材料不完全 相同,所述第一堆叠层和所述第二堆叠层之间的介质层作为隔离层;所述第二堆叠层形成 于纵向贯穿所述介质材料的第二通孔中,包括第三掺杂材料层、第二沟道层和第四掺杂材 料层; 所述第一堆叠层中的第一器件,所述第一器件包括第一掺杂材料层、第一沟道层 和第二掺杂材料层,以及第一间隙中的第一栅介质层和第一栅极层;所述第一沟道层在所 述第一堆叠层除与所述隔离层接触的侧壁之外的至少一侧侧壁上凹于所述第一掺杂材料 层和所述第二掺杂材料层,使所述第一掺杂材料层和所述第二掺杂材料层之间形成所述第 一间隙; 所述第二堆叠层中的第二器件,所述第二器件包括第三掺杂材料层、第二沟道层 和第四掺杂材料层,以及第二间隙中的第二栅介质层和第二栅极层;所述第二沟道层在所 述第二堆叠层除与所述隔离层接触的侧壁之外的至少一侧侧壁上凹于所述第三掺杂材料 层和所述第四掺杂材料层,使所述第一掺杂材料层和所述第二掺杂材料层之间形成所述第 二间隙。 可选的,所述第一掺杂材料层、所述第一沟道层和所述第二掺杂材料层依次为硅 锗、硅、硅锗,或硅、硅锗、硅,或锗、锗锡、锗;所述第三掺杂材料层、所述第二沟道层和所述 第四掺杂材料层依次为硅锗、硅、硅锗,或硅、硅锗、硅,或锗、锗锡、锗。 可选的,所述衬底和所述第一掺杂材料层之间形成有缓冲层,和/或,所述衬底和 所述第三掺杂材料层之间形成有缓冲层。 可选的,所述第一掺杂材料层和所述第一沟道层之间形成有所述第一掺杂材料层 的本征层,所述第一沟道层和所述第二掺杂材料层之间形成有所述第二掺杂材料层的本征 层;和/或,所述第三掺杂材料层和所述第二沟道层之间形成有所述第三掺杂材料层的本征 层,所述第二沟道层和所述第四掺杂材料层之间形成有所述第四掺杂材料层的本征层。 可选的,所述第一堆叠层和所述第二堆叠层之间形成有绝缘层;所述绝缘层包括 第一应变材料层和/或第二应变材料层,所述第一应变材料层形成于所述第一堆叠层侧壁, 用于为所述第一沟道层提供压应力或张应力,所述第二应变材料层形成于所述第二堆叠层 侧壁,用于为所述第二沟道层提供压应力或张应力。 本申请实施例提供了一种半导体器件及其制造方法,在衬底上可以形成介质层, 在介质层中形成第一堆叠层和第二堆叠层,第一堆叠层和第二堆叠层的材料不完全相同, 第一堆叠层和第二堆叠层之间的介质层可以作为隔离层,第一堆叠层形成于纵向贯穿介质 层的第一通孔中,包括第一掺杂材料层、第一沟道层和第二掺杂材料层,第二堆叠层形成于 纵向贯穿介质层的第二通孔中,包括第三掺杂材料层、第二沟道层和第四掺杂材料层,之 后,可以在第一堆叠层中形成第一器件,以及在第二堆叠层中形成第二器件。 其中,所述第一器件包括所述隔离层侧壁的第一掺杂材料层、第一沟道层和第二 7 CN 111599757 A 说 明 书 4/15 页 掺杂材料层,以及第一间隙中的第一栅介质层和第一栅极层;所述第一沟道层在所述第一 堆叠层除与所述隔离层接触的侧壁之外的至少一侧侧壁上凹于所述第一掺杂材料层和所 述第二掺杂材料层,使所述第一掺杂材料层和所述第二掺杂材料层之间形成所述第一间 隙; 所述第二器件包括所述隔离层侧壁的第三掺杂材料层、第二沟道层和第四掺杂材 料层,以及第二间隙中的第二栅介质层和第二栅极层;所述第二沟道层在所述第二堆叠层 除与所述隔离层接触的侧壁之外的至少一侧侧壁上凹于所述第三掺杂材料层和所述第四 掺杂材料层,使所述第一掺杂材料层和所述第二掺杂材料层之间形成所述第二间隙。 这样,第一器件中,第一掺杂材料层和第二掺杂材料层作为源漏,源漏之间存在纵 向的第一沟道层,在第二器件中,第三掺杂材料层和第四掺杂材料层作为源漏,源漏之间存 在纵向的第二沟道层,第一沟道层和第二沟道层的长度与膜层的厚度相关,无需高成本高 精度的刻蚀,因此能够利用较低的成本和简易的工艺得到小尺寸高性能的器件,此外,由于 衬底上可以包括不同材料的第一堆叠层和第二堆叠层,则可以包括不同材料构成的第一器 件和第二器件,因此能够提供多样化的器件结构,更能满足用户需求。 附图说明 为了更清楚地说明本申请实施例或现有技术中的技术方案,下面将对实施例或现 有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图是本申请 的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据 这些附图获得其它的附图。 图1示出了本申请实施例中一种半导体器件的制造方法的流程示意图; 图2-图27示出了根据本申请实施例的制造方法形成半导体器件过程中的结构示 意图; 图28和图29示出了本申请实施例提供的一种堆叠层分布示意图。