技术摘要:

本发明公开了一种基于长短期记忆网络的缓存替换系统及方法,该系统包括中央处理器、分类器以及缓存控制器,分类器由输入产生器和决策器组成;该方法包括步骤:1)将中央处理器的地址发送到输入产生器中,输入产生器计算当前地址的钥匙,并将钥匙发送至决策器中;2)决策 全部

背景技术:

通用中央处理器(CPU)是信息技术产业的根基,随着软件技术的不断发张,对硬件 性能,特别是中央处理器的性能要求越来越高。在2002年以前,根据摩尔定律,芯片密度和 CPU的时钟频率不断增高,带来CPU性能的大幅度提升。但是2002年之后,摩尔定律逐渐失 效,这是因为晶体管的尺寸越来越小,晶体管之间的传输延迟远远大于单元延迟,并难以再 大幅度减小,成为限制CPU时钟频率的主要因素。另外一个原因是,频率增高使得CPU的功耗 达到了芯片承受的极限。为了能进一步提高CPU的性能,人们开始去突破CPU的内存瓶颈,即 主存访问速度。缓存(Cache)被放置在CPU寄存器和主存之间来弥补CPU处理速度和主存访 问速度之间的巨大差异,而缓存管理技术则可以实现用层级少、体量小的缓存结构实现更 大的速度补偿,成本更低。因此缓存管理技术成为现代处理器研究的重点技术。缓存替换方 法是影响缓存系统性能的一个重要因素,根据程序局部性原理可知:程序在运行中,总是频 繁地使用最近被使用过的指令或数据。缓存替换方法依次为理论依据,合理地安排数据的 存储,提高缓存的命中率,让CPU尽可能在缓存中访问到数据,减小访问延迟,最终达到提高 处理器性能的目的。 神经网络算法具有很强的非线性映射能力,其中循环神经网络擅长于处理各类时 间序列问题,而缓存替换方法的本质是研究访问序列的特征,并根据特征将其存储于缓存 或者从缓存中移除,研究目标访问序列也是具有时序信息的地址集合,所以本文考虑将循 环神经网络中的长短期记忆网络(LSTM)与缓存替换方法相结合,这是一次较为崭新的尝 试,因为相关的工作非常少,有个别研究只停留在软件仿真上,说明了神经网络和缓存替换 方法交叉研究的可能性。利用长短期记忆网络提取缓存访问序列特征,并以此对访问地址 实时分类,准确地将CPU“想”访问的数据存储在缓存中,以这样一种新的思路设计缓存替换 方法,突破内存访问瓶颈将会非常具有应用价值。 受硬件资源的限制,传统缓存替换方法的研究热点在于捕获访问地址的复用距 离,或者短期历史内的访问频率,并依次为标准,更新缓存中不同数据的被替换的优先级, 更新机制较为简单以便于用简单的硬件逻辑实现。它们着眼于可以观察到的常见访问序 列,利用频率计数器,复用距离预测器等模块启发性地管理缓存替换,所以缓存命中率不会 很高。这些年,随着晶体管技术的发展,缓存管理设计时的资源限制缓解,可以将一些简单 的机器学习方法应用到缓存替换方法中。新兴的缓存替换方法将缓存替换转换为一个二分 类问题。预测访问地址的缓存特性“是否应该被缓存”,并具有识别程序类型,并不断调整替 换策略的能力。 4 CN 111582455 A 说 明 书 2/6 页

技术实现要素:

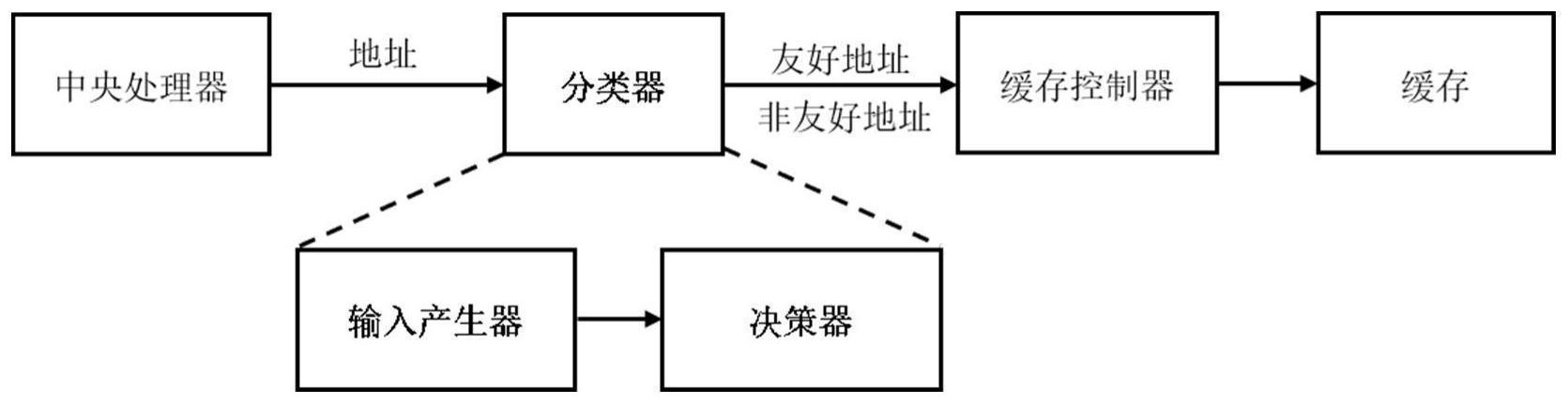

本发明的目的在于提供一种基于长短期记忆网络的缓存替换系统及方法,使得通 用处理器缓存访问缺失率显著降低,减小片外存储器带宽要求。本发明的重点在于,使得缓 存替换方法具有识别访问序列类型的能力,以及具有预测访问序列缓存特性的能力。 本发明采用如下技术方案来实现的: 一种基于长短期记忆网络的缓存替换系统,包括中央处理器、分类器以及缓存控 制器,分类器由输入产生器和决策器组成;其中,输入产生器用于接受中央处理器发送的地 址,计算当前地址的钥匙,并将钥匙发送至决策器中,决策器接收钥匙后,采用四种预测器 对当前钥匙进行分类,并在各自的小缓存中进行实验,根据命中与否更新各自计数器的数 值,选择器通过比较四种预测器的计数器数值,取最高数值所属预测器的结果,作为最后一 级缓存的缓存特性,缓存控制器依据缓存特性更新缓存;利用缓存特性,中央处理器将缓存 特性的影响加入缓存数据块的优先级更新机制中。 本发明进一步的改进在于,输入产生器包括地址列表、遍历器、计数器、阈值产生 器、比较器、钥匙生成器、加法器和钥匙列表;其中, 地址列表存储中央处理器发出的地址,遍历器获取地址并在地址列表中遍历统计 当前地址的二级制个数,并通过计数器将二级制转化为十进制,再传送至阈值产生器中计 算阈值;钥匙列表存储历史钥匙,并通过加法器获计算钥匙列表中值为“1”的钥匙个数,在 比较器中比较钥匙个数与阈值,输出结果传送至钥匙生成器中,结合遍历器产生的“Flag” 信号,得到当前地址的钥匙;当清除信号有效时,将钥匙列表中的元素置“0”。 本发明进一步的改进在于,决策器包括周期计数器、四个预测器、四个采样缓存、 四个计数器、选择器和MUX4;周期计数器每个周期增加1,当数值等于阈值时,发出清零信号 传送至四个预测器和选择器;四个预测器接收钥匙后各自输出缓存特性至MUX4,并传送至 各自的采样缓存中,采样缓存根据缓存特性更新内容并判断是否命中,各自的计数器统计 采样缓存的命中数,并传送至选择器;选择器比较四个计数器值,将最大值计数器的索引传 送至MUX4,MUX4根据索引将对应预测的缓存特性输出。 本发明进一步的改进在于,预测器包括依次连接的长短期记忆层、全连接层和分 类层,长短期记忆层接收钥匙进行计算,将输出传送至全连接层,全连接层将计算结果传送 至分类层,分类层输出缓存特性。 本发明进一步的改进在于,长短期记忆层包括门模块、网络模块和存储模块;存储 模块由B,Wb,Wx,H,C组成;门模块由乘法阵列、加法阵列A、加法阵列B、加法阵列C和MUX2组 成;其中,乘法阵列与存储模块的Wb和H相连,乘法阵列的输出连接至加法阵列A,加法阵列B 接收MUX2的输出和加法阵列A的输出,将计算结果传送至加法阵列C,加法阵列C根据加法阵 列B的输出和存储模块的B计算结果,并传送至网络模块;MUX2接收存储模块的Wx和输入数 据X;网络模块由选择器A、Sigmoid、Tanh、选择器B、乘法器和累加器组成;门模块的输出与 选择器A和Sigmoid连接,选择器输出与Tanh连接,Sigmoid输出与乘法器连接,Tanh输出与 选择器B连接,选择器B接收存储模块的C并将计算结果与乘法器连接,乘法器输出与累加器 连接,并传送至存储模块的H,累加器的输出与存储模块的C连接。 本发明进一步的改进在于,全连接层由乘法阵列和加法阵列组成;乘法阵列输出 多个数据,传送至加法阵列;加法阵列由多层加法器树组成。 5 CN 111582455 A 说 明 书 3/6 页 本发明进一步的改进在于,分类层由一个比较器组成。 一种基于长短期记忆网络的缓存替换方法,该方法基于上述一种基于长短期记忆 网络的缓存替换系统,该方法包括以下步骤: 1)将中央处理器的地址发送到输入产生器中,输入产生器计算当前地址的钥匙, 并将钥匙发送至决策器中; 2)决策器接收钥匙后,采用四种预测器对当前钥匙进行分类,并在各自的小缓存 中进行实验,根据命中与否更新各自计数器的数值,选择器通过比较四种预测器的计数器 数值,取最高数值所属预测器的结果,作为最后一级缓存的缓存特性,缓存控制器依据缓存 特性更新缓存; 3)利用缓存特性,中央处理器将缓存特性的影响加入缓存数据块的优先级更新机 制中,得到性能更高的缓存替换方法。 本发明至少具有如下有益的技术效果: 本发明有以下特点: 1 .在输入产生器的硬件设计中。输入产生器接收短期内的历史访问地址和钥匙, 采用遍历的方式,在地址列表和钥匙列表搜索当前地址和钥匙,可以保证较高的准确度。 2.在决策器的硬件设计中,将长短期记忆网络的硬件系统拆解为三部分,存储模 块存储网络参数。门模块用于计算输入门、输出门、遗忘门和记忆单元的向量,采用了乘法 器阵列和多级加法器设计,并插入多级流水线。网络模块用计算网络状态和输出,主要由激 活函数模块和乘、加法器组成,并使用选择器合理地安排网络状态和输出数据的计算,根据 门模块统筹网络模块的并行度。 本发明有以下优点: 1、本发明利用长短期记忆网络能更准确地识别访问序列类型,并且预测访问序列 的缓存特性。 2、本发明设置四类长短期记忆网络,同时判断当前访问序列的缓存特性,并在附 带的小缓存中实施替换方法,实时监控附带小缓存的性能,并将最后一级缓存切换至性能 最高的长短期记忆网络,实现适应不同程序的能力。 3、本发明实现的长短期记忆网络硬件结构,具有低功耗、低资源消耗和低延迟的 特点。 附图说明 图1为本发明基于长短期记忆网络的缓存替换系统的架构图。 图2为输入产生器的硬件结构图。 图3为决策器的硬件结构图。 图4为预测器的通用硬件结构图。 图5为长短期记忆层的硬件结构图。 图6为门模块的计算过程示意图。 图7为全连接层的计算过程示意图。 图8为分类层的计算过程示意图。 6 CN 111582455 A 说 明 书 4/6 页