技术摘要:

本发明提供一种低温多晶氧化物阵列基板及其制作方法。本发明提供的阵列基板,包括衬底基板以及设置在衬底基板上的薄膜晶体管组件,薄膜晶体管组件包括第一半导体层、第一源极、第一漏极、第二半导体层、第二源极、第二漏极和公共栅极;第一半导体层、第一源极、第一漏 全部

背景技术:

薄膜晶体管液晶显示器(Thin Film Transistor Liquid Crystal Display,简 称:TFT-LCD)具有体积小、功耗低、无辐射等特点,在当前的平板显示器市场中占据了主导 地位。近年来随着TFT-LCD的飞速发展,尤其液晶电视的发展更为迅速,大尺寸、高分辨率的 液晶电视成为TFT-LCD发展的主流。 传统TFT-LCD通常采用多晶硅薄膜晶体管,其迁移率较高,迁移率大于30cm2/V.s。 多晶硅薄膜晶体管一般通过准分子激光退火(Excimer Laser Annealing,简称:ELA)工艺 制作而成,但是在进行激光退火时,由于激光脉冲宽幅的限制,形成的多晶硅均一性差,这 直接影响到薄膜晶体管的均一性,使其不适用于大尺寸的液晶面板;另外,多晶硅薄膜晶体 管虽然迁移率高,但关态电流大,用其驱动像素电极时功耗较高。目前,TFT-LCD还采用金属 氧化物薄膜晶体管,金属氧化物薄膜晶体管也具有较高的迁移率,一般在10-30cm2/V.s左 右,虽然迁移率比多晶硅薄膜晶体管稍低,但也可以充分满足像素区域的驱动需求,且金属 氧化物薄膜晶体管的关态电流远小于多晶硅薄膜晶体管,用其驱动像素电极,可以降低显 示面板的功耗。 但是,随着显示产品向大尺寸、高分辨率的方向发展,薄膜晶体管在像素中的面积 占比越来越大,使得像素的开口率降低,功耗增加。

技术实现要素:

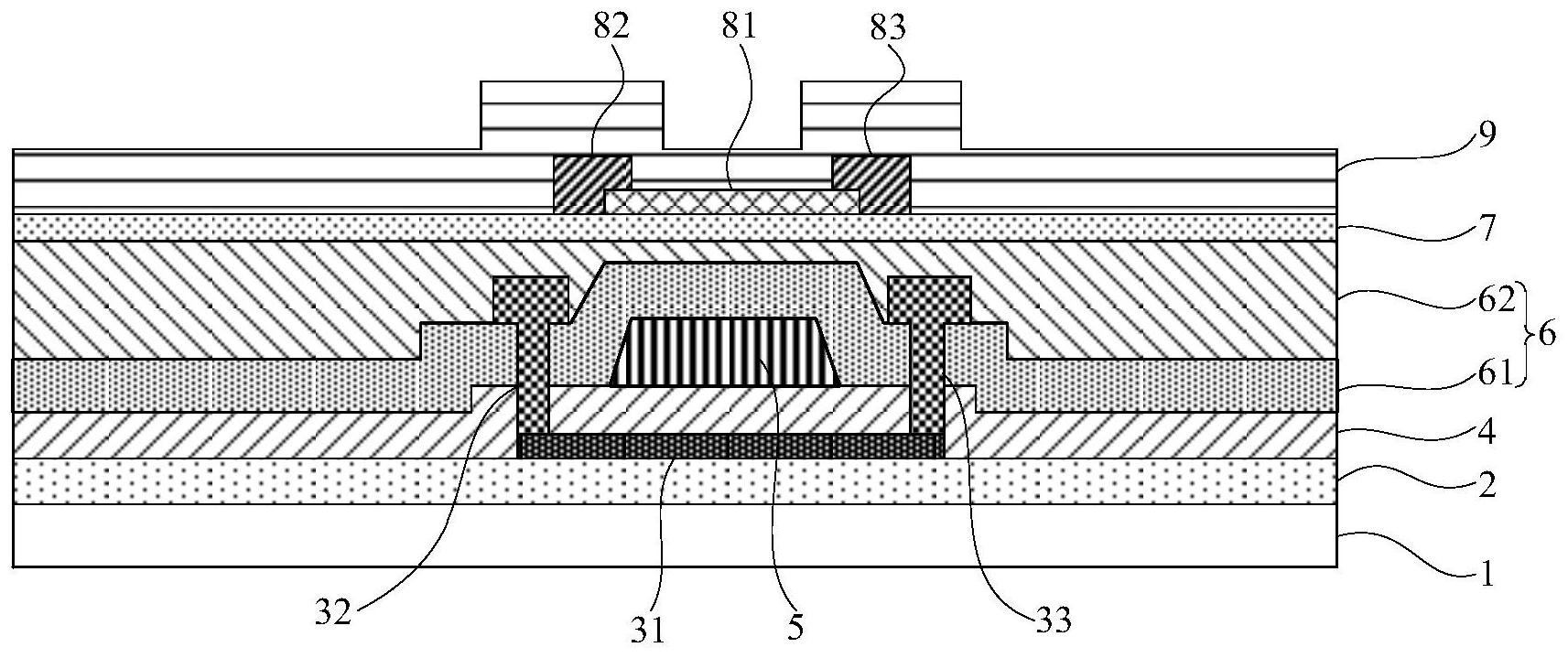

本发明提供一种低温多晶氧化物阵列基板及其制作方法,阵列基板在满足高分辨 率要求的同时,可增大像素开口率,降低功耗。 本发明的一方面提供一种低温多晶氧化物阵列基板,该阵列基板包括衬底基板以 及设置在衬底基板上的薄膜晶体管组件,薄膜晶体管组件包括第一半导体层、第一源极、第 一漏极、第二半导体层、第二源极、第二漏极和公共栅极,第一源极和第一漏极分别连接在 第一半导体层两侧,第二源极和第二漏极分别连接在第二半导体层两侧; 第一半导体层、第一源极、第一漏极和公共栅极形成第一薄膜晶体管,第二半导体 层、第二源极、第二漏极和公共栅极形成第二薄膜晶体管,第二薄膜晶体管沿阵列基板的层 叠方向设于第一薄膜晶体管上方,且第一薄膜晶体管和第二薄膜晶体管中的一者在衬底基 板上的正投影位于另一者在衬底基板上的正投影的覆盖范围内; 其中,第一半导体层和第二半导体层中的一者为多晶硅半导体层,另一者为金属 氧化物半导体层。 在一种可能的实施方式中,公共栅极沿阵列基板的层叠方向设于第一半导体层和 第二半导体层之间,公共栅极用于驱动第一薄膜晶体管和第二薄膜晶体管。 4 CN 111725243 A 说 明 书 2/14 页 在一种可能的实施方式中,薄膜晶体管组件还包括设置在衬底基板上的缓冲层, 第一半导体层设置在缓冲层上;其中,缓冲层包括依次层叠在衬底基板上的第一缓冲层和 第二缓冲层。 在一种可能的实施方式中,薄膜晶体管组件还包括依次层叠设置在缓冲层上的栅 绝缘层和栅极保护层,栅绝缘层覆盖第一半导体层,公共栅极设置在栅绝缘层上,栅极保护 层覆盖公共栅极;其中,栅极保护层和栅绝缘层中设置有连通至第一半导体层的接触孔,第 一源极和第一漏极设置在栅极保护层中并通过接触孔与第一半导体层接触。 在一种可能的实施方式中,栅极保护层包括依次层叠在栅绝缘层上的第一栅极保 护层和第二栅极保护层,第一源极和第一漏极设置在第一栅极保护层和第二栅极保护层之 间。 在一种可能的实施方式中,薄膜晶体管组件还包括依次层叠设置在栅极保护层上 的氧化物绝缘层和金属氧化物保护层,第二半导体层及第二源极、第二漏极均设置在氧化 物绝缘层上,金属氧化物保护层覆盖第二半导体层及第二源极、第二漏极。 本发明的另一方面提供一种低温多晶氧化物阵列基板的制作方法,用于制作如上 任一项所述的低温多晶氧化物阵列基板,该制作方法包括如下步骤: 在衬底基板上形成第一薄膜晶体管;其中,第一薄膜晶体管包括第一半导体层、第 一源极、第一漏极和公共栅极,第一源极和第一漏极分别连接在第一半导体层两侧; 在第一薄膜晶体管上形成第二薄膜晶体管,第二薄膜晶体管与第一薄膜晶体管在 垂直于衬底基板的方向上具有重叠区域;其中,第二薄膜晶体管包括第二半导体层、第二源 极、第二漏极和公共栅极,第二源极和第二漏极分别连接在第二半导体层两侧,且第一半导 体层和第二半导体层中的一者为多晶硅半导体层,另一者为金属氧化物半导体层。 在一种可能的实施方式中,在第一薄膜晶体管上形成第二薄膜晶体管,具体包括: 在第一薄膜晶体管上形成位于第一薄膜晶体管的覆盖范围内的第二薄膜晶体管; 或者, 在第一薄膜晶体管上形成完全覆盖第一薄膜晶体管的第二薄膜晶体管。 在一种可能的实施方式中,在第一薄膜晶体管上形成第二薄膜晶体管,具体包括: 在第一半导体层、第一源极和第一漏极的上方形成公共栅极,公共栅极用于驱动 第一薄膜晶体管和第二薄膜晶体管; 在公共栅极的上方形成第二半导体层、第二源极和第二漏极。 在一种可能的实施方式中,在衬底基板上形成第一薄膜晶体管,具体包括: 在衬底基板上形成缓冲层;其中,缓冲层包括依次层叠在衬底基板上的第一缓冲 层和第二缓冲层; 在缓冲层上形成第一半导体层; 在缓冲层上形成栅绝缘层,栅绝缘层覆盖第一半导体层; 在栅绝缘层上形成公共栅极; 在栅绝缘层上形成栅极保护层,栅极保护层覆盖公共栅极; 在栅极保护层中形成第一源极和第一漏极,第一源极和第一漏极与第一半导体层 接触。 在一种可能的实施方式中,在栅极保护层中形成第一源极和第一漏极,具体包括: 5 CN 111725243 A 说 明 书 3/14 页 在栅绝缘层上形成第一栅极保护层,第一栅极保护层覆盖公共栅极; 在第一栅极保护层和栅绝缘层中形成连通至第一半导体层的接触孔; 在第一栅极保护层上形成第一源极和第一漏极,第一源极和第一漏极通过接触孔 与第一半导体层接触; 在第一栅极保护层上形成第二栅极保护层,第二栅极保护层覆盖第一源极和第一 漏极。 在一种可能的实施方式中,在第一薄膜晶体管上形成第二薄膜晶体管,具体包括: 在第二栅极保护层上形成氧化物绝缘层; 在氧化物绝缘层上形成第二半导体层; 在氧化物绝缘层上形成第二源极和第二漏极,第二源极和第二漏极分别搭接在第 二半导体层两侧; 在氧化物绝缘层上形成金属氧化物保护层,金属氧化物保护层覆盖第二半导体层 及第二源极、第二漏极。 本发明提供一种低温多晶氧化物阵列基板及其制作方法,阵列基板通过在衬底基 板上设置第一薄膜晶体管和第二薄膜晶体管组成薄膜晶体管组件,其中第一薄膜晶体管的 半导体层采用多晶硅半导体层,第二薄膜晶体管的半导体层采用金属氧化物半导体层;通 过多晶硅半导体层驱动第一薄膜晶体管,通过金属氧化物半导体层驱动第二薄膜晶体管, 第一薄膜晶体管和第二薄膜晶体管共同作用于阵列基板的每个像素,可以大尺寸显示面板 的高分辨率需求;同时,通过第一薄膜晶体管和第二薄膜晶体管沿阵列基板的层叠方向设 置,且第一薄膜晶体管和第二薄膜晶体管在竖直方向上具有重叠区域,这样可以减少像素 内薄膜晶体管组件占据的面积比例,增大像素开口率,降低功耗。 LTPO(Low Temperature Polycrystalline Oxide,低温多晶氧化物)薄膜晶体管 阵列基板通过在一个子像素内集成低温多晶硅(Low Temperature Poly-silicon,简称: LTPS)TFT和氧化物(Oxide)TFT这两种器件,LTPO面板技术结合了LTPS TFT工艺驱动能力强 和Oxide TFT工艺漏电小、功耗低的优点,利用LTPS TFT驱动显示器,Oxide TFT用于开关, 因而可以有效降低显示面板的功耗。 附图说明 为了更清楚地说明本发明或现有技术的技术方案,下面将对实施例或现有技术描 述中所需要使用的附图作一简单地介绍,显而易见地,下面描述中的附图是本发明的一些 实施例,对于本领域普通技术人员来讲,在不付出创造性劳动性的前提下,还可以根据这些 附图获得其他的附图。 图1为本发明实施例一提供的低温多晶氧化物阵列基板的结构示意图; 图2为本发明实施例二提供的低温多晶氧化物阵列基板的制作方法的流程示意 图; 图3为本发明实施例二提供的在衬底基板上形成第一薄膜晶体管的流程示意图; 图4为本发明实施例二提供的在衬底基板上形成缓冲层的结构示意图; 图5为本发明实施例二提供的在缓冲层上形成第一半导体层的结构示意图; 图6为本发明实施例二提供的在缓冲层上形成栅绝缘层的结构示意图; 6 CN 111725243 A 说 明 书 4/14 页 图7为本发明实施例二提供的在栅绝缘层上形成公共栅极的结构示意图; 图8为本发明实施例二提供的在栅绝缘层上形成第一栅极保护层的结构示意图; 图9为本发明实施例二提供的在第一栅极保护层和栅绝缘层中形成接触孔的结构 示意图; 图10为本发明实施例二提供的在第一栅极保护层上形成第一源极和第一漏极的 结构示意图; 图11为本发明实施例二提供的在第一栅极保护层上形成第二栅极保护层的结构 示意图; 图12为本发明实施例二提供的在第一薄膜晶体管上形成第二薄膜晶体管的流程 示意图; 图13为本发明实施例二提供的在第二栅极保护层上形成氧化物绝缘层的结构示 意图; 图14为本发明实施例二提供的在氧化物绝缘层上形成第二半导体层的结构示意 图; 图15为本发明实施例二提供的在氧化物绝缘层上形成第二源极和第二漏极的结 构示意图; 图16为本发明实施例二提供的在氧化物绝缘层上形成金属氧化物保护层的结构 示意图。 附图标记说明: 1-衬底基板;2-缓冲层;31-第一半导体层;32-第一源极;33-第一漏极;4-栅绝缘 层;41-接触孔;5-公共栅极;6-栅极保护层;61-第一栅极保护层;62-第二栅极保护层;7-氧 化物绝缘层;81-第二半导体层;82-第二源极;83-第二漏极;9-金属氧化物保护层。