技术摘要:

本发明提供基准电压电路以及半导体装置。基准电压电路具备第1MOS晶体管对和第2MOS晶体管对,其中,所述第1MOS晶体管对具备:第一导电型增强型的第1MOS晶体管,其栅极与漏极连接;和第一导电型耗尽型的第2MOS晶体管,其栅极与第1MOS晶体管的源极连接,源极与第1MOS晶体 全部

背景技术:

一直以来,在半导体装置中,使用由增强型MOS晶体管和耗尽型MOS晶体管的阈值 电压的绝对值之和来决定输出电压的基准电压电路。 已知对于那样的基准电压电路输出的基准电压,通过使增强型MOS晶体管和耗尽 型MOS晶体管的各阈值电压的温度依赖性相互抵消,使得温度依赖性变小。此外,通过增加 耗尽型MOS晶体管或增强型MOS晶体管中的任一方的数量,能够得到任意的高基准电压(例 如,参照专利文献1的图2至图4)。 现有技术文献 专利文献1:日本特开2015-141462号公报 然而,在专利文献1所记载的基准电压电路中,为了使增强型MOS晶体管和耗尽型 MOS晶体管偏置而具备两个以上的恒流源。因此,由于在两个以上的路径中始终流过电流, 因此难以减小消耗电流。

技术实现要素:

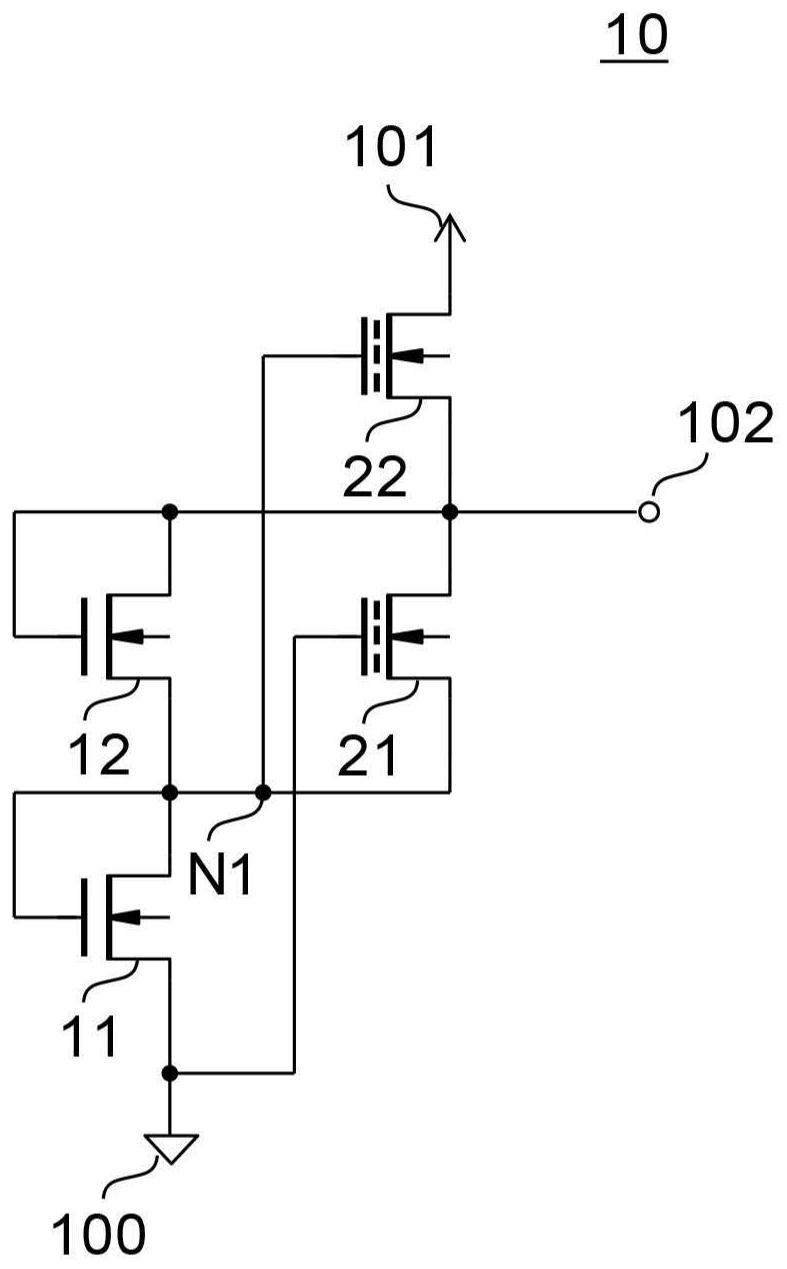

本发明是鉴于上述课题而完成的,其目的在于提供一种消耗电流微小、能够任意 地将基准电压设定得较高的基准电压电路。 本发明的一个实施方式的基准电压电路的特征在于, 所述基准电压电路具备第1MOS晶体管对、第2MOS晶体管对以及输出端子, 所述第1MOS晶体管对具备: 第一导电型增强型的第1MOS晶体管,其栅极与漏极连接;和 第一导电型耗尽型的第2MOS晶体管,其栅极与所述第1MOS晶体管的源极连接,源 极与所述第1MOS晶体管的漏极连接,漏极与所述输出端子连接, 所述第2MOS晶体管对具备: 第一导电型增强型的第3MOS晶体管,其栅极和漏极与所述输出端子连接,源极与 所述第2MOS晶体管的源极连接;和 第一导电型耗尽型的第4MOS晶体管,其栅极与所述第3MOS晶体管的源极连接,源 极与所述输出端子连接, 全部MOS晶体管在弱反型区中工作。 根据本发明的基准电压电路,由于消耗电流取决于进行弱反型工作的第一导电型 增强型的MOS晶体管(第1MOS晶体管)的电流,因此能够容易地使消耗电流微小。 附图说明 图1是用于说明本发明的实施方式的基准电压电路的电路图。 3 CN 111552344 A 说 明 书 2/4 页 图2是用于说明本实施方式的基准电压电路的另一例的电路图。 图3是用于说明本实施方式的基准电压电路的另一例的电路图。 图4是用于说明本实施方式的基准电压电路的另一例的电路图。 标号说明 10、20:基准电压电路; 11、12、13:第一导电型增强型MOS晶体管; 21、22、23:第一导电型耗尽型MOS晶体管; 31:第二导电型增强型MOS晶体管; 11:接地端子; 101:电源端子; 102:输出端子。