技术摘要:

本发明公开了一种数字芯片外设时钟的产生方法及系统,主要是选取n位寄存器,从低位到高位为寄存器N1到寄存器Nn;在初始化时,为各位寄存器分别赋初值0或1;设定所要产生的外设时钟周期长度为m;产生外设时钟时,参考高频时钟频率为f;当接受到第x个高频参考时钟信号时, 全部

背景技术:

在数字芯片中通常都包含有同步外设接口,而同步外设的时钟由外设的时钟发生 器来驱动,并通过芯片管脚向外输出。外设时钟一般都由计数器从一个高频时钟f分频得 到。这种外设时钟发生方法原理如下: 1)设定计数器初值为N,时钟发生器输出初值为0; 2)每接收一个高频参考时钟,计数器减1; 3)每接收一个高频参考时钟,比较计数器的值:如果计数器等于[N/2],则时钟发生器 输出1;如果计数器等于1,则时钟发生器输出为0,同时将计数器重新加载到N;其他情况,时 钟发生器输出保持不变。 由上述原理可知,这种外设时钟发生系统只能进行整数分频,即输出时钟为参考 时钟f的1/N,并且占空比固定为1/2(N为偶数)或者[N/2]/N。这产生的时钟有一定限制,降 低了外设的兼容性和使用的便利性。同时,由于输出外设时钟的上升沿和下降沿间隔固定, 使得时钟的频谱能量集中在设定的频率上,当时钟通过芯片管脚向外输出时,对系统的电 磁干扰较强。

技术实现要素:

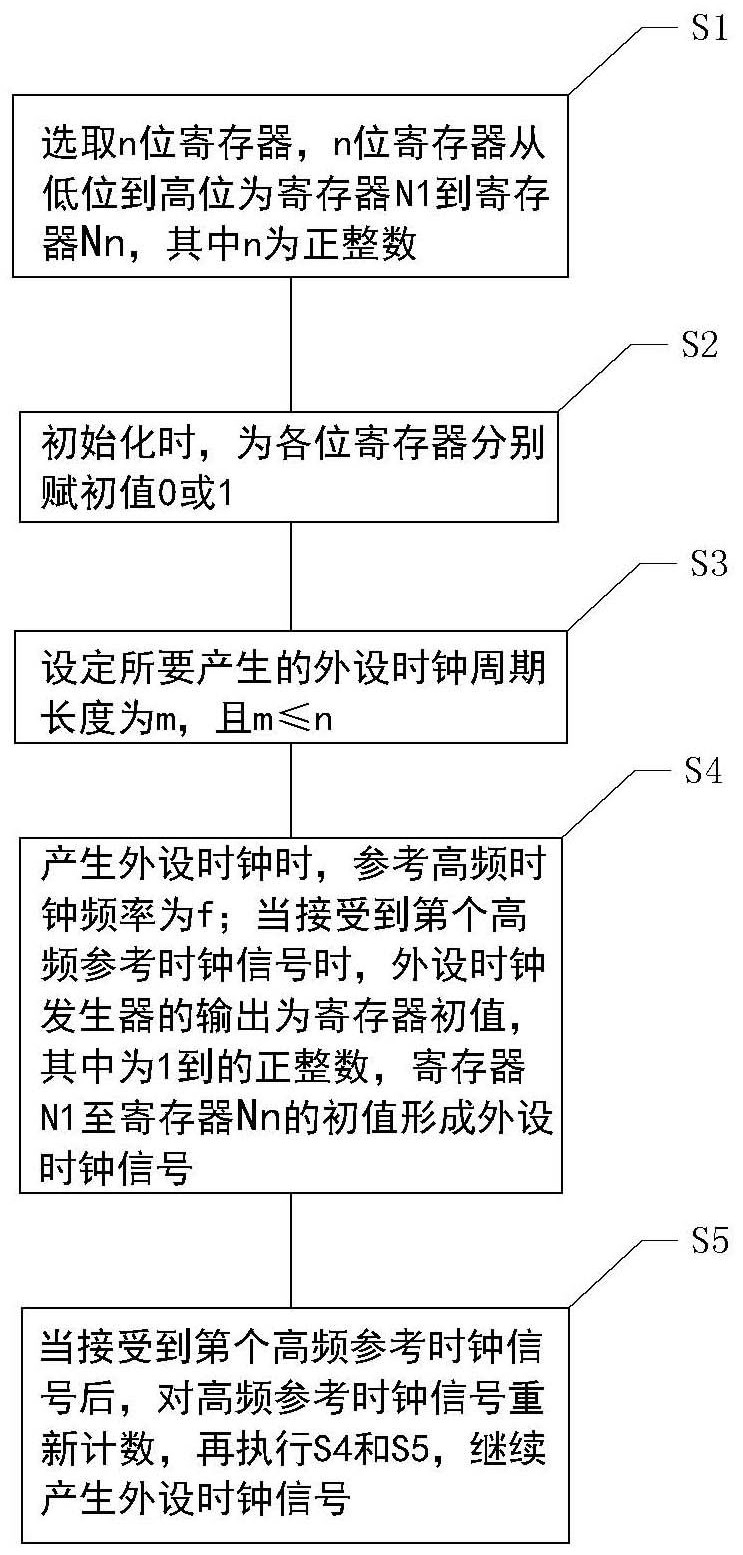

针对上述不足,本发明所要解决的技术问题是:提供一种数字芯片外设时钟的产 生方法及系统,通过本发明可以产生分数分频、可调整占空比、可调整频率及可产生一定的 扩频功能,降低对系统的电磁干扰。 为解决上述技术问题,本发明的技术方案是: 一种数字芯片外设时钟的产生方法,包括以下步骤: S1、选取n位寄存器,n位寄存器从低位到高位为寄存器N1到寄存器Nn,其中n为正整数; S2、初始化时,为各位寄存器分别赋初值0或1; S3、设定所要产生的外设时钟周期长度为m,且m≤n; S4、产生外设时钟时,参考高频时钟频率为f;当接受到第x个高频参考时钟信号时,外 设时钟发生器的输出为寄存器Nx初值,其中x为1到m的正整数,寄存器N1至寄存器Nm的初值 形成外设时钟信号; S5、当接受到第m个高频参考时钟信号后,对高频参考时钟信号重新计数,再执行S4和 S5,继续产生外设时钟信号。 优选方式为,n位寄存器的初值形成上升序列、下降序列和普通序列中的一种或几 种;相邻两位寄存器的初值分别为0和1时,此相邻两位寄存器初值形成上升序列;相邻两位 寄存器的初值分别为1和0时,此相邻两位寄存器初值形成下降序列;相邻两位寄存器的初 4 CN 111600604 A 说 明 书 2/4 页 值同时为0或1时,此相邻两位寄存器初值形成普通序列。 优选方式为,所述S2中,初始化时,使寄存器N1至寄存器Nm的初值中包括y个上升 序列,则产生的外设时钟信号频率为f×y/m,其中y为不大于m的正整数。 优选方式为,设置m可以被y整除,则外设时钟信号是对高频参考时钟f的m/y整数 分频。 优选方式为,n位寄存器的初值形成上升序列和下降序列,通过调整上升序列和下 降序列之间的间隔,来调整所产生外设时钟信号的占空比。 优选方式为,n位寄存器的初值形成上升序列和下降序列,调整上升序列和下降序 列之间的间隔相等或不等,使所产生的外设时钟信号频率在f×y/m附近跳动。 一种数字芯片外设时钟的产生系统,包括主控单元及分别与所述主控单元电连接 的寄存器单元、参考高频时钟、时钟计数器和外设时钟发生器;所述寄存器单元包括n位寄 存器,n位寄存器从低位到高位为寄存器N1到寄存器Nn ;所述主控单元在初始化时,为各位 寄存器分别赋初值0或1;所述参考高频时钟用于输出频率为f的参考高频时钟信号;所述时 钟计数器用于对所述参考高频时钟输出的参考高频时钟信号计数;所述外设时钟发生器用 于在接受到第x个高频参考时钟信号时,输出寄存器Nx的初值,其中x为1到m的正整数,寄存 器N1至寄存器Nm的初值形成外设时钟信号;当接受到第m个高频参考时钟信号后,所述主控 单元对控制所述时钟计数器清零重新计数,所述外设时钟发生器继续产生外设时钟。 优选方式为,还包括与所述主控单元电连接的频率设定单元,所述频率设定单元 根据所要产生的外设时钟信号频率,传输对应的频率电信号给所述主控单元,所述频率电 信号包括各寄存器的初值,所述主控单元根据接收的频率电信号,在初始化时设置各寄存 器的初值。 优选方式为,所要产生的外设时钟频率为f×y/m时,其中y为不大于m的正整数;所 述频率电信号为设置寄存器N1至寄存器Nm的初值包括y个上升序列,相邻两位寄存器的初 值分别为0和1时,此相邻两位寄存器初值形成上升序列。 优选方式为,还包括与所述主控单元电连接的占空比调节单元,所述占空比调节 单元根据所要产生的外设时钟信号占空比,传输对应的调节电信号给所述主控单元,所述 调节电信号为各寄存器初值形成的上升序列和下降序列之间的间隔,相邻两位寄存器的初 值分别为1和0时,此相邻两位寄存器初值形成下降序列;所述主控单元根据接收的调节电 信号,在初始化时设置各寄存器的初值。 采用上述技术方案后,本发明的有益效果是: 由于本发明的数字芯片外设时钟的产生方法及系统,主要是选取位寄存器,从低位到 高位分别为寄存器N1到寄存器Nn;在初始化时,为各位寄存器分别赋初值0或1;设定所要产 生的外设时钟周期长度为m;产生外设时钟时,参考高频时钟频率为f;当接受到第x个高频 参考时钟信号时,外设时钟发生器的输出为寄存器Nx初值,寄存器N1至寄存器Nm的初值形 成外设时钟信号;当接受到第m个高频参考时钟信号后,对高频参考时钟信号重新计数,外 设时钟发生器再继续产生外设时钟信号。采用本发明产生的外设时钟具有更多的自由端, 可调整所产生的外设时钟的频率和占空比,可以产生分数分频,可以产生一定的扩频功能, 降低对系统的电磁干扰。 5 CN 111600604 A 说 明 书 3/4 页 附图说明 图1是本发明数字芯片外设时钟的产生方法的流程图; 图2是本发明的框图; 图3是本发明数字芯片外设时钟的产生系统的原理框图。