技术摘要:

本发明题为“具有应力竖直半导体沟道的三维存储器器件及其制备方法”。本发明公开了三维存储器器件,其包括在竖直半导体沟道中引起竖直拉伸应力以增强载流子迁移率的结构。竖直拉伸应力可以由应力源柱结构所施加的横向压缩应力引起。所述应力源柱结构可以包含应力源材 全部

背景技术:

包括每个单元具有一个位的三维竖直NAND串的三维半导体器件在T.Endoh等人的 标题为“Novel Ultra High Density Memory With A Stacked-Surrounding Gate Transistor(S-SGT)Structured Cell(具有堆叠的围绕栅极晶体管(S-SGT)结构化单元的 新型超高密度存储器)”,IEDM Proc.(2001)33-36的文章中公开。

技术实现要素:

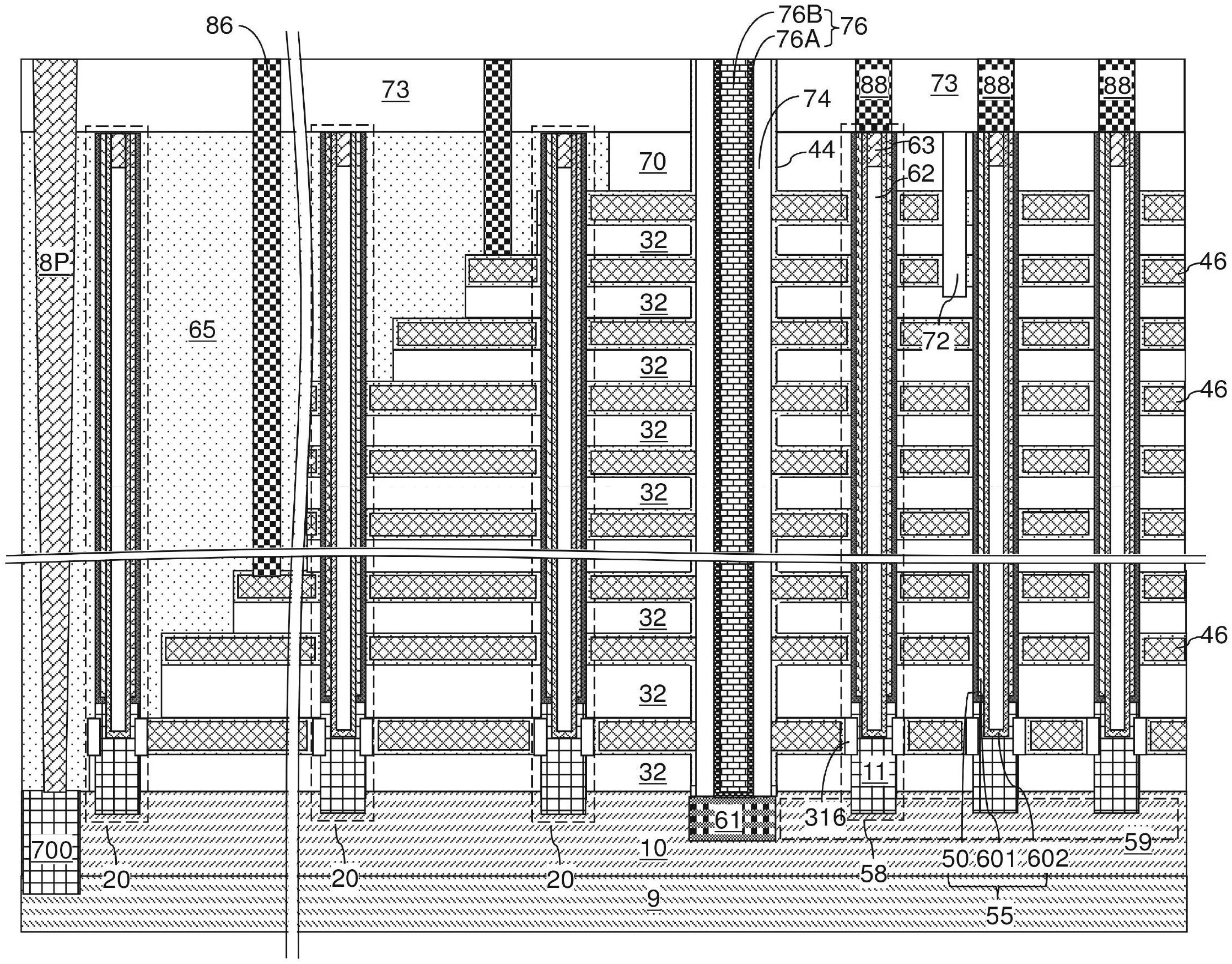

根据本公开的一个方面,提供了一种三维存储器器件,该三维存储器器件包括:绝 缘层和导电层的交替堆叠,该交替堆叠定位在衬底上方;存储器堆叠结构,所述存储器堆叠 结构竖直延伸穿过所述交替堆叠,其中所述存储器堆叠结构包括存储器膜和竖直半导体沟 道,所述存储器膜含有定位在所述导电层的层级处的存储器元件的竖直堆叠,所述竖直半 导体沟道接触所述存储器膜;以及应力源柱结构,该应力源柱结构定位在竖直半导体沟道 的一侧上。该应力源柱结构向竖直半导体沟道施加竖直拉伸应力;所述应力源柱结构的横 向范围由至少一个基本上竖直的介电侧壁表面限定,所述至少一个基本上竖直的介电侧壁 表面提供围绕所述应力源柱结构的闭合周边;所述应力源柱结构基本上由应力源材料组成 并且其中不包含除所述应力源材料之外的任何固体或液体材料;并且该应力源材料选自介 电金属氧化物材料、在应力下沉积的氮化硅、热氧化硅或具有比竖直半导体沟道的晶格常 数更大的晶格常数的半导体材料。 根据本公开的另一方面,提供了一种形成三维存储器器件的方法,该方法包括:在 衬底上方形成绝缘层和间隔物材料层的交替堆叠,其中间隔物材料层形成为导电层或随后 被导电层替换;竖直穿过所述交替堆叠形成存储器堆叠结构,其中所述存储器堆叠结构包 括存储器膜和竖直半导体沟道,所述存储器膜含有定位在所述间隔物材料层的层级处的存 储器元件的竖直堆叠,所述竖直半导体沟道接触所述存储器膜;以及在竖直半导体沟道的 一侧上形成应力源柱结构。该应力源柱结构向竖直半导体沟道施加竖直拉伸应力;所述应 力源柱结构的横向范围由至少一个基本上竖直的介电侧壁表面限定,所述至少一个基本上 竖直的介电侧壁表面提供围绕所述应力源柱结构的闭合周边;所述应力源柱结构基本上由 应力源材料组成并且其中不包含除所述应力源材料之外的任何固体或液体材料;并且该应 8 CN 111587489 A 说 明 书 2/48 页 力源材料选自介电金属氧化物材料、在应力下沉积的氮化硅、热氧化硅或具有比竖直半导 体沟道的晶格常数更大的晶格常数的半导体材料。 根据本公开的另一方面,提供了一种形成三维存储器器件的方法,该方法包括:在 衬底上方形成绝缘层和牺牲材料层的交替堆叠;形成穿过所述交替堆叠的存储器开口;在 所述存储器开口中形成存储器堆叠结构,其中所述存储器堆叠结构包括存储器膜和竖直半 导体沟道,所述存储器膜含有定位在所述牺牲材料层的层级处的存储器元件的竖直堆叠, 所述竖直半导体沟道接触所述存储器膜;用导电层替换所述牺牲材料层;以及向存储器堆 叠结构径向施加横向压缩应力。该横向压缩应力在竖直半导体沟道中沿竖直方向引起拉伸 应力。通过以下操作来提供施加到存储器堆叠结构的横向压缩应力:通过移除牺牲材料层 来形成背侧凹陷部并在背侧凹陷部内沉积生成压缩应力的导电材料;或者将生成压缩应力 的牺牲材料用于牺牲材料层以提供横向压缩应力并且通过在用导电层替换牺牲材料层之 前记住通过快速热退火(RTA)工艺施加到存储器堆叠结构的横向压缩应力。 根据本公开的另一方面,提供了一种三维存储器器件,该三维存储器器件包括:绝 缘层和导电层的交替堆叠,该交替堆叠定位在衬底上方;存储器堆叠结构,所述存储器堆叠 结构竖直延伸穿过所述交替堆叠,其中所述存储器堆叠结构包括存储器膜和竖直半导体沟 道,所述存储器膜含有定位在所述导电层的层级处的存储器元件的竖直堆叠,所述竖直半 导体沟道接触所述存储器膜;源极接触层,所述源极接触层位于所述交替堆叠下方并且横 向围绕所述竖直半导体沟道并接触所述竖直半导体沟道的侧壁;以及介电填充材料层,该 介电填充材料层位于源极接触层下方并且包括杨氏模量小于源极接触层的材料的杨氏模 量的70%的介电填充材料。 根据本公开的另一方面,提供了一种形成三维存储器器件的方法,该方法包括:在 衬底上方形成平面牺牲材料层和过程中源极层级材料层,其中该过程中源极层级材料层包 括源极层级牺牲层;在所述过程中源极层级材料层上方形成绝缘层和间隔物材料层的交替 堆叠,其中所述间隔物材料层形成为导电层,或者随后被所述导电层替换;竖直延伸穿过所 述交替堆叠形成存储器堆叠结构,其中所述存储器堆叠结构包括存储器膜和竖直半导体沟 道,所述存储器膜含有定位在所述间隔物材料层的层级处的存储器元件的竖直堆叠,所述 竖直半导体沟道接触所述存储器膜;用源极接触层替换所述源极层级牺牲层和所述存储器 膜的环形部分,其中所述源极接触层围绕所述竖直半导体沟道并接触所述竖直半导体沟道 的侧壁;以及将平面牺牲材料层替换在介电填充材料层内,该介电填充材料层包含杨氏模 量小于源极接触层的材料的杨氏模量的70%的介电填充材料。 根据本公开的另一方面,提供了一种形成三维存储器器件的方法,该方法包括:在 衬底上方形成绝缘层和间隔物材料层的交替堆叠,其中间隔物材料层形成为导电层或随后 被导电层替换;形成延伸穿过所述交替堆叠的存储器开口;在所述存储器开口的侧壁上形 成存储器膜,其中所述存储器膜包括定位在所述间隔物材料层的层级处的存储器元件的竖 直堆叠;在所述存储器膜的内侧壁上形成第一半导体沟道层,其中所述第一竖直半导体层 包含原子浓度大于98%的硅并且不含锗或包含原子浓度小于2%的锗;以及在第一半导体 沟道层的内侧壁上形成第二半导体沟道层,其中该第二半导体沟道层包含硅锗合金,该硅 锗合金包含原子浓度在3%至50%范围内的锗。 9 CN 111587489 A 说 明 书 3/48 页 附图说明 图1是根据本公开的实施方案的在形成至少一个外围器件和半导体材料层之后的 第一示例性结构的示意性竖直剖面图。 图2是根据本公开的实施方案的在形成绝缘层和牺牲材料层的交替堆叠之后的第 一示例性结构的示意性竖直剖面图。 图3是根据本公开的实施方案的在形成阶梯式平台和后向阶梯式介电材料部分之 后的第一示例性结构的示意性竖直剖面图。 图4A是根据本公开的实施方案的在形成存储器开口和支撑开口之后的第一示例 性结构的示意性竖直剖面图。 图4B是图4A的第一示例性结构的俯视图。竖直平面A-A’为图4A的剖面的平面。 图5A至图5H是根据本公开的实施方案的在形成处于第一构型的存储器开口填充 结构期间的第一示例性结构内的存储器开口的顺序示意性竖直剖面图。 图5I是根据本公开的实施方案的处于第一构型的派生构型的存储器开口填充结 构的示意性竖直剖面图。 图6是根据本公开的实施方案的处于第二构型的存储器开口填充结构的示意性竖 直剖面图。 图7A至图7D是根据本公开的实施方案的在形成处于第三构型的存储器开口填充 结构期间的第一示例性结构内的存储器开口的顺序示意性竖直剖面图。 图8是根据本公开的实施方案的处于第四构型的存储器开口填充结构的示意性竖 直剖面图。 图9A至图9D是根据本公开的实施方案的在形成处于第五构型的存储器开口填充 结构期间的第一示例性结构内的存储器开口的顺序示意性竖直剖面图。 图9E示意性地示出了根据本公开的实施方案的第一半导体沟道层经受竖直拉伸 应力的机制。 图10A至图10D是根据本公开的实施方案的在形成处于第六构型的存储器开口填 充结构期间的第一示例性结构内的存储器开口的顺序示意性竖直剖面图。 图11示出了氮化硅衬垫所生成的应力作为在氮化硅衬垫的沉积期间所使用的 N2O/NH3的比率的函数的相关性。 图12A是根据本公开的实施方案的在形成背侧沟槽之后的第一示例性结构的示意 性竖直剖面图。 图12B是图12A的第一示例性结构的局部透视俯视图。竖直平面A-A’为图12A的示 意性竖直剖面图的平面。 图13是根据本公开的实施方案的在形成背侧凹陷部之后的第一示例性结构的示 意性竖直剖面图。 图14A至图14D是根据本公开的实施方案的在形成导电层期间的第一示例性结构 的区的顺序竖直剖面图。 图15是图9D的处理步骤处的第一示例性结构的示意性竖直剖面图。 图16A是根据本公开的实施方案的在从背侧沟槽内移除沉积的导电材料之后的第 一示例性结构的示意性竖直剖面图。 10 CN 111587489 A 说 明 书 4/48 页 图16B是图16A的第一示例性结构的局部透视俯视图。竖直平面A-A’为图16A的示 意性竖直剖面图的平面。 图17A是根据本公开的实施方案的在形成绝缘间隔物和背侧接触结构之后的第一 示例性结构的示意性竖直剖面图。 图17B是图17A的第一示例性结构的区的放大视图。 图18A是根据本公开的实施方案的在形成附加接触通孔结构之后的第一示例性结 构的示意性竖直剖面图。 图18B是图18A的第一示例性结构的俯视图。竖直平面A-A’为图18A的示意性竖直 剖面图的平面。 图19A是根据本公开的实施方案的包括分裂单元三维存储器元件的第二示例性结 构的俯视图。 图19B是沿着图19A的竖直平面B-B’的竖直剖面图。 图20A是根据本公开的实施方案的包括平坦单元三维存储器元件的第三示例性结 构的竖直剖面图。 图20B是图20A的示例性结构的俯视图。竖直平面A-A’是图20A的竖直剖面图的平 面。 图21A是根据本公开的第一实施方案的在半导体衬底上形成半导体器件、较低层 级介电层、较低金属互连结构和过程中源极层级材料层之后的第四示例性结构的竖直剖面 图。 图21B是图21A的第四示例性结构的俯视图。铰接竖直平面A-A’是图21A的竖直剖 面图的平面。 图21C是沿着图21B的竖直平面C-C’的过程中源极层级材料层的放大视图。 图22是根据本公开的实施方案的在形成第一绝缘层和第一间隔物材料层的第一 层交替堆叠之后的第四示例性结构的竖直剖面图。 图23是根据本公开的实施方案的在图案化第一层楼梯区、第一后向阶梯式介电材 料部分和层间介电层之后的第四示例性结构的竖直剖面图。 图24A是根据本公开的实施方案的在形成第一层存储器开口和第一层支撑开口之 后的第四示例性结构的竖直剖面图。 图24B是图24A的第四示例性结构的俯视图。铰接竖直平面A-A’对应于图24A的竖 直剖面图的平面。 图25是根据本公开的实施方案的在形成各种牺牲填充结构之后的第四示例性结 构的竖直剖面图。 图26是根据本公开的实施方案的在形成第二绝缘层和第二间隔物材料层的第二 层交替堆叠、第二阶梯式表面和第二后向阶梯式介电材料部分之后的第四示例性结构的竖 直剖面图。 图27A是根据本公开的实施方案的在形成第二层存储器开口和第二层支撑开口之 后的第四示例性结构的竖直剖面图。 图27B是沿着图27A的水平平面B-B’的第四示例性结构的水平剖面图。铰接竖直平 面A-A’对应于图27A的竖直剖面图的平面。 11 CN 111587489 A 说 明 书 5/48 页 图28是根据本公开的实施方案的在形成层间存储器开口和层间支撑开口之后的 第四示例性结构的竖直剖面图。 图29A至图29D示出了根据本公开的实施方案的在形成存储器开口填充结构期间 的存储器开口的顺序竖直剖面图。 图30是根据本公开的实施方案的在形成存储器开口填充结构和支撑柱结构之后 的第四示例性结构的竖直剖面图。 图31A是根据本公开的实施方案的在形成背侧柱腔体之后的第四示例性结构的竖 直剖面图。 图31B是沿着图31A的水平平面B-B’的第四示例性结构的水平剖面图。铰接竖直平 面A-A’对应于图31A的竖直剖面图的平面。 图32是根据本公开的实施方案的在形成介电柱结构之后的第四示例性结构的竖 直剖面图。 图33A是根据本公开的实施方案的在形成第一接触级介电层和背侧沟槽之后的第 四示例性结构的竖直剖面图。 图33B是沿着图33A的水平平面B-B’的第四示例性结构的水平剖面图。铰接竖直平 面A-A’对应于图33A的竖直剖面图的平面。 图34是根据本公开的实施方案的在形成背侧沟槽间隔物之后的第四示例性结构 的竖直剖面图。 图35A至图35H示出了根据本公开的实施方案的在分别用源极接触层和介电填充 材料层替换源极层级牺牲层和平面牺牲材料层期间的存储器开口填充结构和背侧沟槽的 顺序竖直剖面图。 图36是根据本公开的实施方案的在形成源极层级材料层之后的第四示例性结构 的竖直剖面图。 图37是根据本公开的实施方案的在形成背侧凹陷部之后的第四示例性结构的竖 直剖面图。 图38是根据本公开的实施方案的在形成导电层之后的第四示例性结构的竖直剖 面图。 图39A是根据本公开的实施方案的在背侧沟槽中形成介电壁结构之后的第四示例 性结构的竖直剖面图。 图39B是沿着图39A的水平平面B-B’的第四示例性结构的水平剖面图。铰接竖直平 面A-A’对应于图39A的竖直剖面图的平面。 图39C是沿着图39B的竖直平面C-C’的第四示例性结构的竖直剖面图。 图39D是在图39A至图39C的处理步骤处的存储器开口填充结构和背侧沟槽的竖直 剖面图。 图40A是根据本公开的实施方案的在形成第二接触级介电层和各种接触通孔结构 之后的第四示例性结构的竖直剖面图。 图40B是沿着图40A的水平平面B-B’的第四示例性结构的水平剖面图。铰接竖直平 面A-A’对应于图40A的竖直剖面图的平面。 图41是根据本公开的实施方案的在形成直通存储器层级通孔结构和上部金属线 12 CN 111587489 A 说 明 书 6/48 页 结构之后的第四示例性结构的竖直剖面图。