技术摘要:

本发明涉及一种信号选择电路和显示装置。所述信号选择电路包括:控制模块与输出模块;控制模块包括控制节点与时钟信号输入端,控制节点与输出模块的控制端连接,输出模块包括第一输入端与第二输入端,第一输入端用于接收第一输入信号,第二输入端用于接收第二输入信号 全部

背景技术:

相关技术中,信号选择电路包括晶体管。由于晶体管存在阈值电压,使得晶体管的 漏极电压与源极电压不同,这样,会导致信号选择电路的输出信号与输入信号不一致的情 况,即存在信号损失。因此,如何减小信号选择电路的信号损失是需要解决的一个技术问 题。

技术实现要素:

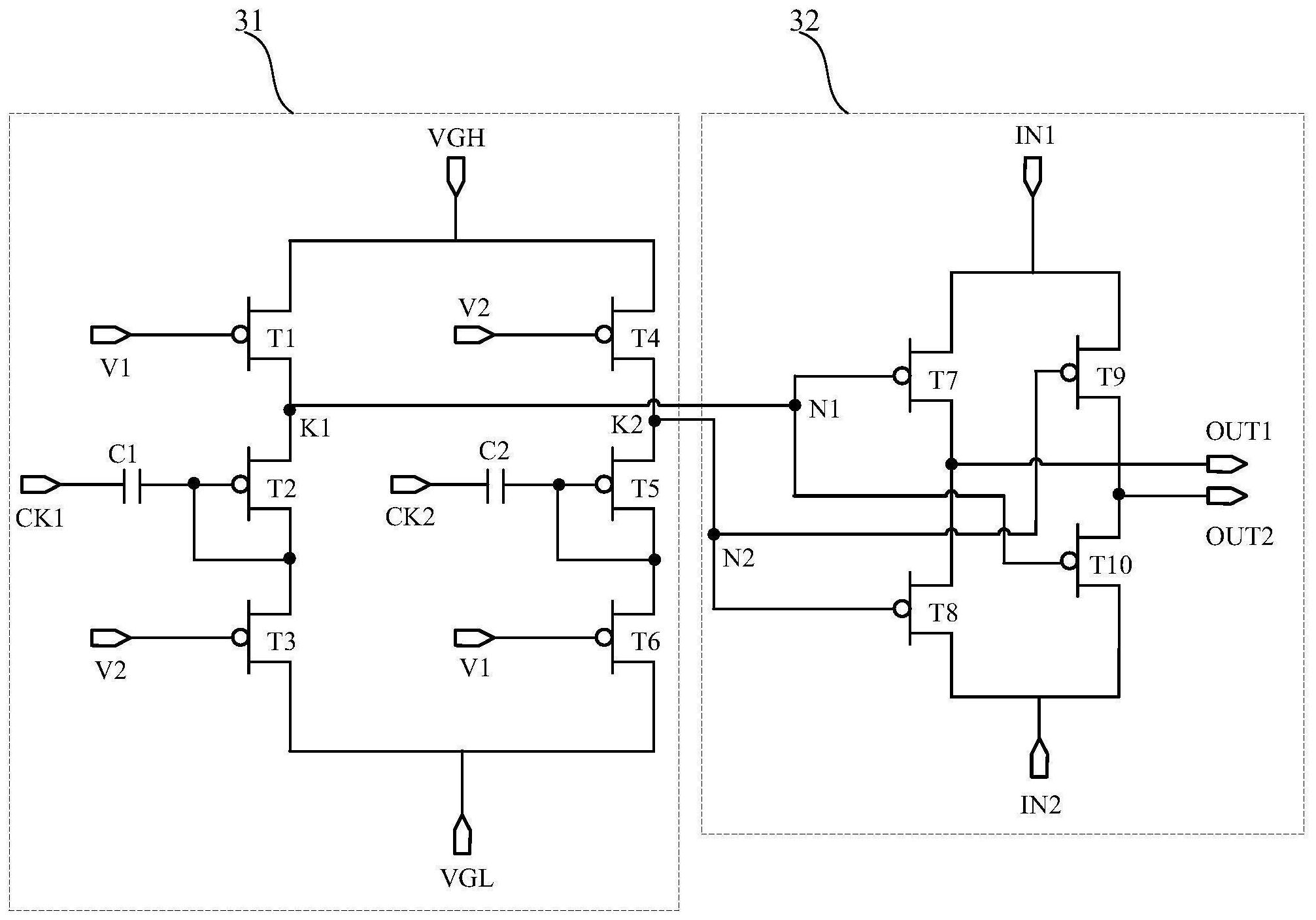

本发明提供一种信号选择电路和显示装置,可以减小信号选择电路的信号损失。 根据本发明实施例的第一方面,提供一种信号选择电路,包括:控制模块与输出模 块;所述控制模块包括控制节点与时钟信号输入端,所述控制节点与所述输出模块的控制 端连接,所述输出模块包括第一输入端与第二输入端,所述第一输入端用于接收第一输入 信号,所述第二输入端用于接收第二输入信号,所述输出模块包括第一输出端与第二输出 端,所述第一输出端用于在所述控制节点的控制下根据所述第一输入信号和所述第二输入 信号中的一个输出第一输出信号,所述第二输出端用于在所述控制节点的控制下根据所述 第一输入信号和所述第二输入信号中的另一个输出第二输出信号; 所述时钟信号输入端用于接收时钟信号,以使所述时钟信号由高电平向低电平切 换时,拉低所述控制节点的电平,当所述控制节点的电平被拉低后,所述第一输出信号与所 述第一输入信号和所述第二输入信号中的一个相同,所述第二输出信号与所述第一输入信 号和所述第二输入信号中的另一个相同。 在一个实施例中,所述控制模块包括第一晶体管、第二晶体管、第三晶体管、第四 晶体管、第五晶体管、第六晶体管、第一电容与第二电容,所述控制节点包括第一控制节点 与第二控制节点;所述时钟信号输入端包括第一时钟信号输入端与第二时钟信号输入端。 所述第一晶体管的第一端用于接收高电平信号,所述第一晶体管的控制端用于接收第一电 压信号,所述第一晶体管的第二端连接至所述第二晶体管的第二端,所述第二晶体管的第 一端与所述第二晶体管的控制端连接,所述第二晶体管的控制端连接至所述第一电容的第 一端,所述第一电容的第二端为所述第一时钟信号输入端,所述第二晶体管的第一端还与 所述第三晶体管的第二端连接,所述第三晶体管的第一端用于接收低电平信号,所述第三 晶体管的控制端用于接收第二电压信号,所述第一控制节点与所述第一晶体管的第二端连 接。所述第四晶体管的第一端与所述第一晶体管的第一端并接,用于接收所述高电平信号, 所述第四晶体管的控制端用于接收第二电压信号,所述第四晶体管的第二端连接至所述第 五晶体管的第二端,所述第五晶体管的第一端与所述第五晶体管的控制端连接,所述第五 晶体管的控制端连接至所述第二电容的第一端,所述第二电容的第二端为所述第二时钟信 号输入端,所述第五晶体管的第一端还与所述第六晶体管的第二端连接,所述第六晶体管 4 CN 111613171 A 说 明 书 2/7 页 的第一端与所述第三晶体管的第一端并接,用于接收所述低电平信号,所述第六晶体管的 控制端用于接收所述第一电压信号,所述第二控制节点与所述第四晶体管的第二端连接。 在一个实施例中,所述第一晶体管为P型晶体管,所述第一晶体管的第一端为源 极,所述第一晶体管的第二端为漏极,所述第一晶体管的控制端为栅极。所述第二晶体管为 P型晶体管,所述第二晶体管的第一端为源极,所述第二晶体管的第二端为漏极,所述第二 晶体管的控制端为栅极。所述第三晶体管为P型晶体管,所述第三晶体管的第一端为源极, 所述第三晶体管的第二端为漏极,所述第三晶体管的控制端为栅极。所述第四晶体管为P型 晶体管,所述第四晶体管的第一端为源极,所述第四晶体管的第二端为漏极,所述第四晶体 管的控制端为栅极。所述第五晶体管为P型晶体管,所述第五晶体管的第一端为源极,所述 第五晶体管的第二端为漏极,所述第五晶体管的控制端为栅极。所述第六晶体管为P型晶体 管,所述第六晶体管的第一端为源极,所述第六晶体管的第二端为漏极,所述第六晶体管的 控制端为栅极。 在一个实施例中,所述输出模块包括第七晶体管、第八晶体管、第九晶体管与第十 晶体管,所述输出模块的控制端包括第一控制端与第二控制端。所述第七晶体管的第一端 连接至所述第一输入端,所述第七晶体管的控制端连接至所述第一控制端,所述第一控制 端连接至所述第一控制节点,所述第七晶体管的第二端与所述第一输出端连接。所述第八 晶体管的第一端连接至所述第二输入端,所述第八晶体管的控制端连接至所述第二控制 端,所述第二控制端接至所述第二控制节点,所述第八晶体管的第二端与所述第一输出端 连接。所述第九晶体管的第一端连接至所述第一输入端,所述第九晶体管的控制端连接至 所述第二控制端,所述第九晶体管的第二端与所述第二输出端连接。所述第十晶体管的第 一端连接至所述第二输入端,所述第十晶体管的控制端连接至所述第一控制端,所述第十 晶体管的第二端与所述第二输出端连接。 在一个实施例中,所述第七晶体管为P型晶体管,所述第七晶体管的第一端为源 极,所述第七晶体管的第二端为漏极,所述第七晶体管的控制端为栅极。所述第八晶体管为 P型晶体管,所述第八晶体管的第一端为源极,所述第八晶体管的第二端为漏极,所述第八 晶体管的控制端为栅极。所述第九晶体管为P型晶体管,所述第九晶体管的第一端为源极, 所述第九晶体管的第二端为漏极,所述第九晶体管的控制端为栅极。所述第十晶体管为P型 晶体管,所述第十晶体管的第一端为源极,所述第十晶体管的第二端为漏极,所述第十晶体 管的控制端为栅极。 在一个实施例中,所述第一电压信号为所述高电平信号,所述第二电压信号为低 电平信号,所述第一输出端根据所述第一输入信号输出所述第一输出信号,所述第二输出 端根据所述第二输入信号输出所述第二输出信号。 在一个实施例中,所述第一输出信号与所述第一输入信号相同,所述第二输出信 号与所述第二输入信号相同。 在一个实施例中,所述第一电压信号为所述低电平信号,所述第二电压信号为所 述高电平信号,所述第一输出端根据所述第二输入信号输出所述第一输出信号,所述第二 输出端根据所述第一输入信号输出所述第二输出信号。 在一个实施例中,所述第一输出信号与所述第二输入信号相同,所述第二输出信 号与所述第一输入信号相同。 5 CN 111613171 A 说 明 书 3/7 页 根据本发明实施例的第二方面,提供一种显示装置,包括上述的信号选择电路。 根据上述实施例可知,由于控制模块的时钟信号输入端接收的时钟信号由高电平 向低电平切换时,可以拉低控制模块的控制节点的电平,也就是会拉低输出模块的控制端 的电平,当控制模块的控制节点的电平被拉低后,第一输出信号与第一输入信号和第二输 入信号中的一个相同,第二输出信号与第一输入信号和第二输入信号中的另一个相同,因 此,可以避免第一输出信号与第一输入信号和第二输入信号中的一个不相同,或者第二输 出信号与第一输入信号和第二输入信号中的另一个不相同。所以,本发明实施例提供的技 术方案,可以减小信号选择电路的信号损失。 应当理解的是,以上的一般描述和后文的细节描述仅是示例性和解释性的,并不 能限制本发明。 附图说明 此处的附图被并入说明书中并构成本说明书的一部分,示出了符合本发明的实施 例,并与说明书一起用于解释本发明的原理。 图1是根据相关技术示出的一种信号选择电路的结构示意图; 图2是根据相关技术示出的一种信号选择电路的仿真结果; 图3是根据本发明实施例示出的一种信号选择电路的结构示意图; 图4是根据本发明实施例示出的信号选择电路的一个仿真结果; 图5是根据本发明实施例示出的信号选择电路的另一个仿真结果。