技术摘要:

本申请公开了一种芯片封装方法,包括:提供第一封装体和第二封装体;其中,第一封装体包含至少一个第一封装单元,第一封装单元包括相邻设置的第一主芯片和第二主芯片、以及第一塑封层,其中,第一主芯片和第二主芯片的信号传输区相邻设置;第二封装体包含至少一个连接 全部

背景技术:

现有的基于聚合物的2D封装技术是最基本、应用最广泛的封装形式,技术成熟,成 本也较低,但是没有第三方向的连接,且线宽较大。近期发展起来的基于硅中介板的封装技 术线宽较小,形成的封装器件的电性能和热传导性能均表现优异,但是成本较高,且硅材料 脆性较高,导致封装器件的稳定性较低。因此,需要结合现有封装技术的优点,发展一种新 的封装技术,能够降低成本,且形成的封装器件的性能优异。

技术实现要素:

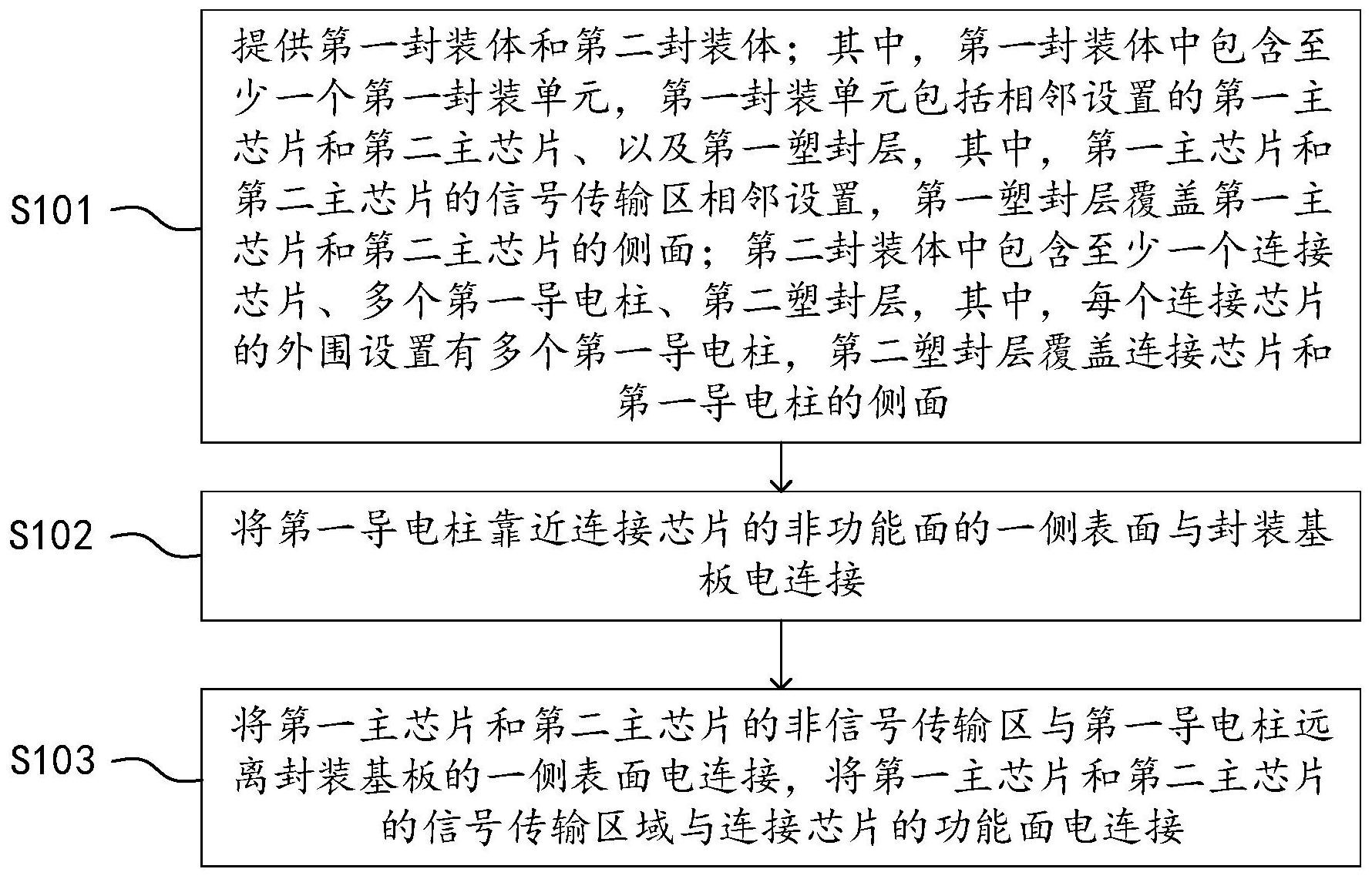

本申请主要解决的技术问题是提供一种芯片封装方法,能够降低封装成本,提高 封装器件的性能。 为解决上述技术问题,本申请采用的一个技术方案是: 提供一种芯片封装方法,包括:提供第一封装体和第二封装体;其中,所述第一封 装体中包含至少一个第一封装单元,所述第一封装单元包括相邻设置的第一主芯片和第二 主芯片、以及第一塑封层,其中,所述第一主芯片和所述第二主芯片的信号传输区相邻设 置,所述第一塑封层覆盖所述第一主芯片和所述第二主芯片的侧面;所述第二封装体中包 含至少一个连接芯片、多个第一导电柱、第二塑封层,其中,每个所述连接芯片的外围设置 有多个所述第一导电柱,所述第二塑封层覆盖所述连接芯片和所述第一导电柱的侧面;将 所述第一导电柱靠近所述连接芯片的非功能面的一侧表面与封装基板电连接;将所述第一 主芯片和所述第二主芯片的非信号传输区与所述第一导电柱远离所述封装基板的一侧表 面电连接,将所述第一主芯片和所述第二主芯片的信号传输区域与所述连接芯片的功能面 电连接。 其中,所述提供第一封装体,包括:提供可移除的第一载板,所述第一载板上定义 有至少一个区域;在每个所述区域黏贴所述第一主芯片和所述第二主芯片,且所述第一主 芯片和所述第二主芯片的功能面朝向所述第一载板,所述第一主芯片和所述第二主芯片的 信号传输区相邻设置;在所述第一载板设置有所述第一主芯片和所述第二主芯片的一侧形 成所述第一塑封层;移除所述第一载板。 或者,所述提供第一封装体,包括:提供可移除的第一载板,所述第一载板上定义 有至少一个区域;在每个所述区域黏贴所述第一主芯片和所述第二主芯片,且所述第一主 芯片和所述第二主芯片的非功能面朝向所述第一载板,所述第一主芯片和所述第二主芯片 的信号传输区相邻设置;在所述第一载板设置有所述第一主芯片和所述第二主芯片的一侧 形成所述第一塑封层,所述第一主芯片和所述第二主芯片的所述功能面从所述第一塑封层 中露出;移除所述第一载板。 其中,所述提供第二封装体,包括:提供可移除的第二载板,所述第二载板上定义 4 CN 111554624 A 说 明 书 2/9 页 有至少一个区域;在每个所述区域边缘形成多个所述第一导电柱;在每个所述区域的内侧 黏贴所述连接芯片,且所述连接芯片的所述非功能面朝向所述第二载板,所述连接芯片的 所述功能面上的焊盘位置处分别设置有第二导电柱;在所述第二载板设置有所述连接芯片 的一侧形成第二塑封层,所述第一导电柱和所述第二导电柱远离所述第二载板的一侧表面 从所述第二塑封层中露出;移除所述第二载板。 或者,所述提供第二封装体,包括:提供可移除的第二载板,所述第二载板上定义 有至少一个区域;在每个所述区域边缘形成多个所述第一导电柱;在每个所述区域的内侧 黏贴所述连接芯片,且所述连接芯片的所述功能面朝向所述第二载板,所述连接芯片的所 述功能面上的焊盘位置处分别设置有第二导电柱;在所述第二载板设置有所述连接芯片的 一侧形成第二塑封层,所述第一导电柱远离所述第二载板的一侧表面从所述第二塑封层中 露出,且所述第一导电柱的高度大于等于所述连接芯片的非功能面与所述第二载板靠近所 述第一导电柱一侧表面之间的距离;移除所述第二载板。 其中,所述将所述第一主芯片和所述第二主芯片的非信号传输区与所述第一导电 柱远离所述封装基板的一侧表面电连接,将所述第一主芯片和所述第二主芯片的信号传输 区域与所述连接芯片的功能面电连接,之后,所述第一主芯片的功能面与所述封装基板靠 近所述第二封装体的一侧表面之间的距离大于等于所述第一主芯片的功能面与所述连接 芯片的非功能面之间的距离。 其中,所述将所述第一导电柱靠近所述连接芯片的非功能面的一侧表面与封装基 板电连接,之后,包括:在所述第二封装体和所述封装基板之间形成第一底填胶。 其中,所述将所述第一主芯片和所述第二主芯片的非信号传输区与所述第一导电 柱远离所述封装基板的一侧表面电连接,将所述第一主芯片和所述第二主芯片的信号传输 区域与所述连接芯片的功能面电连接,之后,包括:在所述第一主芯片和所述第二主芯片的 功能面与所述第二封装体之间形成第二底填胶。 其中,所述第一封装体中包含至少两个所述第一封装单元,相邻所述第一封装单 元的所述第一塑封层相互连接;所述提供所述第一封装体之后,包括:切割掉相邻所述第一 封装单元之间的区域,以获得包含单个所述第一封装单元的结构。 其中,所述第二封装体中包含至少两个第二封装单元,每个所述第二封装单元包 括至少一个所述连接芯片以及位于所述连接芯片外围的多个所述第一导电柱、以及所述第 二塑封层,相邻所述第二封装单元的所述第二塑封层相互连接;所述提供所述第二封装体 之后,包括:切割掉相邻所述第二封装单元之间的区域,以获得包含单个所述第二封装单元 的结构。 本申请的有益效果是:区别于现有技术的情况,本申请提供的芯片封装方法对于 主芯片的信号传输区和非信号传输区采用不同的连接方式:对于信号传输区,采用连接芯 片连接两个主芯片,提高主芯片之间的信号传输速率,提高封装器件的性能;对于非信号传 输区,采用普通的导电柱与封装基板连接,能够降低封装成本。 附图说明 为了更清楚地说明本申请实施方式中的技术方案,下面将对实施方式描述中所需 要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本申请的一些实施方 5 CN 111554624 A 说 明 书 3/9 页 式,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获 得其他的附图。其中: 图1为本申请芯片封装方法一实施方式的流程示意图; 图2a为第一封装体一实施方式的结构示意图; 图2b为第二封装体一实施方式的结构示意图; 图3为提供第一封装体一实施方式的流程示意图; 图4a为图3中步骤S201对应的一实施方式的结构示意图; 图4b为图3中步骤S202对应的一实施方式的结构示意图; 图4c为图3中步骤S203对应的一实施方式的结构示意图; 图5为提供第一封装体另一实施方式的流程示意图; 图6a为图5中步骤S302对应的一实施方式的结构示意图; 图6b为图5中步骤S303对应的一实施方式的结构示意图; 图6c为图5中步骤S303对应的另一实施方式的结构示意图; 图6d为图5中步骤S304对应的一实施方式的结构示意图; 图7为提供第一封装体之后包括的步骤对应的一实施方式的结构示意图; 图8是第一封装体另一实施方式的结构示意图; 图9为提供第二封装体一实施方式的流程示意图; 图10a为图9中步骤S402对应的一实施方式的结构示意图; 图10b为图9中步骤S403对应的一实施方式的结构示意图; 图10c为图9中步骤S404对应的一实施方式的结构示意图; 图11为提供第二封装体另一实施方式的流程示意图; 图12a为图11中步骤S503对应的一实施方式的结构示意图; 图12b为图11中步骤S504对应的一实施方式的结构示意图; 图12c为图11中步骤S505对应的一实施方式的结构示意图; 图13是第二封装体另一实施方式的结构示意图; 图14为图1中步骤S102对应的一实施方式的结构示意图; 图15为图1中步骤S102之后包括的步骤对应的一实施方式的结构示意图; 图16为图1中步骤S103对应的一实施方式的结构示意图; 图17为图1中步骤S103之后包括的步骤对应的一实施方式的结构示意图。