技术摘要:

本发明涉及全加器、芯片和计算装置。公开了一种全加器,包括:多个初级逻辑单元以及至少一个次级逻辑单元,其中,各个初级逻辑单元的输出端至少连接到该至少一个次级逻辑单元中的第一次级逻辑单元的输入端。该多个初级逻辑单元包括:第一初级逻辑单元、第二初级逻辑单 全部

背景技术:

全加器(full-adder)是能够计算低位进位的二进制加法电路。与半加器相比,全 加器不只考虑本位计算结果是否有进位,也考虑上一位对本位的进位。多个一位全加器进 行级联可以得到多位全加器。下文中,除非特别指出,否则全加器指代一位全加器。 图1A示出了全加器的示意图。通常来说,全加器可以用具有三个输入以及两个输 出的电子电路实现。其中,在输入侧,A、B表示两个加数,Cin表示来自相邻低位的进位数。对 应地,在输出侧,SUM表示本位的和数,Cout表示向相邻高位的进位数。 图1B示出了全加器的真值表(truth table)。如图1B所示,当输入侧的A、B、Cin中具 有逻辑值“1”的数的数目是奇数时,SUM的值将是“1”。否则,SUM的值将是“0”。此外,当输入 侧的A、B、Cin中具有逻辑值“1”的数的数目超过1时,Cout的值将是“1”,否则,Cout的值将是 “0”。 全加器中典型的求和逻辑表达式和求进位逻辑表达式如下所示: Cout=AB (A B)Cin (2-1)。 其中,典型的求进位逻辑表达式(2-1)还可以表示为: 作为一种基本的逻辑电路,全加器被广泛应用于各种电子器件。对于全加器而言, 改善平衡性和减少毛刺是重要的挑战。因此存在对于新的技术的需求。

技术实现要素:

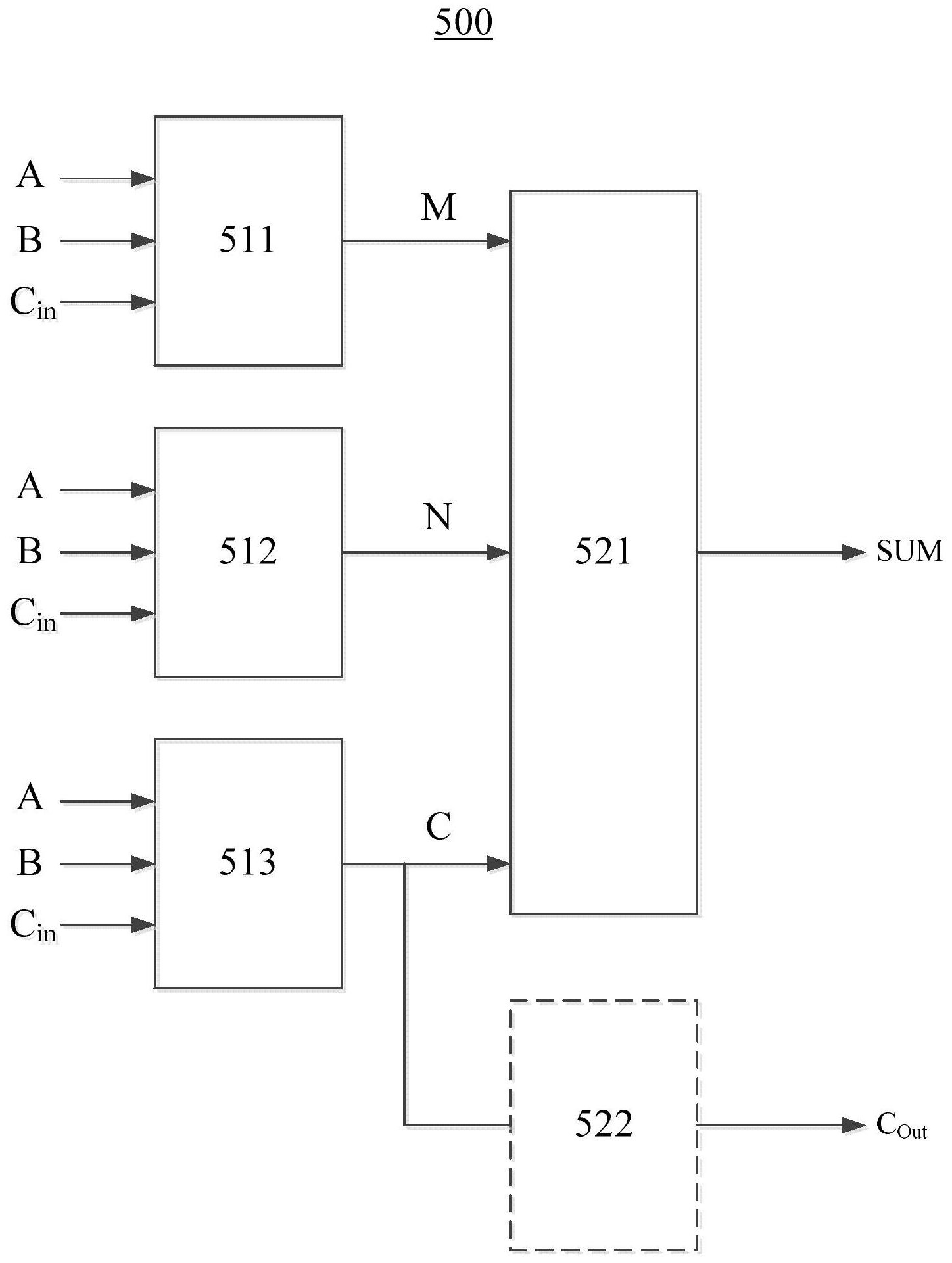

根据本公开的一个方面,提供了一种全加器,包括:多个初级逻辑单元以及至少一 个次级逻辑单元,其中,各个初级逻辑单元的输出端至少连接到该至少一个次级逻辑单元 中的第一次级逻辑单元的输入端。该多个初级逻辑单元包括:第一初级逻辑单元,被配置为 基于输入到该全加器的第一输入信号A、第二输入信号B以及进位输入信号Cin生成第一中间 信号M;第二初级逻辑单元,被配置为基于第一输入信号A、第二输入信号B以及进位输入信 号Cin生成第二中间信号N;以及第三初级逻辑单元,被配置为基于第一输入信号A、第二输入 信号B以及进位输入信号Cin生成进位相关信号C。此外,第一次级逻辑单元被配置为基于第 一中间信号M、第二中间信号N以及进位相关信号C生成该全加器的和数输出信号SUM。 根据本公开的另一个方面,提供了一种芯片,其包括如上所述的全加器。 根据本公开的又一个方面,提供了一种计算装置,其包括如上所述的芯片。 通过以下参照附图对本公开的示例性实施例的详细描述,本公开的其它特征及其 4 CN 111614350 A 说 明 书 2/11 页 优点将会变得更为清楚。 附图说明 构成说明书的一部分的附图描述了本公开的实施例,并且连同说明书一起用于解 释本公开的原理。 参照附图,根据下面的详细描述,可以更加清楚地理解本公开,其中: 图1A示出了全加器的示意图。 图1B示出了全加器的真值表。 图2示出了现有技术的全加器的一种实现方式的逻辑电路图。 图3示出了现有技术的全加器的另一种实现方式的逻辑电路图。 图4示出了现有技术的全加器的又一种实现方式的电路图。 图5示出了根据本公开的一个或多个示例性实施例的全加器的示意图。 图6示出了根据本公开的第一实施例的全加器的示意图。 图7示出了根据本公开的第二实施例的全加器的示意图。 注意,在以下说明的实施方式中,有时在不同的附图之间共同使用同一附图标记 来表示相同部分或具有相同功能的部分,而省略其重复说明。在一些情况中,使用相似的标 号和字母表示类似项,因此,一旦某一项在一个附图中被定义,则在随后的附图中不需要对 其进行进一步讨论。 为了便于理解,在附图等中所示的各结构的位置、尺寸及范围等有时不表示实际 的位置、尺寸及范围等。因此,本公开并不限于附图等所公开的位置、尺寸及范围等。