技术摘要:

本发明提供了用于限制在经受启动浪涌电流的电路路径中使用极低欧姆FET(VLOFET)的电路中的过大电流的电路(例如,升压型DC至DC变换器电路)和方法。实施方式包括电流镜驱动器电路,该电流镜驱动器电路可以耦接至VLOFET的栅极以形成限制流经VLOFET的电流的电流镜。电流镜驱 全部

背景技术:

许多电子产品,特别是电池供电的移动计算和/或通信产品(例如,笔记型计算机、 超簿计算机和平板设备)需要多个电压电平。例如,无线电发射机功率放大器可能需要相对 高的电压(例如12V或更高),而逻辑电路可能需要相当低的电压电平(例如1V–2V)。其他电 路可能需要中等的电压电平(例如2.5V、3.3V或5V)。 通常使用DC至DC变换器从DC电源产生较低或较高的DC电压。从较高电压的DC电源 产生较低电压电平的DC至DC转换器通常称为降压型变换器或降压(buck)变换器,之所以这 样称呼是因为VOUT小于VIN,因此该变换器使输入电压“降压”。产生比DC电源高的电压电平的 DC至DC变换器通常称为升压型变换器或升压(boost)变换器,因为VOUT大于VIN。 存在许多创建降压变换器和/或升压变换器的选择,包括电感性、电容性和/或线 性稳压器(包括低压降(LDO)稳压器)电路,其中,大小和效率是这些选择之间的重要差异。 例如,DC至DC变换器的各种配置(包括阶梯(Ladder)配置、Dickson配置、串并联配置、斐波 纳契(Fibonacci)配置和倍增器(Doubler)配置)依赖于开关元件的交替配置来在变换器的 端子之间传播电荷并传递能量。与电荷传播相关联的能量损耗决定变换器的效率。 某些降压型DC至DC变换器已经变得非常高效,通过优化各种电路元件和电路配 置,效率高达95%-98%。一种有助于这样的高效率的电路元件是极低欧姆(VLO)开关,其通 常是具有小于10毫欧、低至1毫欧(在某些情况下甚至更低)的总导通电阻RON的场效应晶体 管(FET)开关复合体。为了获得这样低的RON值,VLO FET开关复合体(或“VLOFET”)通常包括 数百至数千个并联耦接但作为单个单元进行切换的FET。大量器件产生相当大的有效总栅 极宽度,并且导通电阻与栅极宽度成反比。 由于其低RON电阻,VLOFET对高电流几乎不提供阻抗。在许多降压型DC至DC变换器 中,对于高启动浪涌电流,此特性通常不会构成重大问题,因为变换器配置和其他电路部件 用于限制启动浪涌电流。但是,在许多升压型DC至DC变换器电路中,使用VLOFET将会有问 题,因为变换器配置和其他部件不限制启动浪涌电流。因此,启动浪涌电流可能达到损坏或 破坏VLOFET和/或包括所连接的电源的其他电路元件(例如,电池及其相关电路)的量级。 例如,图1是现有技术的升压型DC至DC变换器电路100的示意图。所示电路包括 Dickson 3倍增升压DC至DC变换器的一个部分或单元;通常,具有针对对应开关S1-S7的互 补时钟相位的第二相似部分或单元(未示出)将耦接至共享的输出存储电容器CS的节点 102。 在所示的示例中,电路100包括3个串联连接的开关S1、S2、S3,3个串联连接的开关 S1、S2、S3串联耦接至包括2个串联连接的开关S4、S6的第一并联支路和包括2个串联连接的 开关S5、S7的第二并联支路。每个开关可以包括例如一个或更多个FET,一个或更多个FET包 含一个或更多个MOSFET;在图1中,使用NFET(开关S3-S7)和PFET(开关S1)两者。每个开关都 7 CN 111585428 A 说 明 书 2/11 页 耦接至两个互补时钟相位P1或P2之一,如每个开关S1-S7的括号所示。每个FET开关S1-S7被 示意性地示为在FET的主体与漏极之间包括对应的寄生二极管D1-D7(在本申请中,“时钟相 位”指的是诸如相位P1或P2的时钟信号,而不是指单个时钟信号的高低偏移)。 第一电容器C1耦接在第一上部对即交替相位开关S1(P1)和S2(P2)与第一支路对 即交替相位开关S4(P1)和S6(P2)之间。第二电容器C2耦接在第二上部对即交替相位开关S2 (P2)和S3(P1)与第二支路对即交替相位开关S5(P2)和S7(P1)之间。在一个实施方式中,电 容器具有相同的值,约10微法拉。通过相对小的电感器L(例如,约10nH)耦接要在节点102处 被放大3倍的输入电压VIN,其输出是电压Vx,输出电压Vx如所示出的耦接在3个串联连接的 开关S1-S3与第一并联支路即2个串联连接的开关S4、S6和第二并联支路即2个串联连接的 开关S5、S7之间。在启动时段期间,在电容器C1和C2充电之后,电感器L限制流入DC至DC变换 器电路100的电流。 在所示配置中,在启动时段之后,升压型DC至DC变换器电路100以如下绝热模式操 作:通过包括非电容性元件例如一个或更多个电感器和/或磁性元件来限制由于在交替操 作阶段期间在电容器C1与C2之间转移电荷而引起的电流变化。以虚线框104为界所示的开 关S1-S7和支持电路(例如时钟相位产生电路,未示出)可以被制造为集成电路(IC)的“片 上”部件。电容器C1、C2也可以制造在片上,但是通常使用片外电容器(如图1所示)。例如,特 别地可以在2018年3月13日提交的题为“Selectable Conversion Ratio DC-DC Converter”的美国专利申请第15/920,327号中找到Dickson变换器的配置和操作的其他细 节。例如,可以在2015年5月25日发布的题为“Partial Adiabatic Conversion”的美国专利 第9,041,459号和2018年1月30日发布的题为“DC-DC Converter with Modular Stages”的 美国专利第9,882,471号中找到关于绝热DC至DC变换电路的其他信息。 如果在经受启动浪涌电流的电路路径中不使用VLOFET,则图1所示的升压型DC至 DC变换器电路100可以良好地工作,因为存在足够的电路路径(包括常规FET)电阻来限制电 流。然而,由于这样的电路路径电阻,这样的电路将具有较低的效率。试图使用低电阻 VLOFET代替常规FET以提高效率会引起如下问题:如果在经受启动浪涌电流的电路路径中 使用VLOFET,则VLOFET基本上不会对电流呈现任何电阻。 例如,在图1所示的升压型DC至DC变换器电路100中,在电容器C1和C2充电时,在电 路启动时的相对短的时间段期间会出现启动浪涌电流。一旦电路运行,则在每个时钟周期 电容器C1和C2被预充电,并且浪涌电流停止,并且因此实现工作状态或平衡。当在VIN处施加 电压并且首次开始计时时,在时钟相位P1期间开关S7导通,使电流以从VIN到地的电流路径 流经FET开关S3、S7的体-漏二极管D3、D7(开关S3不会导通,因为没有足够高的电压来其导 通,但是二极管D3传导电流)。体-漏二极管D1-D7切换电路100中的电荷,直到有足够的电压 来通过FET启动正常受控切换。因此,二极管D1-D7启动电荷泵送操作,但是随着电压的升 高,开关S1-S7开始接管。二极管具有约0.7V的电压降,因此它们将降低效率直到开关完全 激活,这在电路100已经稳定且已达到期望的输出电压时发生。 将VLOFET用于开关S1-S7将引起非常显著的从VIN到地的浪涌电流。更具体地,在时 钟相位P1期间,在开关S7导通并且二极管D3传导电流的情况下,电容器C2的底板通过 VLOFET开关S7有效接地,并且VLOFET开关S3使得基本上不受限制且不受调节的电流经由二 极管D3流到电容器C2的顶板上。开关S1和S6会发生类似的问题,但启动浪涌电流会略低。例 8 CN 111585428 A 说 明 书 3/11 页 如,在启动期间,开关S6将导通并且二极管D3和D2将使得电荷流到电容器C1上。 图2示出了在针对所有开关使用VLOFET的图1所示类型的一个建模电路中,通过电 感器L的启动浪涌电流随时间的图表200。当输出在负载出现之前稳定时,浪涌电流在数微 秒内达到160安培,然后在大约80μS处下降到数十毫安。在此示例中,负载在大约100μS处出 现,此时工作电流增加至大约9安培。作为对这样的高浪涌电流的后果的说明,在电池供电 的电路中,上拉160安培的电流即使达数微秒也可能对电池以及电流路径中的其他电路(包 括升压型DC至DC变换器电路100)造成损坏。使用VLOFET时的这种启动浪涌高电流问题不仅 在如图1所示的升压型DC至DC变换器电路中出现,也在经受启动浪涌电流的电路路径中使 用VLOFET的其他类型的升压型DC至DC变换器电路中出现。更普遍地,在启动电流路径中使 用VLOFET的许多类型的电路中,可能都会出现高启动浪涌电流。 可以通过使电感器L变大(从而限制通过电感器的电流的变化率)或者通过在电流 路径(例如,开关S7的电流路径)的某处使用相对高电阻的FET(例如1欧姆至2欧姆)或者通 过在电流路径的某处(例如,在开关S7与地之间)包括电阻器来限制这样的启动浪涌电流。 然而,这样的方法降低了电路的效率,基本上抵消了最初通过使用VLOFET所寻求的效率益 处。例如,足够大的电感器对电路面积、高度、成本以及性能产生负面影响。此外,这样的部 件中的过程-电压-温度(PVT)变化降低了这样的电路的批量生产的平均效率,并且引起其 他的已知问题。 因此,需要用于限制在经受启动浪涌电流的电路路径中使用VLOFET的电路(例如, 升压型DC至DC变换器电路)中的启动浪涌电流的电路和方法。本发明满足这种需求并提供 附加益处。

技术实现要素:

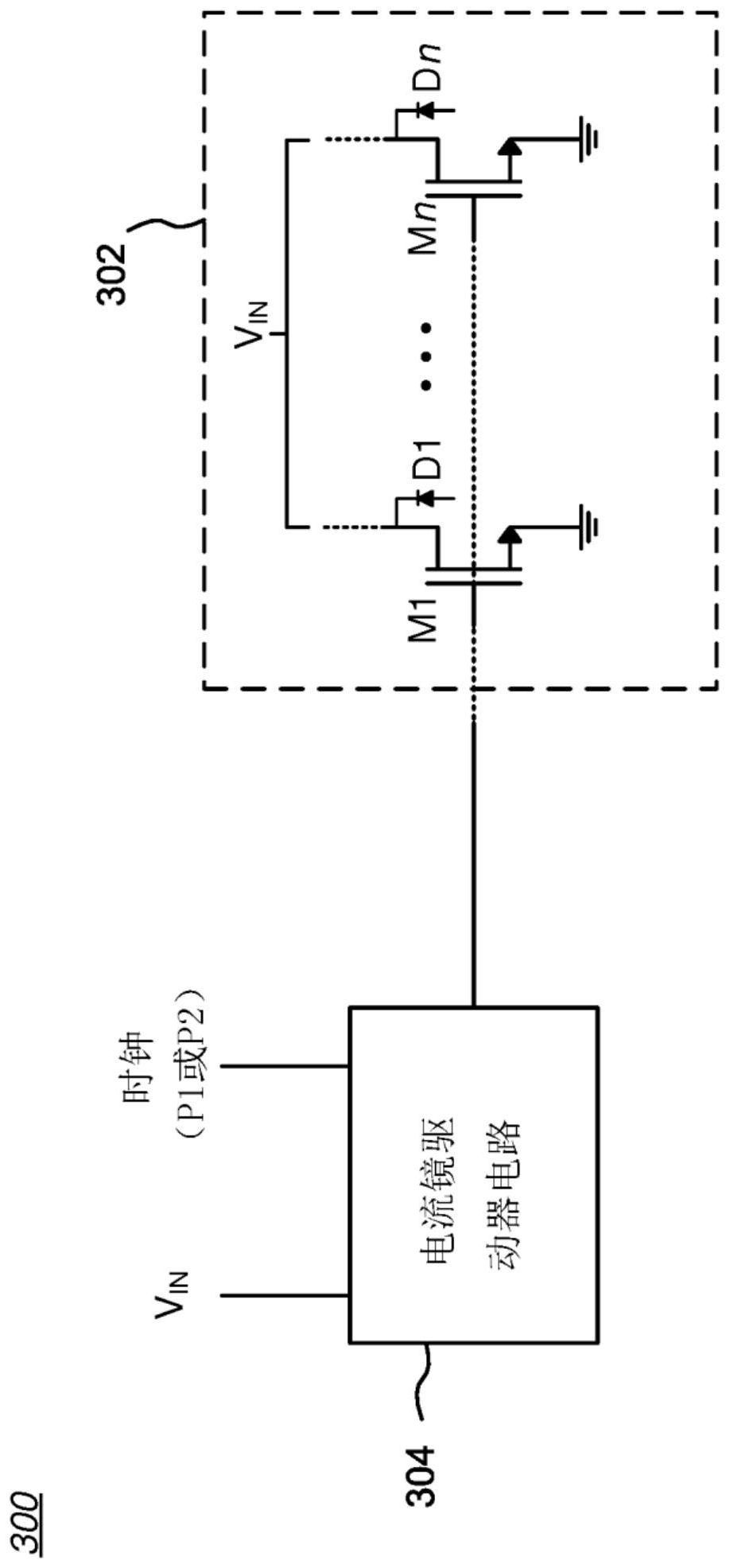

本发明包括用于限制在经受启动浪涌电流的电路路径中使用极低欧姆FET (VLOFET)的电路(例如升压型DC至DC变换器电路)中的启动浪涌电流的电路和方法。本发明 的实施方式包括电流镜驱动器电路,该电流镜驱动器电路可以耦接至VLOFET的栅极以形成 限制流经VLOFET的电流的电流镜。电流镜驱动器电路提供脉冲操作,使得耦接的VLOFET在 启动时段期间仍在截止状态与限流模式之间切换。 通过在经受启动浪涌电流的电路路径中结合使用电流镜驱动器电路和VLOFET,可 以将浪涌电流调节到可接受的水平。特别地,在经受启动浪涌电流的电路路径中不需要附 加的阻抗来限制浪涌电流,从而避免了效率损失。可以用N型FET或P型FET或者两者的组合 (特别是CMOS FET)来实现实施方式。 尽管在升压型DC至DC变换器电路的背景下描述了各种实施方式,但是本发明的实 施方式可以更普遍地在使用经受启动浪涌电流的VLOFET的电路中使用。 在附图和以下描述中阐明本发明的一个或更多个实施方式的细节。根据说明书和 附图以及根据权利要求书,本发明的其他特征、目的和优点将变得明显。 附图说明 图1是现有技术的升压型DC至DC变换器电路的示意图。 图2示出在针对所有开关使用VLOFET的图1所示类型的一个建模电路中,通过电感 9 CN 111585428 A 说 明 书 4/11 页 器L的启动浪涌电流随时间的图表200。 图3是用于将VLOFET用作开关的升压型DC至DC变换器电路(未整体示出)的浪涌电 流受限电路的示意图。 图4A是包括VLOFET和第一实施方式的电流镜驱动器电路的电流镜的示意图。 图4B是包括VLOFET和PFET实施方式的电流镜驱动器电路的电流镜的示意图。 图5是包括VLOFET和第二实施方式的电流镜驱动器电路的电流镜的示意图。 图6是包括VLOFET和第三实施方式的电流镜驱动器电路的电流镜的示意图。 图7是包括VLOFET和第四实施方式的电流镜驱动器电路的电流镜的示意图。 图8是用于限制通过VLOFET的浪涌电流的第一方法的处理流程图。 图9是用于限制通过具有至少一个VLOFET的升压型DC至DC变换器电路的浪涌电流 的第一方法的处理流程图。 在各个附图中,相似的附图标记和标记指示相似的元件。