技术摘要:

本发明公开了一种存储器装置与其编程方法,该存储器装置(memory device)包括存储单元阵列(memory cell array)和存储器控制器(memory controller)。存储单元阵列包括多个存储区块(memory blocks)。各这些存储区块包括多条字线(Word lines)。多个记忆块(memory chunks)耦 全部

背景技术:

在编程周期(programming cycle)期间,通过施加一组电压来编程存储 单元。特 别是,为将数据编程到高密度存储器装置(high-density memory device)(例如高密度 NAND快闪存储器装置(high-density NAND flash memory device)或NOR快闪存储器装置 (NOR flash memory device)),在适 当周期(suitable periods)的不同时序(timings)中 施加不同电平(levels)的电压 至存储器装置。

技术实现要素:

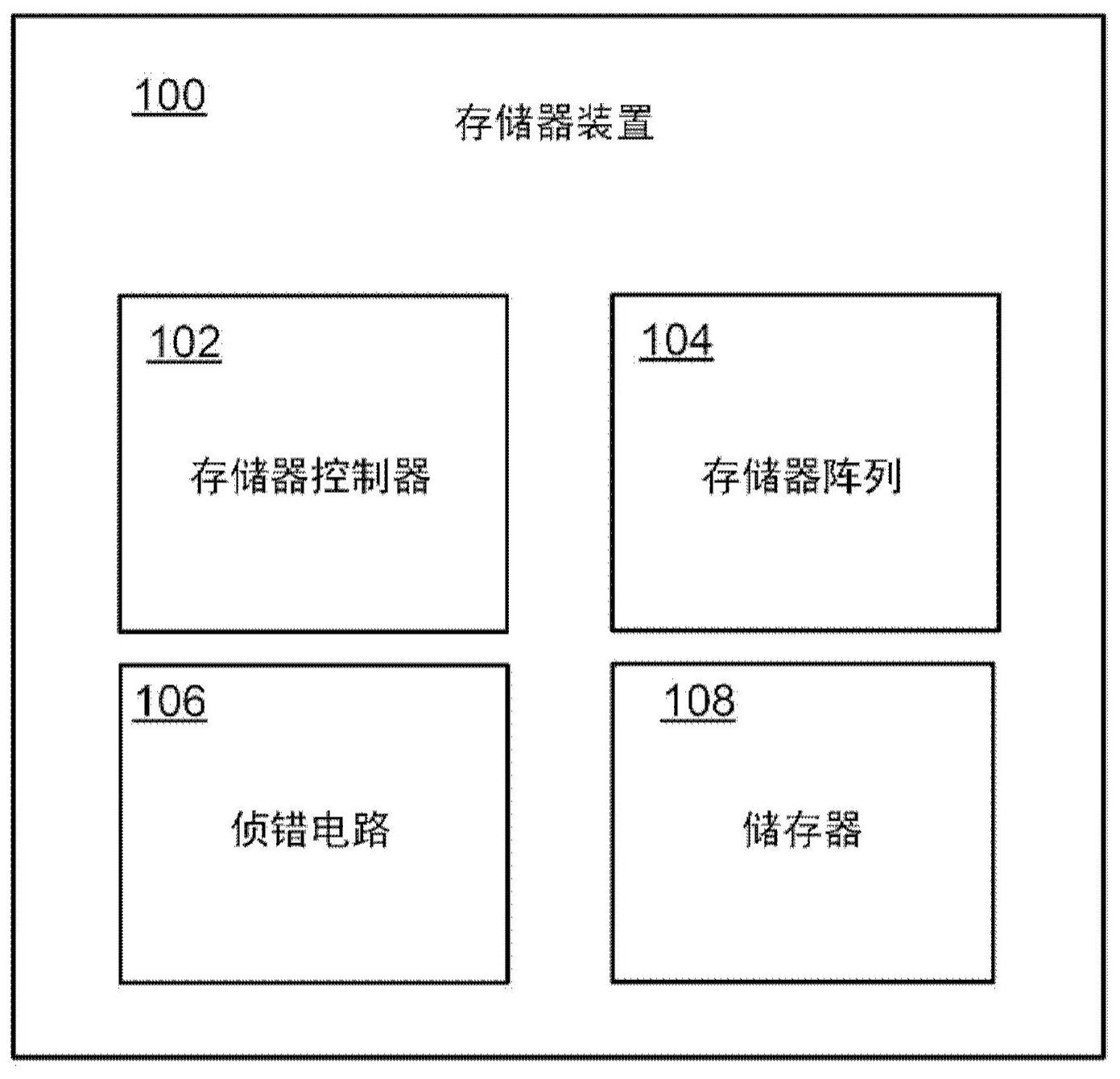

本发明描述了将数据编程(program)到存储器装置(memory device)中 的存储单 元(memory cell)的技术。特别是在存储器控制器(memory controller)将多级数据 (multi-level data)编程到存储区块(memory blocks)中 的多个记忆块(memory chunks) 的情况下,记忆块之间会发生干扰 (disturbance)。此外,在存储区块具有磨损(wear-out) 或损坏(broken)状态的 情况下,存储区块更容易有干扰问题。如果记忆块之间存在干扰, 则存储 器控制器无法正确地将数据编程到特定记忆块(particular memory chunk)。 因 此,干扰会导致存储器装置中的可靠性(reliability)问题。此外,在存储 器装置需要高可 靠性(high reliability)的情况下(例如存储器装置用于通信 设备),应该避免有干扰问 题,以确保一定程度的可靠性。 本发明技术可以减少或基本上消除发生于存储器装置中的干扰问题。 特别是,存 储器控制器获得关于存储区块错误率的数据,并确定存储器控 制器执行哪种编程操作。例 如在存储区块具有高错误率的情况下,存储器 控制器可以执行单脉冲编程操作(one-shot programming operations),以避免 干扰。另一方面,在存储区块具有低错误率的情况下, 存储器控制器可以 执行多级编程操作(multi-level programming operations),以提高 编程操作的 效率。因此,该技术可在不降低存储器装置效率的前提下来提高存储器装 置 的可靠性。 一般来说,本说明书所描述技术可以实施于存储器装置,该存储器装 置包含存储 单元阵列(memory cell array)和存储器控制器。存储单元阵列包 括多个存储区块。各存 储区块包括多条字线(word lines)。多个记忆块耦接 到这些字线的至少其中之一。存储器 控制器架构成通过执行块操作(chunk operation)将数据编程至多个记忆块的特定记忆 块,该块操作包括从多条字 线中选择特定字线(particular word line),从耦接到特定字 线的多个记忆块 中选择特定记忆块,并将编程电压施加到对应于特定记忆块的特定存储 区 块(particular memory block),以将数据编程到特定记忆块。 上述和其他实施方式可以各自选择性地(optionally)单独(alone)或组合 4 CN 111599398 A 说 明 书 2/12 页 (combination)包括以下技术特征中的一或多个。特别是,亦可有一种实施 方式包括以下 所有特征的组合。存储器控制器可以架构成依序(sequentially) 从多条字线中选择特定 字线。存储器控制器可架构成依序从多个记忆块中 选择特定记忆块。存储器控制器可架构 成随机地(randomly)从多条字线中 选择特定字线。存储器控制器可架构成随机地从多个 记忆块中选择特定记 忆块。存储器控制器可架构成通过提供12V和26V之间的编程电压,以 对特定存储区块执行块操作。 存储器装置可以包括侦错电路(error detection circuit),该侦错电路架构 成 探测发生于特定存储区块的一或多个错误,并产生错误率。当错误率满 足阈值(threshold value)时,存储器控制器可以架构成执行块操作。 存储器装置可包括多条位线(bit lines),各这些位线分别耦接到多个记 忆块的 一或多个记忆块。在块操作的单一周期(single cycle)期间,存储器 控制器可以架构成执 行块操作至这些位线的一位线中的单一记忆块(single memory chunk)。 本说明书所描述技术可以实施于存储器装置,该存储器装置包括存储 单元阵列、 侦错电路和存储器控制器。存储单元阵列包括多个存储区块。 各这些存储区块包括多条字 线。多个记忆块耦接到这些字线的至少其中之 一。侦错电路架构成探测发生于存储区块的 一或多个错误,并产生错误率。 存储器控制器架构成通过包括从侦错电路所获得的错误率 的操作执行来 将数据编程到多个记忆块的特定记忆块。当错误率满足阈值时,存储器控 制器决定特定存储区块的状态。根据特定存储区块的状态,存储器控制器 从第一编程操作 (first programming operation)和第二编程操作(second programming operation)之间 决定执行哪种编程操作,以及对特定存储区块 执行已决定的编程操作。 上述和其他实施方式可以各自选择性地单独或组合包括以下特征中 的一个或多 个。特别是一种实施方式包括以下所有特征的组合。第一编程 操作可以包括从多条字线中 选择特定字线,从耦接到特定字线的多个记忆 块中选择特定记忆块,并将编程电压施加到 特定存储区块,以将数据编程 到特定记忆块。第二编程操作可以包括选择特定存储区块中 的一或多个第 一记忆块、施加第一编程电压到特定存储区块来同时将数据编程到一或多 个第一记忆块,选择特定存储区块中的一或多个第二记忆块,以及将施加 第二编程电压到 特定存储区块来同时将数据编程到一或多个第二记忆块。 本说明书所描述技术可以用一方法来实施,在编程周期(programming cycle)期 间,由存储器控制器来编程一或多个存储器装置的存储单元。该 方法包括由存储器控制器 从存储器装置的存储单元阵列中的多个存储区 块的特定存储区块所包括的多条字线中选 择特定字线,其中多个记忆块耦 接到这些字线的至少其中之一。存储器控制器从耦接到特 定字线的多个记 忆块中选择特定记忆块。存储器控制器施加编程电压至对应于特定记忆 块 的特定存储区块,以将数据编程到特定记忆块。 上述和其他实施方式可以各自单独或组合地选择包括以下特征中的 一个或多 个。特别是一种实施方式包括以下所有特征的组合。选择特定字 线可以包括依序从多条字 线中选择特定字线。选择特定记忆块可以包括依 序从多个记忆块中选择特定记忆块。选择 特定字线可以包括随机地从多条 字线中选择特定字线。选择特定记忆块可以包括随机地 从多个记忆块中选 择特定记忆块。施加的编程电压可以包括提供12V和26V之间的编程电 压。 5 CN 111599398 A 说 明 书 3/12 页 该方法可以包括用于存储器装置中的侦错电路来探测发生于特定存 储区块的一 或多个错误。回应于所探测的一或多个错误,侦错电路可以产 生错误率。在错误率满足阈 值时,存储器控制器可以施加编程电压至对应 于特定记忆块的特定存储区块,以将数据编 程到特定记忆块。 在编程周期期间,从多个记忆块中所选择的特定记忆块可以包括在存 储器装置 的多条位线的位线中所选择的单一记忆块。各这些位线可以耦接 到多个记忆块的一或多 个记忆块。 所公开的一或多个实施方式的细节将搭配底下附图来进行说明。通过 说明书、附 图和权利要求书,本发明的其他特征、方面和优点将变得显而 易见。 附图说明 图1示例说明存储器装置。 图2绘示存储器装置中的存储单元阵列。 图3A、图3B及图3C绘示存储器装置的示例记忆块。 图4A和图4B绘示对字线的记忆块执行编程操作的示例时序图。 图5A、图5B绘示对存储区块的字线执行编程操作的示例时序图。 图6绘示用于存储区块中的特定记忆块的单脉冲编程操作的示例图。 图7A、图7B绘示对特定存储区块执行编程操作的示例图。 【附图标记说明】 100、200:存储器装置 102:存储器控制器 104、204:存储单元阵列 106:侦错电路 108:储存器 310、320、330:记忆块 311、321:第一组存储单元 313、323:第二组存储单元 325:第三组存储单元 331、333、335、337、339:屏蔽区域 332、334、336:存储单元 BL0~BL63、BLN:位线 MC0~MC63、MC11~MCML:记忆块 WL0~WL7、WLM:字线 MB:存储区块 VverifyA、VverifyB、VverifyC:验证电压 VP1~VPn:编程电压 Vbypass:读取通过电压 6 CN 111599398 A 说 明 书 4/12 页