技术摘要:

本发明公开了一种GaN基P沟道MOSFET及其制备方法,属于电子材料技术领域。本发明利用氟正离子注入氮化镓(GaN)后形成的二维空穴气(2DHG)能够在GaN表面层以下形成导电沟道的原理,将氟离子注入GaN制备出了一种GaN基P沟道MOSFET。本发明制备出的GaN基P沟道MOSFET与传统P沟 全部

背景技术:

金属-氧化物半导体场效应晶体管,简称金氧半场效晶体管(Metal-Oxide- Semiconductor Field-Effect Transistor,MOSFET)是一种可以广泛使用在模拟电路与数 字电路的场效晶体管(field-effect transistor)。 MOSFET依照其“通道”(工作载流子)的极性不同,可分为“N型”与“P型”的两种类 型,其中,P沟道MOSFET在N型衬底上有两个P 区,分别叫做源极和漏极,两极之间不通导,栅 极上加有足够的正电压(源极接地)时,栅极下的N型衬底表面呈现P型反型层,成为连接源 极和漏极的沟道。 P沟道MOSFET又分为增强型和耗尽型,其中,P沟道增强型MOSFET通过改变栅压来 改变沟道中的电子密度,从而改变沟道的电阻;P沟道耗尽型MOSFET由于N型衬底表面不加 栅压就已存在P型反型层沟道,加上适当的偏压,可使沟道的电阻增大或减小。 目前,常采用Si、Ge、GaN、GaAs等材料来制备P沟道MOSFET,在这些材料中,由于GaN 材料具有转换效率高(GaN的禁带宽度是硅的3倍,临界击穿电场是硅10倍,因此,同样额定 电压的GaN功率器件的导通电阻比硅器件低1000倍左右,大大降低了开关的导通损耗)、工 作频率高(GaN的电子渡越时间比硅低10倍,电子速度比在硅中高2倍以上,反向恢复时间基 本可以忽略,因此,GaN开关功率器件的工作频率可以比硅器件提升至少20倍,大大减小了 电路中储能元件如电容、电感的体积,从而成倍地减小设备体积,减少铜等贵重原材料消 耗,开关频率高还能减少开关损耗,进一步降低电源总的能耗)以及工作温度高(GaN的禁带 宽度高达3.4eV,本征电子浓度极低,电子很难被激发,因此,理论上GaN器件可以工作在800 ℃以上的高温)等的优点,使得GaN基P沟道MOSFET成为了学术界和工业界研究的热点。 但是,对于GaN基P沟道MOSFET器件的研究仍然存在一些难题。在工艺方面,GaN材 料的p型掺杂并不是一种很成熟的技术,国内主要通过调整压力、温度、Mg掺杂量等参数优 化体材料掺杂效果;国外主要集中在寻找新的受主元素(如Be、Zn)、使用新的结构(如超晶 格结构)、尝试新的掺杂方法(如共掺杂)等来提高p型掺杂的效果,这些方法均具有操作复 杂,重复性差等的缺点。 因此,急需找到一种性能优越的同时制备工艺简单、易操作且重复性好的GaN基P 沟道MOSFET。

技术实现要素:

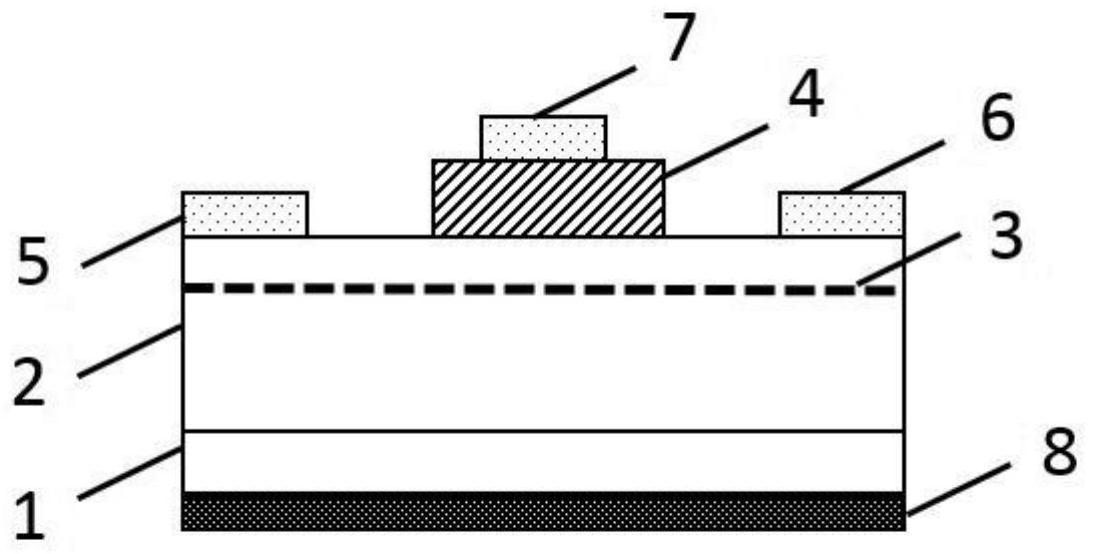

为解决上述问题,本发明提供了一种GaN基P沟道MOSFET及其制备方法。本发明利 用氟正离子注入氮化镓(GaN)后形成的二维空穴气(2DHG)能够在GaN表面层以下形成导电 沟道的原理,将氟离子注入GaN制备出了一种GaN基P沟道MOSFET。本发明制备出的GaN基P沟 道MOSFET与传统P沟道MOSFET相比,性能优越;同时,本发明采用的制备方法与传统P沟道 3 CN 111599865 A 说 明 书 2/8 页 MOSFET需要在N型衬底上利用扩散或离子注入掺杂出P型的源漏区并通过施加在栅电极的 电压使栅氧化层下的半导体反型出P沟道的制备方法相比,制备工艺简单、易操作且重复性 好,有效避免了P型掺杂。 本发明的技术方案如下: 本发明提供了一种GaN基P沟道MOSFET,所述GaN基P沟道MOSFET的GaN外延层2内部 含有通过氟离子注射形成的二维空穴气3。 在本发明的一种实施方式中,所述GaN基P沟道MOSFET包含衬底层1、GaN外延层2、 二维空穴气3、栅氧化层4、第一金属电极5、第二金属电极6、第三金属电极7以及第四金属电 极8; 所述GaN外延层2位于衬底层1上方; 所述二维空穴气3位于GaN外延层2内部; 所述栅氧化层4位于GaN外延层2上方的中心区域; 所述第一金属电极5、第二金属电极6位于栅氧化层4两侧; 所述第三金属电极7位于栅氧化层4上方的中心区域; 所述第四金属电极8位于衬底层1下方。 在本发明的一种实施方式中,所述衬底层1的材料为蓝宝石(Al2O3)、硅(Si)或碳化 硅(SiC)。 在本发明的一种实施方式中,所述衬底层1的材料为蓝宝石(Al2O3)。 在本发明的一种实施方式中,所述GaN外延层2为掺杂了施主杂质的N型GaN外延 层。 在本发明的一种实施方式中,所述二维空穴气3位于GaN外延层2内部靠近栅氧化 层4的一端。 在本发明的一种实施方式中,所述二维空穴气3的覆盖面为整个GaN外延层2的水 平横截面或所述二维空穴气3的覆盖面仅为位于第一金属电极5和第二金属电极6下方的 GaN外延层2的水平横截面。 在本发明的一种实施方式中,所述栅氧化层4的材料为二氧化硅。 在本发明的一种实施方式中,所述第一金属电极5和第二金属电极6分别于栅氧化 层4两侧对称分布且与栅氧化层4不接触或所述第一金属电极5和第二金属电极6分别于栅 氧化层4两侧对称分布且靠近栅氧化层4一侧的部分区域上方被栅氧化层4覆盖。 在本发明的一种实施方式中,第一金属电极5、第二金属电极5以及第三金属电极7 的材料均为双层金属Ni/Au。 在本发明的一种实施方式中,所述第四金属电极8的材料为四层金属Ti/Al/Ni/ Au。 在本发明的一种实施方式中,所述第一金属电极5、第二金属电极6、第三金属电极 7以及第四金属电极8的水平截面为矩形。 在本发明的一种实施方式中,所述衬底层1的厚度为20~35μm。 在本发明的一种实施方式中,所述GaN外延层2的厚度为3.5μm。 在本发明的一种实施方式中,所述二维空穴气3的厚度为2~10μm。 在本发明的一种实施方式中,所述栅氧化层4的厚度不低于2μm。 4 CN 111599865 A 说 明 书 3/8 页 在本发明的一种实施方式中,所述第一金属电极5和第二金属电极6的厚度为 300nm。 在本发明的一种实施方式中,所述第三金属电极7的厚度为300nm。 在本发明的一种实施方式中,所述第四金属电极8的厚度为300nm。 本发明提供了上述一种GaN基P沟道MOSFET的制备方法,包含如下步骤: 步骤1:制备衬底层1; 步骤2:在步骤1所得衬底层1上方外延生长一层GaN外延层2; 步骤3:在步骤2所得的GaN外延层2进行氟离子注入,形成二维空穴气3; 步骤4:在步骤3所得的含有二维空穴气3的GaN外延层2上方的中心区域形成栅氧 化层4; 步骤5:在步骤4所得的栅氧化层4两侧分别形成第一金属电极5和第二金属电极6; 步骤6:在步骤4所得的栅氧化层4上方的中心区域形成第三金属电极7; 步骤7:在步骤1所得的衬底层1下方形成第四金属电极8。 在本发明的一种实施方式中,所述步骤1中的衬底层1的材料为蓝宝石(Al2O3)、硅 (Si)或碳化硅(SiC)。 在本发明的一种实施方式中,所述步骤1中的衬底层1的材料为蓝宝石(Al2O3)。 在本发明的一种实施方式中,所述步骤2中的GaN外延层2为掺杂了施主杂质的N型 GaN外延层。 在本发明的一种实施方式中,所述步骤2为采用金属有机物化学气相沉积的方法 在衬底层1上方同质外延生长GaN外延层2。 在本发明的一种实施方式中,所述步骤2为采用氢化物气相外延(HVPE)的方法在 衬底层1上方同质外延生长GaN外延层2。 在本发明的一种实施方式中,所述步骤中3的氟离子直接在GaN外延层2的上表面 注入。 在本发明的一种实施方式中,所述步骤3中的氟离子注入区域为整个GaN外延层2 上表面或所述步骤3中的氟离子注入区域仅为位于第一金属电极5和第二金属电极6下方的 GaN外延层2的上表面。 在本发明的一种实施方式中,所述步骤4中的栅氧化层4的材料为二氧化硅。 在本发明的一种实施方式中,所述步骤5中的第一金属电极5和第二金属电极6的 材料为双层金属Ni/Au。 在本发明的一种实施方式中,所述步骤5中的第一金属电极5和第二金属电极6分 别于步骤4所得的栅氧化层4两侧对称分布且与栅氧化层4不接触或所述步骤5中的第一金 属电极5和第二金属电极6分别于步骤4所得的栅氧化层4两侧对称分布且靠近栅氧化层4一 侧的部分区域上方被栅氧化层4覆盖。 在本发明的一种实施方式中,所述步骤6中的第三金属电极7的材料为双层金属 Ni/Au。 在本发明的一种实施方式中,所述步骤7中的第四金属电极8的材料为四层金属 Ti/Al/Ni/Au。 在本发明的一种实施方式中,所述第一金属电极5、第二金属电极6、第三金属电极 5 CN 111599865 A 说 明 书 4/8 页 7以及第四金属电极8的水平截面为矩形。 在本发明的一种实施方式中,所述第一金属电极5、第二金属电极6、第三金属电极 7以及第四金属电极8可用电子束蒸发法或磁控溅射法形成。 在本发明的一种实施方式中,所述衬底层1的厚度为20~35μm。 在本发明的一种实施方式中,所述GaN外延层2的厚度为3.5μm。 在本发明的一种实施方式中,所述二维空穴气3的厚度为2~10μm。 在本发明的一种实施方式中,所述栅氧化层4的厚度不低于2μm。 在本发明的一种实施方式中,所述第一金属电极5和第二金属电极6的厚度为 300nm。 在本发明的一种实施方式中,所述第三金属电极7的厚度为300nm。 在本发明的一种实施方式中,所述第四金属电极8的厚度为300nm。 本发明提供了上述一种GaN基P沟道MOSFET的制备方法制备得到的GaN基P沟道 MOSFET。 本发明提供了上述一种GaN基P沟道MOSFET或本发明提供了上述一种GaN基P沟道 MOSFET的制备方法在集成电路方面的应用。 有益效果: (1)本发明GaN基P沟道MOSFET的沟道中的载流子浓度和迁移率等远大于传统P沟 道MOSFET,使得本发明GaN基P沟道MOSFET的功率密度可较传统P沟道MOSFET提高20倍以上、 器件体积可较传统P沟道MOSFET缩小10倍以上; (2)传统的P沟道MOSFET需要在N型衬底上利用扩散或离子注入掺杂出P型的源漏 区,并通过施加在栅电极的电压使栅氧化层下的半导体反型出P沟道;而本发明仅需使用离 子注入氟工艺取缔原有的繁琐的P阱区的制备工艺,与传统的制备方法相比,本发明的制备 方法简单、易操作且重复性好,有效避免了P型掺杂。 附图说明 图1为本发明的耗尽型GaN基P沟道MOSFET的示意图。 图2为本发明的增强型GaN基P沟道MOSFET的示意图。